先进的数字后处理技术可增强时间交错ADC系统的性能

描述

通过以双倍采样率多路复用(例如)一对转换器的输出来对多个模数转换器进行时间交错,现在已经是一个成熟的概念——布莱克和霍奇斯于 1980 年首次提出。1, 2在设计 7 位、4MHz 模数转换器 (ADC) 时,他们确定时间交错解决方案需要的芯片面积比同类的 2 MHz 模数转换器n闪存转换器设计。事实证明,这种新概念在他们的设计中具有巨大的价值,但节省空间并不是它的唯一好处。ADC的时间交错提供了一种概念上简单的方法,用于乘以现有高性能ADC的采样速率,例如14位、105 MSPS AD6645和12位、210 MSPS AD9430。在许多不同的应用中,这一概念已被用于使需要极高采样率模数转换的系统受益。

虽然标准ADC产品的速度和分辨率已经远远超过4 MHz和7位,但时间交错ADC系统(有充分的理由)并没有远远超过8位分辨率。然而,在8位性能水平下,这一概念已在测试和测量行业中得到广泛采用,特别是对于宽带数字示波器。安捷伦实验室最近开发的 20 GSPS、8 位 ADC 证明它继续在这个市场上产生影响3并被安捷伦技术无限公司采用™示波器系列。4事实上,时间交错式ADC系统在8位电平上蓬勃发展,但在需要高分辨率、宽带宽和稳定动态范围相结合的应用中,它们仍然不足。

12位和14位电平的时间交错ADC系统的主要限制因素是通道匹配的要求。提供8 dB动态范围的50位系统可以容忍0.25%的增益失配和5 ps的时钟偏斜误差。这种精度水平可以通过传统方法实现,例如匹配物理通道布局、使用通用ADC基准电压、预筛选器件和有源模拟调整,但在更高的分辨率下,要求要严格得多。到目前为止,采用更多创新匹配技术的设备尚未商业化。

本文将详细概述12位和14位时间交错ADC系统的匹配要求,讨论先进的数字后处理技术作为使能技术的理念,并介绍采用迄今为止最有前途的解决方案高级滤波器组(AFB)的器件。™),来自 V Corp Technologies, Inc.5, 6

时间交错过程概述

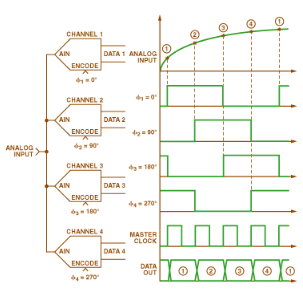

ADC系统的时间交错采用以总系统采样速率的1/m采样速率运行m ADC的概念。每个通道的时钟都处于一个相位,使系统作为一个整体能够以相等间隔的时间增量进行采样,从而创建单个A/D转换器全速采样的无缝图像。图1显示了典型四通道、时间交错ADC系统的模块图和时序图。四个ADC通道中的每一个都以系统采样速率的四分之一运行,间隔为90°。最终输出数据流是通过以正确的顺序(例如,1、2、3、4、1、2等)交错所有单独的通道数据输出来创建的。在双转换器示例中,两个ADC通道的时钟频率为整个系统采样速率的一半,并且它们彼此异相180°。

图1.四通道时间交错ADC系统。

为简单起见,本文主要关注双转换器系统,但当需要阐明关键性能差异时,将讨论四转换器系统。大多数框图、数学关系和解决方案将突出显示双通道配置。

时间交错的设计挑战

如前所述,通道间匹配对时间交错ADC系统的动态范围性能有直接影响。ADC通道之间的失配会导致动态范围下降,在FFT图中,动态范围下降表现为杂散频率分量,称为镜像杂散和失调杂散。与时间交错ADC系统相关的镜像杂散是ADC通道之间增益和相位不匹配的直接结果。增益误差和相位误差产生彼此正交的误差函数。两者都有助于在相同频率位置的镜像杂散能量。失调杂散由ADC通道之间的失调差产生。与镜像杂散不同,偏移杂散不依赖于输入信号。对于给定的失调失配,失调杂散将始终处于同一电平。对这些杂散行为的广泛研究产生了几种数学方法来表征信道匹配误差与动态范围性能之间的关系。7, 8

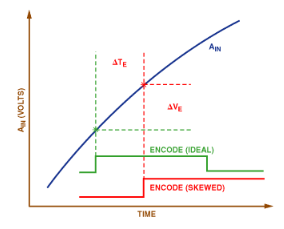

虽然这些方法彻底且非常有用,但这里使用的“误差电压”方法提供了一种简单的方法来理解这种关系,而无需深入研究复杂的数学推导。该方法基于ADI公司应用笔记AN-501中使用的相同理念9建立ADC中孔径抖动与信噪比(SNR)下降之间的关系。误差电压定义为“预期”采样电压与“实际”采样电压之差。这些差异是由一大部分误差造成的,这些误差分为三个基本类别:增益(图2)、相位(图3)和失调(图4)失配。

图2.增益不匹配导致的电压误差。

图3.由于编码/时钟偏差导致的电压误差。

图4.失调失配导致的电压误差。

在双转换器交错系统中,增益和相位失配产生的误差电压导致位于奈奎斯特减去模拟输入频率的镜像杂散。失调失配会产生误差电压,导致位于奈奎斯特的失调杂散。由于偏移杂散位于奈奎斯特频段的边缘,双通道系统的设计人员通常可以围绕该频段规划系统频率,并将精力集中在增益和相位匹配上。图5显示了双通道系统的典型FFT图。

图5.典型的双转换器交错FFT图。

在四转换器交错系统中,有三个镜像杂散和两个失调杂散。由ADC通道之间的增益和相位失配产生的镜像杂散位于(1)奈奎斯特减去模拟输入频率和(2)奈奎斯特加或减模拟输入频率的一半。偏移杂散位于奈奎斯特和奈奎斯特的一半(波段中间)。图6显示了四转换器系统的典型FFT图,说明了这五个杂散的位置。

图6.典型的四转换器交错FFT图。

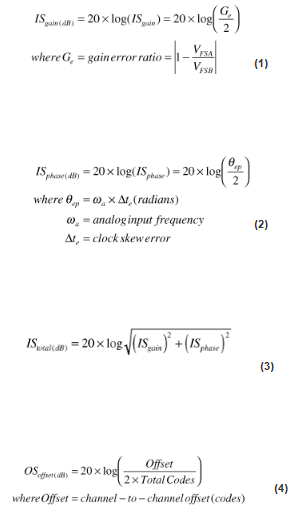

一旦知道三个失配组中每个组的误差电压,就可以使用以下公式来计算镜像和失调杂散(IS获得是阶段是总这抵消) 在单音、双转换器系统中:

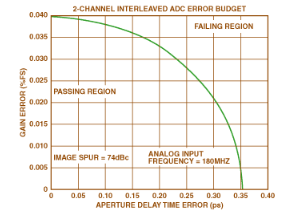

如前所述,增益和相位误差产生正交误差函数7,需要它们对图像支线的个人贡献的“和方根”组合。使用这些公式,可以制定误差预算,以确定维持给定动态范围要求所需的匹配级别。例如,在12 MHz输入频率下,74位动态范围要求为180 dBc,则需要增益匹配优于0.02%,孔径延迟匹配优于300 fs!如果增益可以完美匹配,则孔径延迟匹配可以“放松”到大约350 fs。图7显示了此12位、180 MHz示例的详细“误差预算曲线”示例。

图7.误差预算:12 位、2 通道、180MHz 输入。

表I提供了几种不同情况的匹配要求,以说明使经典的时间交错A/D转换系统在宽带宽上以12位和14位分辨率工作所需的极高精度。

表 I. 时间交错 ADC 匹配要求。

|

180 MHz 时的性能 要求 |

SFDR (dBc) |

增益 匹配 (%) |

光圈 匹配 (fs) |

| 12 位 | 74 | 0.04 | 0 |

|

12 位 |

74 |

0 | 350 |

|

12 位 |

74 |

0.02 | 300 |

|

14 位 |

86 |

0.01 |

0 |

|

14 位 |

86 |

0 | 88 |

|

14 位 |

86 |

0.005 | 77 |

宽带宽时间交错ADC系统的传统方法

传统的2通道时间交错ADC系统采用图8所示的基本配置。传统时间交错ADC系统中的第一级匹配是通过减少通道之间的物理和电气差异来实现的。例如,增益匹配通常通过使用公共基准电压和精心匹配的物理布局来控制。相位匹配是通过手动调整时钟(或模拟输入)路径的电气长度和/或通过控制时钟分配电路的电气特性(上升/下降时间、偏置电平、触发电平等)的特殊调整技术来实现的。失调匹配取决于各个ADC的失调性能。

图8.传统时间交错ADC的功能图

其中许多匹配方法都基于仔细的模拟设计和调整技术。虽然有很多优秀的想法可以满足这些苛刻的匹配要求,但其中许多都需要额外的电路来增加自己的误差源,这违背了实现精确增益和相位匹配的最初目的。这种想法的一个例子是设置两个不同时钟信号的上升和下降时间。任何能够提供这种控制水平的电路都会受到电源电压和温度对每个通道相位行为的影响。

先进的数字后处理

随着新数字信号处理技术的发展,以及廉价、高速、可配置的数字硬件平台(DSP、FPPGA、CPLD、ASIC 等)的进步,为时间交错 ADC 性能的突破开辟了道路。与传统的模拟匹配技术相比,数字后处理方法有几个优点。它们在实现方面非常灵活,其精度可以远远超过目标ADC分辨率。数字信号处理技术如何影响时间交错系统架构的概念视图如图9所示。该概念采用一组数字校准传递函数来处理每个ADC的输出数据,从而创建一组新的“校准输出”。这些数字校准传递函数可以使用各种数字滤波器配置(FIR、IIR等)来实现。它们可以像调整一个通道的增益一样简单,也可以像在宽带宽和温度范围内调整每个通道的增益、相位和失调一样复杂。

宽带宽和温度匹配是使用数字后处理技术提高时间交错ADC系统性能的最大机遇和挑战。在宽带宽和温度范围内为多个ADC通道设计数字校准传递函数所需的数学推导极其复杂且不容易获得。然而,在这一领域投入了大量的学术工作,创造了许多有趣的解决方案。其中一个解决方案被称为高级过滤器库(AFB),其为重大突破提供平台的能力非常突出。

图9.数字后处理架构示例。

高级过滤器组 (AFB)

AFB是首批商用数字后处理技术之一,对时间交错ADC系统的性能产生重大影响。通过在宽带宽和温度范围内提供精确的通道间增益、相位和失调匹配,AFB完全有能力在高速12/14位应用领域牢固地建立时间交错ADC系统。除了匹配功能外,AFB还为ADC系统提供相位线性化和增益平坦度补偿。图10显示了采用AFB的系统的基本框图表示。

图 10.空军基地基本框图。

通过使用独特的多速率FIR滤波器结构,AFB可以很容易地实现到方便的数字硬件平台中,例如FPGA或CPLD。FIR系数是使用专利方法计算的,该方法涉及从图9所示的方程开始,然后应用各种高级数学技术来求解数字校准传递函数。

AFB使时间交错ADC系统能够使用高达90%的奈奎斯特频段,并且可以配置为在转换器的任何奈奎斯特区(例如,第一、第二、第三等)工作。可以使用一组逻辑输入来选择适当的奈奎斯特区,这些逻辑输入控制所需的FIR系数。

空军基地设计示例

AD12400是ADI公司利用时间交错和AFB的全新产品系列的首款产品。其性能将用于说明将最先进的ADC设计与先进的数字后处理技术相结合可以实现的目标。图11显示了AD12400的框图及其关键电路功能。AD12400采用独特的模拟前端电路,具有400 MHz输入带宽、两个12位、200 MSPS ADC通道,以及采用高级现场可编程门阵列(FPGA)的AFB实现方案。它采用上面讨论的许多经典匹配技术以及非常低抖动的时钟分配电路进行设计。这些关键组件相结合,开发出一款 12 位、400 MSPS ADC 模块,该模块在 90% 的奈奎斯特频段和 85°C 温度范围内性能非常好。它具有 400 MHz 的模拟输入带宽。

图 11.AD12400原理框图

ADC的传递函数是在制造过程中通过宽带宽、宽温度范围测量获得的。该检定例程将ADC的测量传递函数直接馈送到AFB系数计算过程中。一旦对ADC进行了表征,并计算了所需的FIR系数,FPGA就会被编程,产品就可以开始工作了。使用AFB的特殊FIR结构和系数计算过程实现宽带宽匹配。通过使用板载数字温度传感器选择多个FIR系数组之一,可实现宽温度性能。

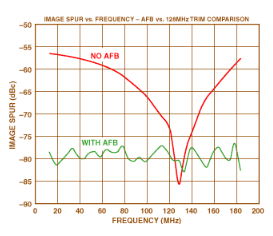

这项技术的真正影响可以在图12和图13中看到。图12显示了该系统第一个奈奎斯特区的镜像杂散性能。图12中的第一条曲线表示2通道时间交错系统的性能,该系统经过精心设计,可在布局中提供最佳匹配。该曲线中镜像杂散的行为表明,该系统是在128 MHz的模拟输入频率下手动调整的。图13的类似观察表明,手动微调温度为40°C。

图 12.在频率范围内“前后”手动调整系统的性能。

图 13.在温度范围内“前后”手动调整系统的性能。

尽管AD12400 ADC采用了精心的PCB布局、紧密匹配的前端电路、紧密匹配的时钟分配电路以及通用基准电压,但随着频率和/或温度偏离手动调整条件,动态范围会迅速下降。通过分析影响该电路的一些敏感因素,可以在任何双转换器时间交错ADC系统中预测这种快速的衰减速率。例如,典型的高性能12位ADC的增益温度系数为0.02%/°C。 在这种情况下,温度变化10°C会导致增益变化0.2%,导致镜像杂散为60 dBc(参见公式1)。仅考虑这种单一ADC温度特性,预测的镜像杂散比图3所示的30°C性能差13 dB。

相比之下,当启用AFB补偿时,这些图中显示的动态范围性能仍然稳定。事实上,在近12 MHz的带宽和190°C的温度范围内,动态范围性能超过了40位电平。 这种方法的另一个显著优势是,通过使用额外的FIR系数组,温度范围实际上可以从所示的20°C至60°C范围扩展到0°C至85°C,如AD12400所示。

结论

时间交错正逐渐成为高速ADC系统性能增强的重要趋势。先进的数字后处理方法(如AFB)为分辨率水平的严格通道匹配要求提供了一种方便的解决方案,这是以前时间交错系统无法实现的。当与现有的最佳ADC架构相结合时,先进的DSP技术(如AFB)已准备好将高速ADC系统的性能提升到一个新的水平,并促进在医疗成像、精密药物分配器(流体流量测量)、合成孔径雷达、数字波束形成通信系统和高级测试/测量系统等要求苛刻的市场中大幅改进产品和系统。该技术将在不久的将来带来许多突破,包括14位/400 MSPS和12位/800 MSPS ADC系统。

审核编辑:郭婷

-

交错ADC:揭开谜团2023-01-08 2630

-

利用CTLE和时间交错闪存ADC来降低ADC分辨率2022-07-28 2563

-

一文详细了解ADC时间交错技术2022-03-10 4385

-

浅谈模数转换器(ADC)的时间交错2021-10-11 1421

-

基于数字后处理算法的并行交替采样ADC系统2021-09-17 885

-

ADC 的时间交错特性讨论资料下载2021-03-29 711

-

基于时间交错技术实现10位/400 MSPS ADC的设计2020-09-09 1654

-

详解时间交错技术2019-07-23 1115

-

深入分析时间交错技术2018-10-24 1906

-

具有专利的运动精确图像视频后处理器2018-08-27 1659

-

示波器的带宽增强技术2018-04-03 3202

-

一文详解“时间交错技术”2018-01-17 9562

-

拓展一些关于交错ADC的观点2017-11-16 903

-

基于FPGA的视频后处理系统2015-10-30 577

全部0条评论

快来发表一下你的评论吧 !