应用工程师咨询:ADC的放大器或变压器驱动?

描述

Rob Reeder 和 Jim Caserta

在高性能模数转换器(ADC)之前设计输入配置或“前端”对于实现所需的系统性能至关重要。优化整体设计取决于许多因素,包括应用的性质、系统分区和ADC架构。以下问题和答案重点介绍了影响使用放大器和变压器电路的ADC前端设计的重要实际考虑因素。

Q. 放大器和变压器之间的根本区别是什么?

A。放大器是有源元件,而变压器是无源元件。与所有有源元件一样,放大器会消耗功率并增加噪声;变压器不消耗电力,增加的噪音可以忽略不计。两者都有动态效应需要处理。

问。 为什么要使用放大器?

A。放大器性能的限制比变压器少。如果必须保持直流电平,则必须使用放大器,因为变压器本质上是交流耦合器件。另一方面,变压器在需要时提供电流隔离。放大器更容易提供增益,因为它们的输出阻抗基本上与增益无关。另一方面,变压器的输出阻抗随电压增益的平方而增加,这取决于匝数比。放大器在通带内提供更平坦的响应,没有由于变压器中的寄生相互作用而产生的纹波。

问。放大器通常会增加多少噪声,我能做些什么来降低噪声?

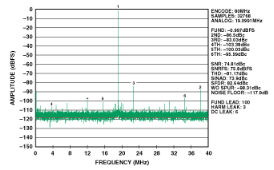

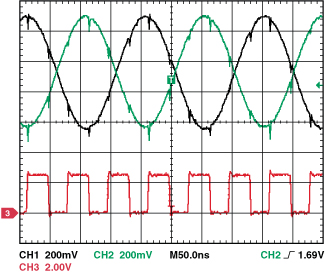

一个。例如,可以考虑的典型放大器ADA4937在配置为G = 1时,高频下的输出噪声频谱密度为6 nV/rtHz,而10 MSPS AD80-9446 ADC的输入噪声频谱密度为80 nV/rtHz。这里的问题是,放大器的噪声带宽相当于ADC的全带宽,约为500 MHz,而ADC噪声则折叠到一个奈奎斯特区(40 MHz)。如果没有滤波器,放大器的积分噪声为155 μV rms,ADC的积分噪声为90 μV rms。从理论上讲,这会将整个系统的SNR(信噪比)降低6 dB。为了通过实验证实这一点,ADA4937驱动AD9446-80时测得的SNR为76 dBFS,本底噪声为–118 dB(图1)。使用变压器驱动时,SNR 为 82 dBFS。因此,驱动放大器将SNR降低了6 dB。

图1.ADA4937放大器,以9446 MSPS驱动AD80-80 ADC,不带噪声滤波器。

为了更好地利用ADC的SNR,在放大器和ADC之间插入了一个滤波器。使用100 MHz 2极点滤波器时,放大器的积分噪声变为71 μV rms,仅将ADC的SNR降低3 dB。使用2极点滤波器可将图1电路的SNR性能提高到79 dBFS,本底噪声为-121 dB,如图2a所示。2 极点滤波器由 24 欧姆电阻和 30 nH 电感器构成,与放大器的每个输出串联,以及一个 47pF 差分连接的电容器(图 2b)。

图 2b.ADA4937放大器使用9446极点噪声滤波器以80 MSPS驱动AD80-2 ADC的原理图。

问。 高速放大器和ADC的功耗如何比较?

A。 这取决于所使用的放大器和ADC。功耗相似的两个典型放大器是AD8352,37 V (5 mW)时功耗为185 mA,ADA4937在40 V (5 mW)时功耗为200 mA。通过使用 3.3V 电源,总功耗可降低约 16/80,性能略有下降。ADC的功耗更加多样化,具体取决于分辨率和速度。9446位、80 MSPS AD2-4功耗为14.125 W,9246位、125 MSPS AD415-12功耗为20 mW,9235位、20 MSPS AD95-<>功耗仅为<> mW。

问。什么时候需要使用变压器?

A。与放大器相比,变压器在信号频率非常高时具有最大的性能优势,并且当ADC输入端不能容忍大量额外噪声时。

问。 变压器和放大器在提供增益时有何不同?

A。 主要区别在于它们呈现给ADC输入的阻抗,这直接影响系统带宽。变压器的输入阻抗和输出阻抗与匝数比的平方有关,而放大器的输入和输出阻抗基本上与增益无关。

例如,当从2欧姆的源阻抗使用G = 50变压器时,变压器次级侧的阻抗为200欧姆。AD9246 ADC的差分输入电容为4 pF,与200 Ω变压器阻抗相结合,可将ADC的–3 dB带宽从650 MHz降低至200 MHz。 通常需要额外的串联电阻和差分电容来提高性能并减少转换器的反冲,这会进一步限制–3 dB带宽。 可能达到 100 MHz。

使用低输出阻抗放大器(如ADA4937)时,源阻抗非常低,通常小于5 Ω。25 欧姆瞬态限制电阻可与每个 ADC 输入串联使用;对于AD9246,ADC的全650 MHz模拟输入带宽是可用的。

到目前为止,讨论的是关于–3 dB带宽。当需要更紧密的平坦度时,例如在0极系统中为5.1 dB,−3 dB带宽需要宽约3×。对于单极0.1 dB平坦度,该比率增加到6.5×。如果在高达0 MHz时需要5.150 dB平坦度,则需要大于3 MHz的–450 dB带宽,这很难通过G = 2变压器实现,但使用低输出阻抗放大器则很简单。

问。 选择变压器或放大器来驱动ADC时需要考虑哪些因素?

A。它们可以归结为六个参数 — 如下表所述:

| 参数 | 通常的偏好 |

| 带宽 | 变换 |

| 获得 | 放大器 |

| 通带平坦度 | 放大器 |

| 功率要求 | 变换 |

| 噪声 | 变换 |

| 直流与交流耦合 |

放大器(直流电平保持) 变压器(直流隔离) |

关键参数冲突的应用需要额外的分析和权衡。

问。此分析中有哪些考虑因素?

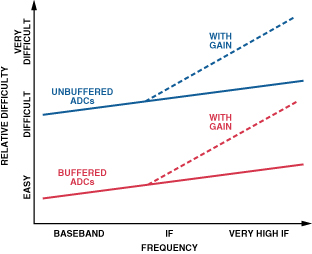

A。首先必须了解为给定ADC设计前端的难度。首先,ADC是内部缓冲,还是无缓冲(例如,开关电容类型)?当然,在任何一种情况下,难度级别都会随着频率的增加而增加。但开关电容类型对设计人员来说更难处理。

如果需要增益来充分利用ADC的输入范围,则随着所需增益(匝数比)的增加,原本可能有利于变压器的应用变得更加困难。

当然,难度会随着频率的增加而增加。如图100所示,与使用无缓冲ADC的低信号电平高中频设计相比,使用缓冲ADC设计低于3 MHz的中频系统相对简单。由于如此多的参数朝着不同的方向拉动,在更改和评估组件时,权衡有时很困难,而且经常令人费解。

图3.频率与相对难度。

在设计进行时,使用电子表格或表格来保持所有参数的直线可能会很有用。没有满足所有情况的最佳设计;它将受可用组件和应用规格的约束。

问。 好吧,设计可能很困难。现在,有关系统参数的一些详细信息如何?

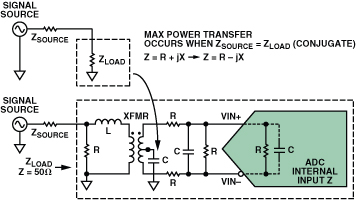

A。首先,在设计ADC前端时,必须考虑所有因素!每个组件都应被视为前一级载荷的一部分;并且最大功率传输发生在 Z源= 共轭物 Z负荷(图4)。

图4.最大功率传输。

现在来看设计参数:

输入阻抗是设计的特性阻抗。在大多数情况下,它是 50 欧姆,但可能需要不同的值。变压器是很好的跨阻器件。它允许用户在需要时在不同的特性阻抗之间进行耦合,并完全平衡系统的整体负载。在放大器电路中,阻抗被指定为输入和输出特性,可以设计为不会像变压器那样随频率变化。

电压驻波比(VSWR)是一个无量纲参数,可用于了解在目标带宽上有多少功率反射到负载中。它是一项重要措施,它决定了实现ADC满量程输入所需的输入驱动电平。

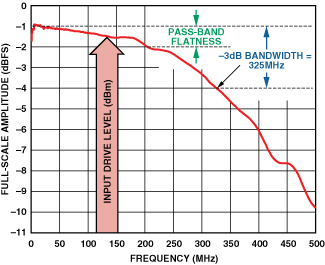

带宽是系统中使用的频率范围。它们可以是窄的或宽的,在基带,或覆盖多个奈奎斯特区。它们的频率限制通常为 –3 dB 点。

通带平坦度(也称为增益平坦度)指定了指定带宽内响应随频率变化的(正负)变化量。它可能是涟漪或简单的单调滚降,就像巴特沃兹滤波器特性一样。无论如何,通带平坦度通常要求小于或等于1 dB,这对于设置整体系统增益至关重要。

输入驱动电平由特定应用所需的系统增益决定。它与带宽规格密切相关,取决于所选的前端组件,例如滤波器和放大器/变压器;它们的特性可能导致驱动器级别要求成为最难维护的参数之一。

图5.定义带宽、通带平坦度和输入驱动电平。

信噪比(SNR)是满量程信号的均方根值与给定带宽内所有噪声分量的和方根的对数比,但不包括失真分量。就前端而言,SNR随着带宽、抖动和增益的增加而降低(在高增益下,在低增益下可能可以忽略不计的放大器噪声成分可能会变得很大)。

无杂散动态范围(SFDR)是均方根满量程值与最大杂散频谱分量的均方根值之比。前端杂散的两个主要因素是放大器的非线性(或变压器缺乏完美平衡),这主要产生二次谐波失真,以及输入失配及其由增益放大(在较高增益下,匹配更困难,寄生非线性被放大),通常被视为三次谐波失真。

问。 关于变压器,需要了解哪些重要信息?

A。变压器具有许多不同的特性,例如电压增益和阻抗比、带宽和插入损耗、幅度和相位不平衡以及回波损耗。其他要求可能包括额定功率、配置类型(如巴伦或变压器)和中心抽头选项。

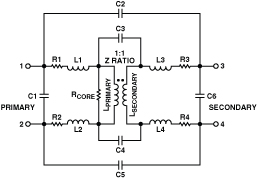

使用变压器进行设计并不总是那么简单。例如,变压器特性随频率变化,从而使模型复杂化。ADC应用变压器建模的起点示例如图6所示。每个参数都取决于所选的变压器。建议您联系变压器制造商以获取型号(如果有)。

图6.变压器模型。

变压器的特点包括:

匝数比是次级电压与初级电压的比值。

流动比率与匝数比率成反比。

阻抗比是匝数比的平方。

理想情况下,信号增益等于匝数比。虽然电压增益本质上是无噪声的,但还有其他考虑因素,将在下面讨论。

变压器可以简单地视为具有标称增益的通带滤波器。插入损耗(滤波器在指定频率范围内的损耗)是数据手册中最常见的测量规格,但还有其他考虑因素。

回波损耗是变压器初级端接所见次级端接有效阻抗不匹配的量度。例如,如果次级与初级匝数之比的平方为2:1,则当次级端接50欧姆时,预计100欧姆的阻抗会反射到初级端上。但是,这种关系并不准确;例如,初级端的反射阻抗随频率变化。通常,随着阻抗比的上升,回波损耗的可变性也会增加。

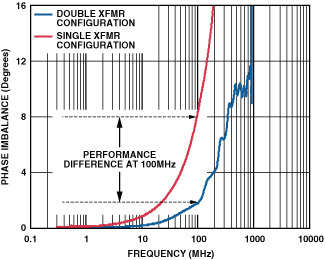

在考虑变压器时,幅度和相位不平衡是关键性能特征。这两个规格使设计人员了解当设计需要非常高(高于100 MHz)的IF频率时,预期的非线性程度。随着频率的增加,变压器的非线性度也随之增加,通常以相位不平衡为主,这转化为偶数阶失真(主要是2德·-谐波)。

图7显示了单变压器和双变压器配置的典型相位不平衡与频率的关系。

图7.单变压器和双变压器配置的变压器相位不平衡。

请记住,并非所有制造商都以相同的方式指定所有变压器,具有明显相似规格的变压器在相同情况下的性能可能不同。为您的设计选择变压器的最佳方法是收集和了解所考虑的所有变压器的规格,并索取制造商数据表中未说明的任何关键数据项。或者,或者另外,使用网络分析仪自己测量它们的性能可能是有用的。

问。 哪些参数在选择放大器时很重要?

A。使用放大器而不是变压器的主要原因是获得更好的通带平坦度。如果此规格对您的设计至关重要,则放大器应产生较小的可变性,通常在频率范围内±0.1 dB。变压器具有块状响应,当必须使用它们并且平坦度是一个问题时,需要“微调”。

驱动能力是放大器的另一个优势。变压器不是为在印刷电路板上驱动长走线而设计的。它们旨在直接连接到ADC。如果系统要求要求“驱动器/耦合器”需要远离ADC,或者位于不同的电路板上,则强烈建议使用放大器。

直流耦合也可能是使用放大器的一个原因,因为变压器本质上是交流耦合的。一些高频放大器可以一直耦合到直流的频率,如果这部分频谱在应用中很重要。需要考虑的典型放大器包括AD8138和ADA4937。

放大器还可以提供动态隔离(大约30 dB至40 dB的反向隔离),以抑制无缓冲ADC输入中电流瞬变产生的反冲毛刺。

如果设计需要宽带增益,则放大器比变压器更好地匹配ADC的模拟输入。

另一个权衡是带宽与噪声。对于频率大于150 MHz的设计,变压器将更好地保持SNR和SFDR。但是,在第一或第二奈奎斯特区内,可以使用变压器或放大器。

问。驱动高性能ADC的首选ADI放大器是什么?

A。少数放大器最适合高速ADC前端。其中包括AD8138和AD8139;AD8350、AD8351和AD8352; 以及ADA4937和ADA4938。AD8139通常用于基带设计,即目标输入频率小于50 MHz的基带设计。对于中频较高的设计,通常使用AD8352。该放大器在更宽的频率频带(高达 200MHz 区域)上表现出良好的噪声和杂散抑制。ADA4937可用于高达150 MHz的频率;它的主要优势在于采用ADC的直流耦合应用,因为它可以处理各种共模输出电压。

问。 我可能使用的ADC有哪些重要特性?

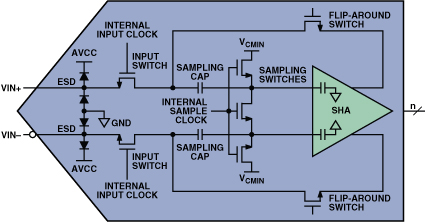

一个。广受欢迎的CMOS开关电容ADC没有内部输入缓冲器,因此其功耗远低于缓冲型。外部电源直接连接到 ADC 的内部开关电容采样保持 (SHA) 电路(图 8)。这就带来了两个问题。首先,输入阻抗随时间以及模式在采样和保持之间切换而变化。其次,注入采样电容器的电荷反射回信号源;这可能会导致驱动电路中无源滤波器的建立延迟。

图8.开关电容ADC输入级框图

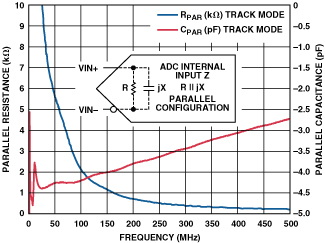

将外部网络与ADC跟踪模式阻抗相匹配非常重要,如图9所示。如您所见,输入阻抗(蓝线)的实部(阻性)在较低频率(基带)下非常高(在几千欧姆范围内),并且在2 MHz以上滚降到小于100 kohm。

输入阻抗的虚部或容性部分红线开始时为相当高的容性负载,在高频下逐渐减小至约3 pF(右手标度)。

匹配这种输入结构是一个相当具有挑战性的设计问题,尤其是在频率大于100 MHz时。

图9.轨道模式下开关电容ADC的典型输入阻抗图。

图10和图11中的波形说明了差分信号的优势。乍一看,图10中的单个单端ADC输入波形看起来相当糟糕。但是,图11表明,单端迹线的损坏几乎纯粹是共模效应。

图 10.开关电容ADC输入相对于时钟边沿的单端测量。

图 11.开关电容ADC输入相对于时钟边沿的差分测量。

以差分方式观察ADC输入(图11),可以看到输入信号要干净得多。与时钟相关的“损坏”故障消失了。差分信号固有的共模抑制可抵消共模噪声,无论是来自电源、数字源还是电荷注入。

缓冲输入ADC更易于理解和使用。输入源以固定阻抗端接。它由晶体管级缓冲,晶体管级以低阻抗驱动转换过程,因此电荷注入尖峰和开关瞬变显著降低。与开关电容ADC不同,输入端接在ADC的模拟输入频率范围内变化很小,因此选择合适的驱动电路要容易得多。缓冲器专门设计为非常线性且具有低噪声;它唯一的缺点是其功耗会导致ADC整体功耗更高。

问。 你能给我看一些变压器和放大器驱动电路的例子吗?

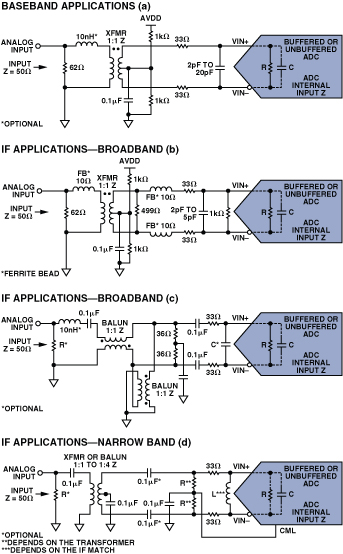

A。图12显示了使用变压器的ADC输入配置的四个示例。

在基带应用(a)中,输入阻抗要高得多,因此匹配比更高频率下的匹配更直接,而且不像匹配那样重要。通常,小值串联电阻器足以用差分连接的电容器来抑制电荷注入。这种简单的滤波器可衰减宽带噪声,实现最佳性能。

为了在宽带应用(b)中获得匹配良好的输入,请尝试使输入的实际(电阻)成分占主导地位。最小化电感或铁氧体磁珠与模拟前端并联或串联的电容项。这可以产生良好的带宽,改善增益平坦度,并提供更好的性能(SFDR),如使用AD92xx开关电容ADC系列所示。

对于缓冲高中频应用(c),图中显示了双巴伦配置,其滤波器类似于基带配置。这允许高达300 MHz的输入,并提供良好的平衡,以最大限度地减少偶数阶失真。

对于窄带(谐振)应用(d),拓扑结构类似于宽带。但是,匹配是分流而不是串联的,以将带宽缩小到指定的频率。

图 12.采用变压器驱动的ADC前端设计。

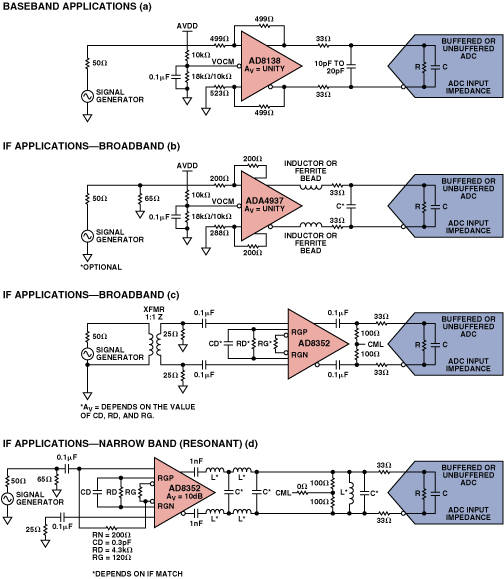

在基带应用中使用带有缓冲或无缓冲ADC的放大器时,设计相当简单(图13)。只需确保放大器的共模电压与ADC共享,并使用简单的低通滤波器来消除不需要的宽带噪声(a)。对于中频应用(b和c),匹配网络与基带中的匹配网络基本相似,但通常具有较浅的滚降。如果需要,可以在放大器的输出端使用电感器或铁氧体磁珠,以帮助扩展带宽。然而,这并不总是必要的,因为与变压器的特性相比,放大器的特性更不容易在目标频带上发生变化。对于窄带或谐振应用(d),滤波器与放大器的输出阻抗匹配,以抵消ADC的输入电容。通常使用多极点滤波器来消除感兴趣频率区域之外的宽带噪声。

图 13.具有放大器驱动的ADC前端设计。

审核编辑:郭婷

-

仪表放大器应用工程师指南 第2版2023-11-18 914

-

应用工程师咨询:宽带A/D转换器前端设计注意事项II2023-02-07 1684

-

AN-360:询问应用工程师-6:运算放大器问题2021-04-27 808

-

简单介绍ADC芯片前端输入使用放大器和变压器各自的优势2021-03-26 7079

-

分享仪表放大器应用工程师指南!2019-08-30 1822

-

关于宽带ADC前端设计考虑:用放大器还是用变压器驱动ADC?2018-12-14 3288

-

适合你的是放大器还是平衡-非平衡变压器2018-09-12 3453

-

仪表放大器应用工程师指南108页2.9Mpdf2017-03-20 1347

-

仪表放大器应用工程师指南2016-03-31 984

-

减少变压器对放大器的干扰技术分析2009-12-11 558

-

仪表放大器应用工程师指南(第2版)2009-08-08 983

-

差分放大器驱动高速ADC的电路2009-03-22 2853

全部0条评论

快来发表一下你的评论吧 !