利用同步反相SEPIC拓扑结构实现高效率降压/升压转换器

描述

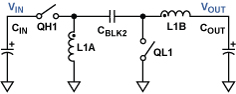

许多市场对高效率同相 DC-DC 转换器的需求都在不断增长,这些转换器能以降压或升压模式工作,即可以将输入电压降低或提高至所需的稳定电压,并且具有最低的成本和最少的元件数量。反相 SEPIC(单端初级电感转换器)也称为 Zeta 转换器,具有许多支持此功能的特性(图 1)。对其工作原理及利用双通道同步开关控制器ADP1877的实施方案进行分析,可以了解其在本 应用中的有用特性。

图1. 反相 SEPIC 拓扑结构

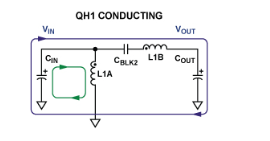

初级开关QH1 和次级开关QL1 反相工作。在导通时间内,QH1接通,QL1 断开。电流沿两条路径流动,如图 2 所示。第一条路径是从输入端经过初级开关、能量传输电容(CBLK2)、输出电感(L1B)和负载,最终通过地流回输入端。第二条路径是从输入端经过初级开关、地基准电感(L1A)和地流回输入端。

图 2. 电流流向图;QH1 闭合,QL1 断开。

在关断期间,开关位置刚好相反。QL1 接通,QH1 断开。输入电容(CIN)断开,但电流继续经过电感沿两条路径流动,如图 3所示。第一条路径是从输出电感经过负载、地和次级开关流回输出电感。第二条路径是从地基准电感经过能量传输电容、次级开关流回地基准电感。

图 3. 能量传输图;QL1 闭合,QH1 断开。

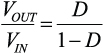

应用电感伏秒平衡原理和电容电荷平衡原理,可以求得方程式 1所规定的均衡直流转换比,其中 D 为转换器的占空比(一个周期的导通时间部分)。

|

(1) |

上式表明:如果占空比大于 0.5,输出端将获得较高的调节电压(升压);如果占空比小于 0.5,调节电压会较低(降压)。此外还可分析得到其它相关结果:在无损系统中,能量传输电容(CBLK2)上的稳态电压等于VOUT;流经输出电感(L1B)的直流电流值等于IOUT;流经地基准电感(L1A)的直流电流值等于IOUT ×VOUT/VIN。该能量传输电容还能提供VIN至VOUT的隔直。当存在输出短路风险时,此特性很有用。

分析还显示,反相 SEPIC 中的输出电流是连续的,对于给定输出电容阻抗,会产生较低的峰峰值输出电压纹波。这就允许使用较小、较便宜的输出电容;相比之下,在非连续输出电流拓扑结构中,为了达到同样的纹波要求,需要使用较大且昂贵的电容。

通常,次级开关(QL1)是一个单向功率二极管,它会限制这种拓扑结构的峰值效率。然而,利用ADI公司双通道同步开关控制器ADP1877(见附录)的一个通道,并采用双向MOSFET作为次级开关,可以设计一个"完全同步配置"的反相SEPIC。这样,峰值效率将大大提高,同时可以降低输出电流大于 1 A的转换器尺寸和成本。

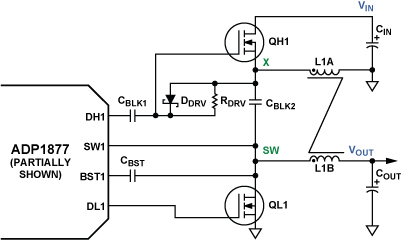

图 4 显示完全同步反相SEPIC配置的功率级,它利用ADP1877 实现,只需要三个小型、廉价的额外器件(CBLK1、DDRV和RDRV),其功耗可以忽略不计。

图 4. 同步反相 SEPIC 的功率级,利用 ADP1877 的通道 1 实现

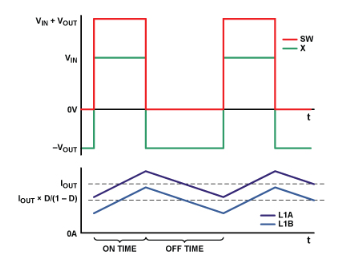

反相SEPIC的理想稳态波形如图 5 所示。通道 1 开关节点SW1(见附录图A)在VIN + VOUT(导通时间内)和 0 V(关断时间内)之间切换。将电荷泵电容CBST连接到SW1,以便在导通时间内将约为VIN + VOUT + 5 V的电压施加于高端内部驱动器的自举上电轨(BST1 引脚)和高端驱动器的输出(DH1 引脚),从而增强初级浮空N沟道MOSFET开关QH1。箝位二极管DDRV确保稳态输出期间CBLK1上的电压约为VOUT + VFWD(DDRV),该电压参考ADP1877的DH1 引脚到QH1 栅极的电压。在关断时间内,当X节点电压约为–VOUT时,CBLK1上的电压阻止初级开关产生高于其阈值的栅极-源极电压。

图 5. 同步反相 SEPIC 的理想波形(忽略死区)

ADP1877 具有脉冲跳跃模式,使能时,可以降低开关速率,只向输出端提供足以保持输出电压稳定的能量,从而提高小负载时的效率,大大降低栅极电荷和开关损耗。在同步反相 SEPIC 和同步降压拓扑结构中均可以使能此模式。图 4 所示 DC-DC 转换电路只需要双通道 ADP1877 的一个通道,因此另一通道可以用于任一种拓扑结构。

电感耦合和能量传输电容

图 4 中,功率电感 L1A 和 L1B 显示为彼此耦合。在这种拓扑结构中,耦合电感的目的是减少输出电压和电感电流的纹波,并且提高最大可能闭环带宽,下一部分将对此加以说明。

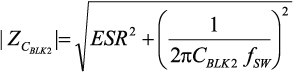

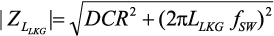

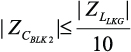

虽然这些电感互相耦合,但并不希望耦合太紧,以至于将一个绕组的大量能量通过铁芯传输至另一个绕组。为了避免这一点,必须求得耦合电感的泄漏电感(LLKG),并选择适当的能量传输电容(CBLK2),使得其复数阻抗的幅值为泄漏电感与单个绕组电阻(DCR)的复串联阻抗的 1/10,如方程式 2、3、4 所示。按照这一关系设计电路,可使耦合铁芯所传输的能量降至最低。泄漏电感可以根据耦合电感数据手册中提供的耦合系数计算。

| (2) | ||

|

(3) | |

|

(4) |

匝数比最好为 1:1,因为对于给定水平的输出电压纹波,此时各绕组只需要分立电感所需电感的一半1。可以使用 1:1 以外的匝数比,但其结果将无法用本文中的方程式准确描述。

小信号分析和环路补偿

反相 SEPIC 转换器的完整小信号分析超出了本文的范围,不过,如果遵照下述原则,完整分析将更具学术意义。

首先必须计算谐振频率(fRES)时的许多复数阻抗交互,以便求得目标交越频率的上限。当电感解耦时,此频率降低,导致最大可能闭环带宽显著降低。

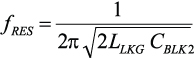

|

(5) |

在此频率时,可能有 300°或更大的"高Q"相位迟滞。为了避免转换器在整个负载范围内相位裕量偏小的问题,目标交越频率(fUNITY)应为fRES的 1/10。此谐振的阻尼主要取决于输出负载电阻和耦合电感的直流电阻。在较小程度上,阻尼还取决于能量传输电容的等效串联电阻(ESR)和功率MOSFET(QHl和QL1)的导通电阻。因此,当输出负载电阻改变时,闭环传递函数的特征在该频率时发生明显变化也不足为奇。

耦合系数通常不是一个能够精确控制的参数,因此应将目标交越频率设置为比fRES低 10 倍的值(假设fRES小于开关频率fSW)。当fUNITY设置适当时,可以使用标准"II型"补偿——两个极点和一个零点。

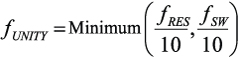

| (6) |

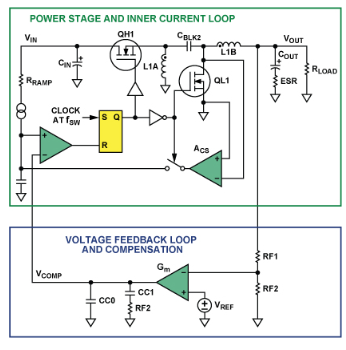

图6 显示同步反相SEPIC 降压/升压拓扑结构中ADP1877反馈环路的等效电路。上框包含功率级和电流环路,下框包含电压反馈环路和补偿电路。

图 6. 同步反相 SEPIC 拓扑结构中 ADP1877 具有内部电流检测 I环路的功率级和补偿方案

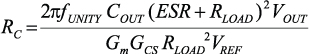

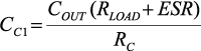

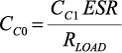

下框中的补偿元件值可以通过下式计算:

| (7) | ||

| (8) | ||

|

(9) |

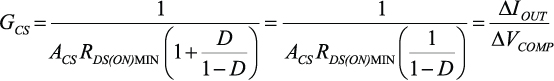

转换器的跨导GCS利用下式计算:

| (10) |

COUT是转换器的输出电容。ESR是该输出电容的等效串联电阻。RLOAD是最小输出负载电阻。ACS是电流检测增益,对于ADP1877,它可以在 3 V/V至 24 V/V范围内以离散步进选择。Gm是误差放大器的跨导,ADP1877 为 550 μs。VREF是与误差放大器的正输入端相连的基准电压,ADP1877 为 0.6 V。

GCS是与频率无关的增益项,随增强后的次级开关电阻RDS(ON)而变化。最高交越频率预期出现在此电阻和占空比D最低时。

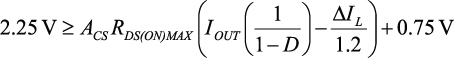

为确保在最大输出电流时不会达到补偿箝位电压,所选的电流检测增益(ACS)最高值应满足以下条件:

| (11) |

其中∆IL为峰峰值电感纹波电流。

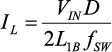

|

(12) |

如果斜率补偿过多,此处的方程式精确度将会下降:直流增益将降低,输出滤波器将引起主极点的频率位置提高。

斜率补偿

对于利用ADP1877 实现的同步反相SEPIC,必须考虑电流模式控制器2中的次谐波振荡现象。

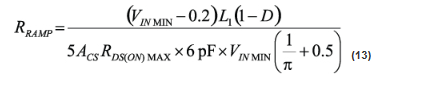

按照下式设置RRAMP,可以将采样极点的品质因素设为 1,从而防止发生次谐波振荡3(假设fUNITY设置适当)。

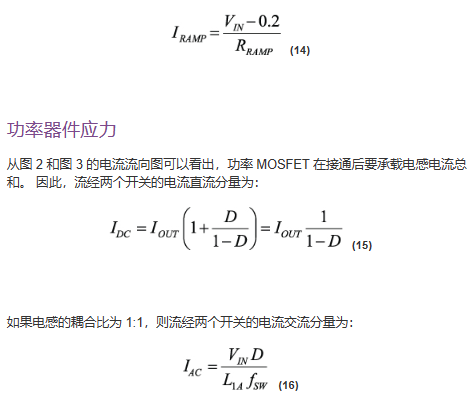

值得注意的是,随着增强后的次级开关电阻RDS(ON)降低,采样极点的Q也会下降。如果这一因素与其它相关容差一起导致Q小于0.25,则应进行仿真,确保在考虑容差的情况下,转换器不会有过多斜率补偿,并且不是太偏向于电压模式。RRAMP的值必须使得ADP1877 RAMP引脚的电流在 6 μA至 200 μA范围内,其计算公式 14 如下:

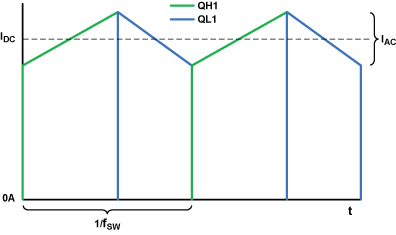

知道这些值后,可以很快算出流经各开关的电流均方根值。这些值与所选MOSFET的RDS(ON)MAX共同确保MOSFET具有热稳定性,同时功耗足够低,以满足效率要求。

图 7. 同步反相 SEPIC 的理想电流波形(忽略死区)

精确计算初级开关的开关损耗超出了本文的范围,但应注意,从高阻态变为低阻态时,MOSFET上的电压摆辐约为VIN + VOUT至 0V,流经开关的电流摆辐为 0 A至IOUT[1/(1–D)]。由于摆幅如此之高,开关损耗可能是主要损耗,这是挑选MOSFET时应注意的一点;对于MOSFET,反向传输电容(CRSS)与RDS(ON)成反比。

初级开关和次级开关的漏极-源极击穿电压(BVDSS)均须大于输入电压与输出电压之和(见图 5)。

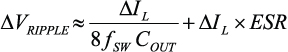

峰峰值输出电压纹波(∆VRIPPLE)可通过下式近似计算:

| (17) |

流经输出电容的电流均方根值(I rms COUT)为:

|

(18) |

方程式 12 所表示的峰峰值电感电流(∆IL)取决于输入电压,因此必须确保当此参数改变时,输出电压纹波不会超过规定值,并且流经输出电容的均方根电流不会超过其额定值。

对于利用ADP1877 实现的同步反向SEPIC,输入电压与输出电压之和不得超过 14.5 V,因为电荷泵电容与开关节点相连,当初级开关接通时,其电压达到VIN + VOUT。

实验室结果

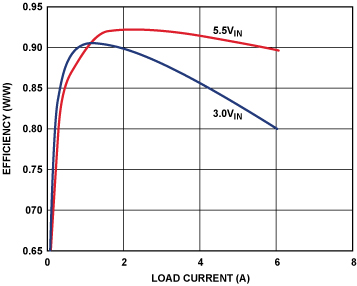

图 8 显示 5 V 输出、3 V 和 5.5 V 输入时同步反向 SEPIC 的功效与负载电流的关系。对于需要在 3.3 V 和 5.0 V 输入轨之间切换的应用,或者当实时调整输入电压以优化系统效率时,这是常见情况。采用 1 A 至 2 A 负载时,无论输入电压高于或低于输出电压,转换器的效率均超过 90%。

图 8. 效率与负载电流的关系

与图 8 相关的功率器件材料清单见表 1,其中仅采用常见的现成器件。一项具可比性的异步设计采用一个具有低正向压降的业界较领先肖特基二极管代替 QL1,在以上两种输入电压下,其满载时的效率低近 10%。此外,异步设计尺寸更大、成本更高,而且可能需要昂贵的散热器。

表 1. 功率器件

| 标志符 | 产品型号 | 制造厂商 | 值 | 封装 | 备注 |

| QH1/QL1 | FDS6572A | Fairchild Semiconductor | 20 BVDSS | SO8 | 功率 MOSFET/6 mΩ(最大值,4.5 Vgs, 25°C Tj) |

| L1A/B | PCA20EFD-U10S002 | TDK | 每个绕组3.4 µH | 30 mm × 22 mm × 12 mm | 1:1:1:1:1:1 耦合电感/铁氧体/每个绕组 35.8 mΩ(最大值) DCR |

结束语

许多市场对输出电压高于或低于输入电压(升压/降压)的高效率同相转换器的需求都在不断增长。ADI 公司的双通道同步开关控制器ADP1877允许用低损耗MOSFET代替常用于功率级的高损耗功率二极管,从而提高效率,降低成本,缩小电路尺寸,使系统达到苛刻的能耗要求。只要遵循几项原则就能快速算出可靠补偿所需的元件值,并且利用常见的现成器件便可实现高效率。

审核编辑:郭婷

-

非反向降压-升压转换器的拓扑结构和如何实现应用设计2020-08-30 3037

-

今日推荐-YB2414高效率同步降压转换器2024-01-13 9036

-

高效率2.7A同步升压转换器管理IC2018-06-08 2739

-

基于同步反相SEPIC拓扑结构实现高效率降压/升压转换器2018-10-22 2968

-

高效率72W功率输出的非同步降压升压转换器2018-12-17 2027

-

降压、升压和降压升压拓扑结构详解2019-03-19 4310

-

LTC3125的典型应用是高效率,同步升压型DC / DC转换器2019-08-30 2224

-

基于L6920D的高效率同步整流升压转换器演示板2020-07-30 1797

-

基于反相SEPIC的高效率降压/升压转换器的实现2010-10-29 2709

-

同步反相SEPIC拓扑结构的降压升压转换器实现2011-03-30 931

-

AN-1075: 使用ADP1870/ADP1872的同步反相SEPIC使同相降压/升压应用实现高效率2021-03-20 714

-

高效率15V/1.5A同步升压转换器2022-09-07 756

-

如何在高压应用中利用反相降压-升压拓扑?2022-11-15 1989

-

用于汽车和工业装置的高效同步SEPIC2023-01-31 1856

-

同步反向SEPIC拓扑提供高效率降压/升压转换器2023-02-01 3409

全部0条评论

快来发表一下你的评论吧 !