源极接地放大电路设计(2)

模拟技术

描述

二 电路设计步骤

2.1 确定电源电压

电压电源V1由最大输出电压决定。例如为了得到Vpp=3V的输出电压,电源电压必须在3V以上,否则输出信号会失真(削波)。为了确保源极偏置电流,在R4上需要有电压存在,例如1V或者更多。因此合计起来,电源电压至少在4V以上。当前例子中,此电压取值为15V。

2.2 选择何种沟道的FET

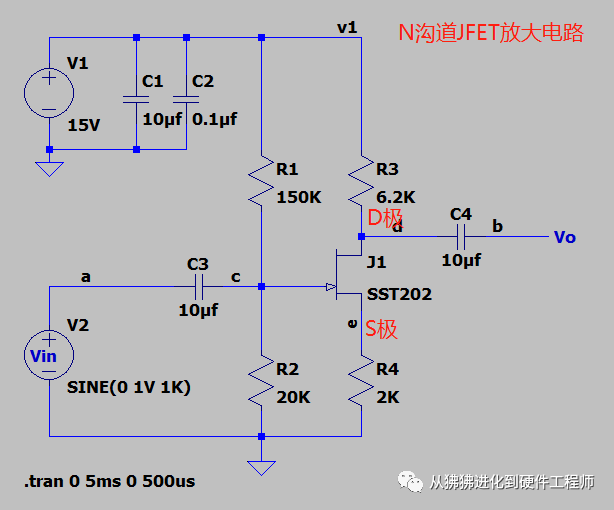

选择FET时,电流和耐压不要超过其最大额定值。另外可以使用N沟道器件组成放大电路,也可以使用P沟道器件组成放大电路。之前讨论的是N沟道FET组成的放大电路。

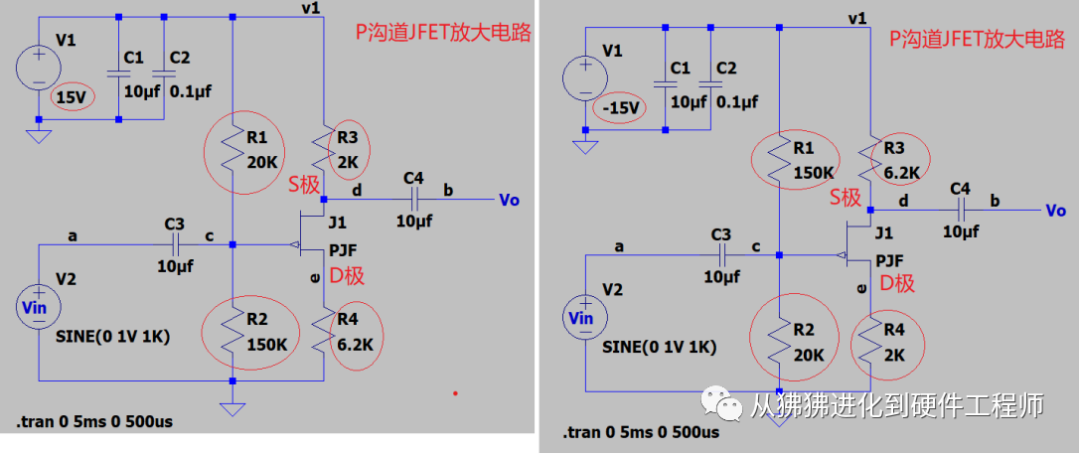

使用P沟道FET组成的放大电路,其电流方向与N沟道FET放大电路相反,因此需要变更偏置电压极性,需要将电源和GND调换。下图是2种P沟道JFET放大电路。

2.3 依据电源电压选择FET的Vgs耐压值

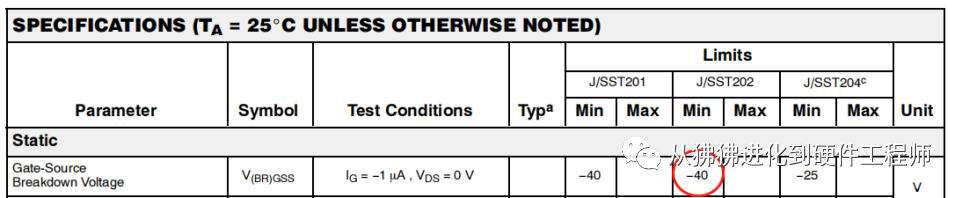

因为上一步中确定电源电压是15V,针对N沟道FET,它的栅极-源极间电压Vgs,最大有可能达到15V。因此需要选择那种Vgs大于15V的FET。大多数FET的这个参数都在30V以上。我们选择SST202,它的Vgs(BR)=-40V

2.4 确定漏极电流Id

确定放大电路工作点时,我们需要先确定Id,而不是Vgs。因为FET的重要特性都是随Id变化而变化的。当Id设定好之后,从spec的传输曲线中自然可以得到Vgs。

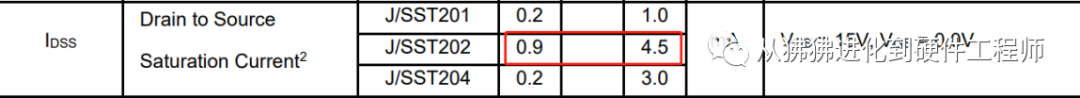

在JFET的spec中会定义Idss。例如SST202的Idss在0.9~4.5mA。确定放大电路的Id时,Id要比Idss的最小值(0.9mA)还低。例如设计Id=0.1mA。

注意:如果Id的选择太接近Idss,大信号输入后,因为Id无法超越Idss,输出波形可能会被限幅,即被削波。

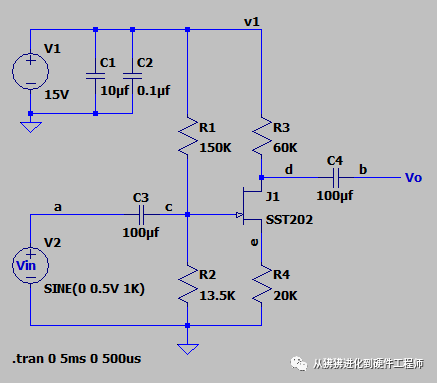

2.5 确定源极电阻和漏极电阻

在3.1.2节提到,这种放大电路的放大倍数是由源极电阻Rs(下图R4)和漏极电阻Rd(下图R3)的比值决定。

例如希望放大倍数Av=3倍,那么

Vgs电压会因为Id不同而不同,也会受到温度的影响。例如Id随着温度变化而变化,进而导致Rs上的电压变化(此处是指直流电压),最终导致Vgs变化。为了抵消Vgs因为温度变化而变化,使漏极电流具有稳定性,需要Rs上的电压降>1V(使Vgs

我们设置Rs上的电压降是2V,因为Id=0.1mA,

Rs=Vs/Is=Vs/Id=2V/0.1mA=20KR

接下来

Rd=Rs x Av=60KR。仿真电路如下:

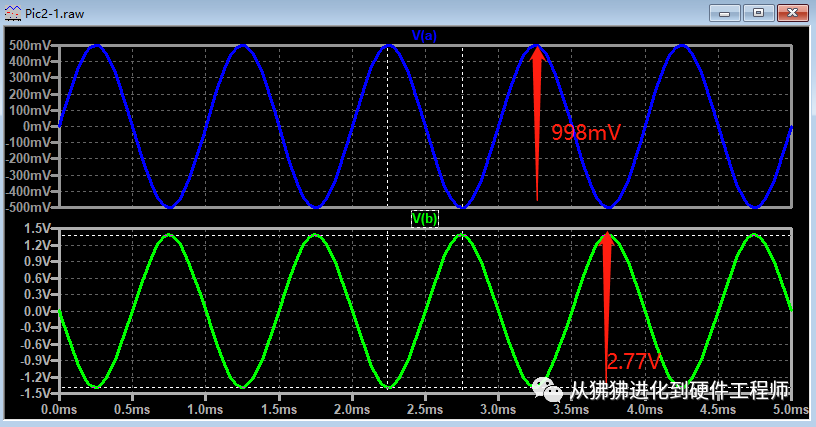

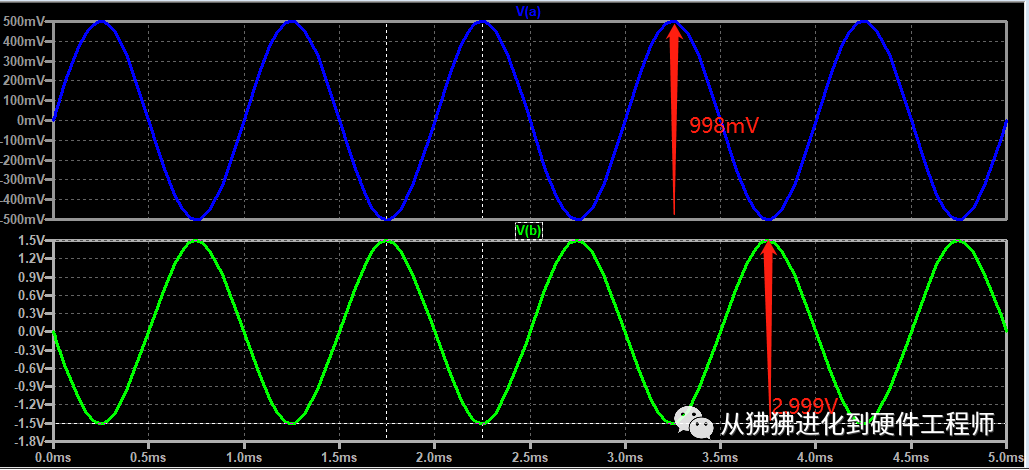

仿真结果如下:Vo/Vin=2.77V/0.998V=2.77。

仿真放大倍数是2.77V,和理论上的3倍有差异。

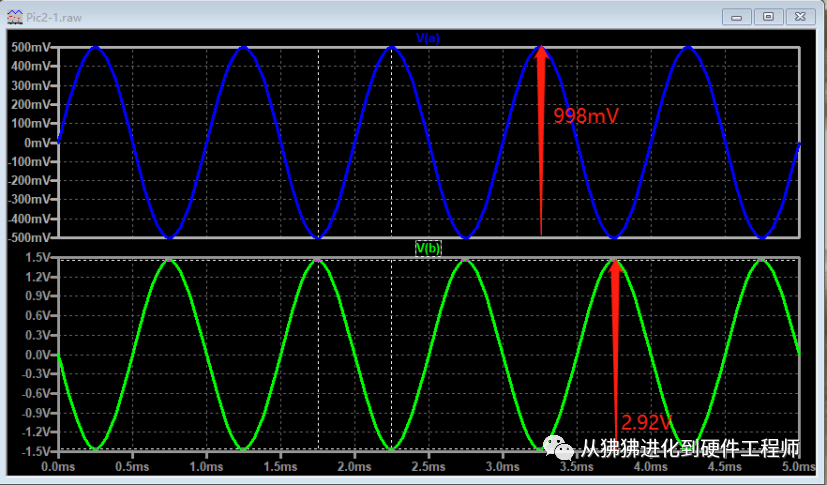

无意中将R3和R4从60K和20K增大到600K和200K,放大倍数可以提高到2.93,如下图。此时Id只有大约15uA,比Idss=900uA小了许多。

保持R4=20KR,修改R3=65KR,R3/R4=3.25倍时,仿真结果是3倍,如下图。此时Id大约在150uA左右。

**哪位老师可以解释为什么仿真值(R3=60KR,R4=20KR)和理论计算(R3=60KR,R4=20KR)结果不同吗?**

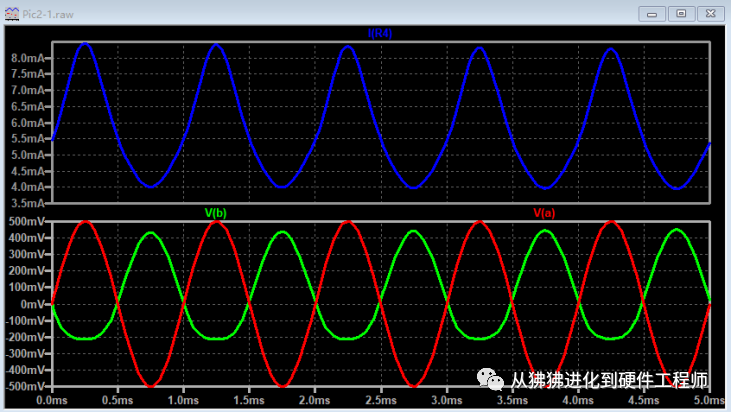

就像上述说的,首先需要考虑的是Id的电流要比Idss min值小。如果将R4和R3调整的很小,也就是将Id变大,超过Idss max的4.5mA。输出就失真了,如下图是Id大约在7mA时的输出波形。蓝色是Id,红色是V2,绿色是Vo。输出已经失真。

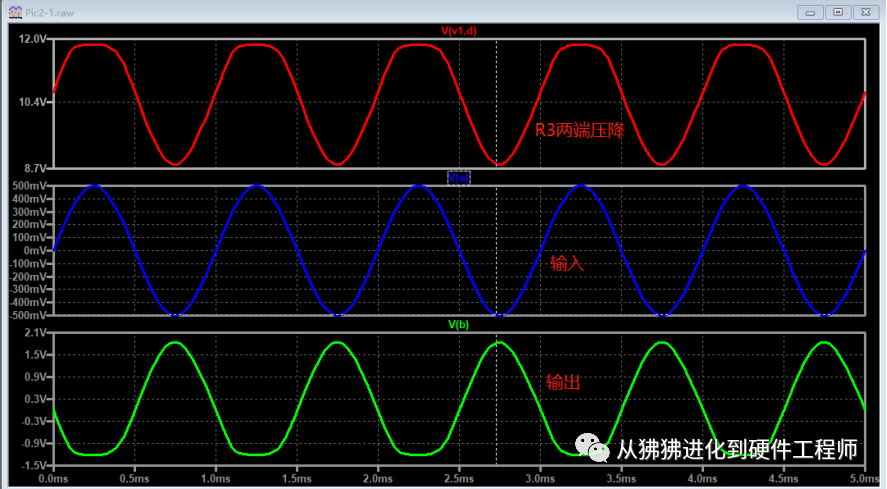

另外如果将Rd增大,即R3从65KR改变到80KR -->R3自身压降变大 -->漏极电压Vd下-->输出波形的下半周期被钳制。换句话,是R3变大带来自身两端电压升高,向上升时会碰到15V的上限,被钳制,进而导致输出下半周期被钳制。如下图。

输出波形的上半部分不失真,是因为R3变大带来自身两端电压升高,向下升时距离0V的下限还很远,不会被钳制,不失真。

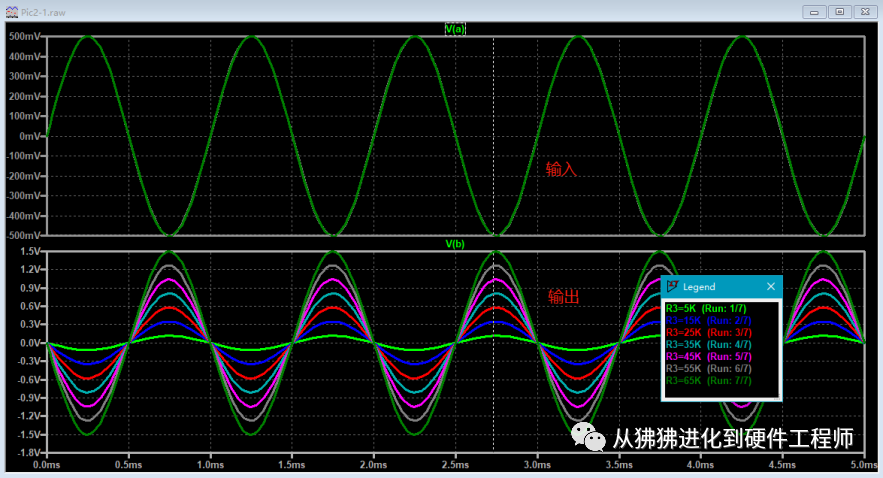

另外如果将Rd减小,输出波形会减小。因为放大倍数减小了。如下是R3是不同值时的仿真结果。

未完待续

-

晶体管电路设计(下)2025-04-14 594

-

源极跟随器电路设计2023-08-31 3836

-

源极接地放大电路设计(1)2023-06-23 860

-

采用N沟JFET与PNP型三极管的放大电路设计2022-10-18 4622

-

共源极放大器电路及原理2009-12-08 20953

-

采用N沟MOSFET的源极接地型开关电路图2009-08-15 3117

-

导致源极接地电路高频特性降低的因素电路图2009-08-08 585

全部0条评论

快来发表一下你的评论吧 !