PCB布局挑战——改进您的开关模式电源设计

描述

隐藏的 PCB 布局威胁——PCB 耦合

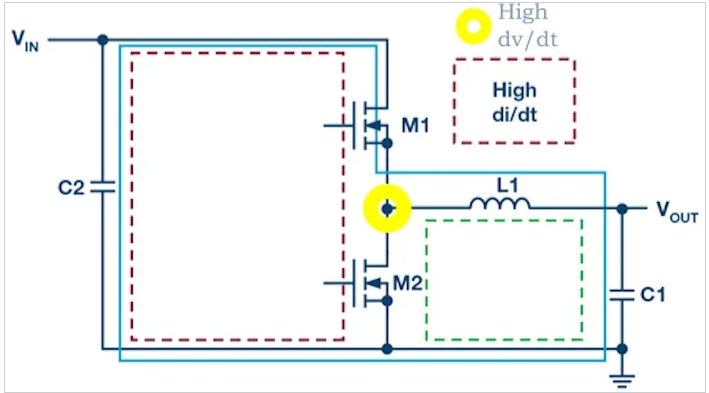

与 SMPS 相关的 EMC 原则通常要求设计人员密切注意 SMPS 布局中的两个耦合因素,如图 1 所示:

具有高 dv/dt 的电压开关节点

“热电流回路”,其中包含子系统中的 di/dt

图 1.显示降压转换器 di/dt 和 dv/dt 位置的示意图。图片(修改后)由Analog Devices提供

这里发挥作用的机制和风险是不需要的能量以电容 (dv/dt) 和电感 (di/dt) 耦合到系统的其他部分,或者更糟的是,以辐射和传导发射的形式耦合到系统之外。

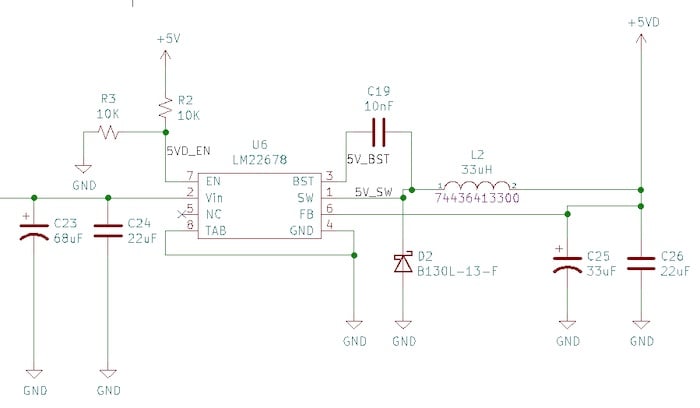

PCB 设计后期制作审查

深入研究该项目,我们将检查LM22678 5A 转换器(图 2)的 PCB 布局,其中V输入为 12 V(未显示),V输出为 5 V。这是一个非同步降压转换器,使用用于其低侧开关元件的 B130L-13-F 肖特基二极管(是的,在您检查之前 - 系统消耗的电流小于二极管的 1 A 额定值! )。

图 2.非同步 LM22678 降压转换器 12 V 至 5 V 的原理图。

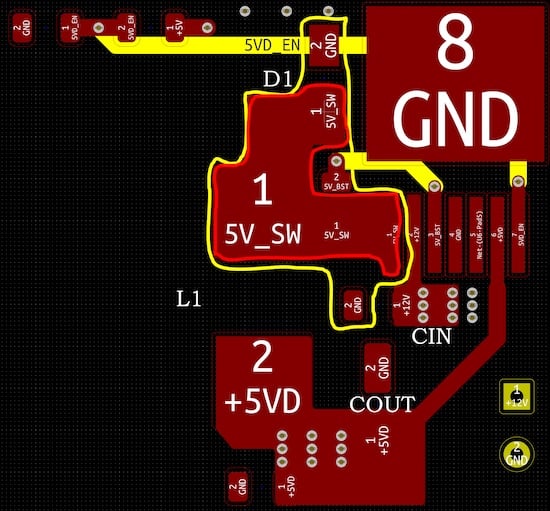

限度地减少电容和电感耦合通常并不复杂,但很容易被忽视,从而导致排放测试失败和上市延迟。在下面的图 3 中,我们看到了用于非同步降压稳压器的 TO-263 封装布局,其中标识了电压节点(红色轮廓)和热电流环路(黄色轮廓)。

图 3.具有低侧功率二极管的非同步降压稳压器设计。

为清楚起见,电路板上的铜填充已被隐藏。总的来说,这种设计存在三个明显的问题:

高 di/dt 环路比需要的大得多

没有过孔连接 C IN 或 C OUT的 GND 节点(它们被地面浇注覆盖)

交换节点可以更小

这些设计选择的终效果意味着电流环路没有得到很好的控制,并且由于平面之间没有过孔,电流没有明确的路径返回源头。

对于 EMC——(电气)沉默是金

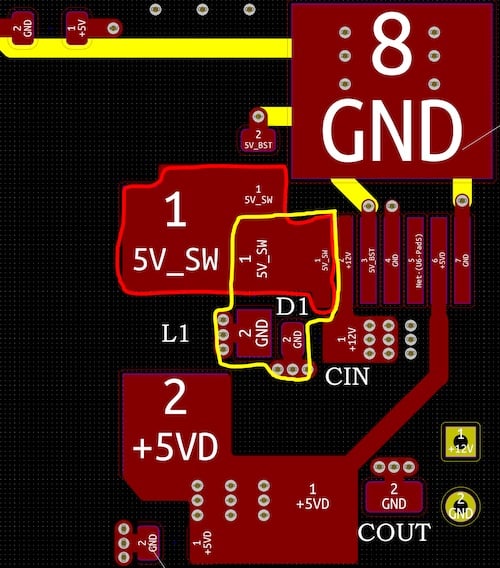

应用从 Hubing 博士的讨论中收集的原则,可以在下面的图 4 中看到改进后的布局。它具有优化的电压节点、更小的热环路以及通过访问每个无源组件的第 2 层参考平面。此外,初级 C OUT电容器也相对于原始设计旋转了 90 度,从而降低了输出轨上的噪声风险。

图 4.改进后的布局考虑了耦合机制。

通过在开关引脚和电感器之间移动低侧二极管,我们可以更好地限制由高 dv/dt 耦合效应产生的潜在串扰噪声。此外,通过减小热回路几何形状,高 di/dt 磁场耦合的影响会降低。

尽管这些变化很小,但它们不需要额外的电路板空间或改组其他子系统。然而,通过将电流环路减少约 50% 并优化电压节点,无疑提高了系统合规性。

当您设计符合CISPR EMC 标准的商业产品时,每个 dBμV 都很重要,设计阶段的微小变化可能意味着成功发布或错过市场窗口之间的差异。

-

开关电源PCB布局2015-08-13 0

-

印刷电路板布局的挑战ーー改善你的开关电源设计2022-06-10 0

-

高频开关电源的关键布局技巧2009-09-28 819

-

如何做好非隔离式开关电源的PCB布局2012-12-04 8372

-

开关电源的PCB设计(布局、排版、走线)规范2016-07-26 872

-

LED开关电源PCB元件布局设计2019-05-05 5130

-

TPS5430开关电源 正负电源 低噪声设计 选材分析 布局布线分析 原理图PCB分析2021-10-21 1502

-

开关模式电源板的布局优化是什么样子2022-10-08 556

-

开关电源PCB设计要点总结2023-03-27 2424

-

PCB布局挑战—改进您的开关模式电源设计2023-06-30 489

-

开关模式电源电路板布局的黄金法则2023-07-08 583

-

开关模式电源设计PCB布局改进方案2023-07-26 741

全部0条评论

快来发表一下你的评论吧 !