总结一下AMD CPU的信息

描述

和AMD的确无缘,在拿到Day1 的大礼包之后,我就上交了笔记本,只是在AMD connection中看了一些内网的信息,但是因为实在对AMD的CPU不熟悉,也没搞明白啥。

近来在AMD的平台上需要搞搞性能提升,因此看了看AMD的CPU的相关信息,之后就一发而不可收拾,自己总结了一下AMD CPU的信息,这个权当没有机会参加的AMD的new hire 培训了。

本篇从AMD的CPU的崛起开始,以AMD的ZEN架构为主线,先看一下AMD的整体情况。

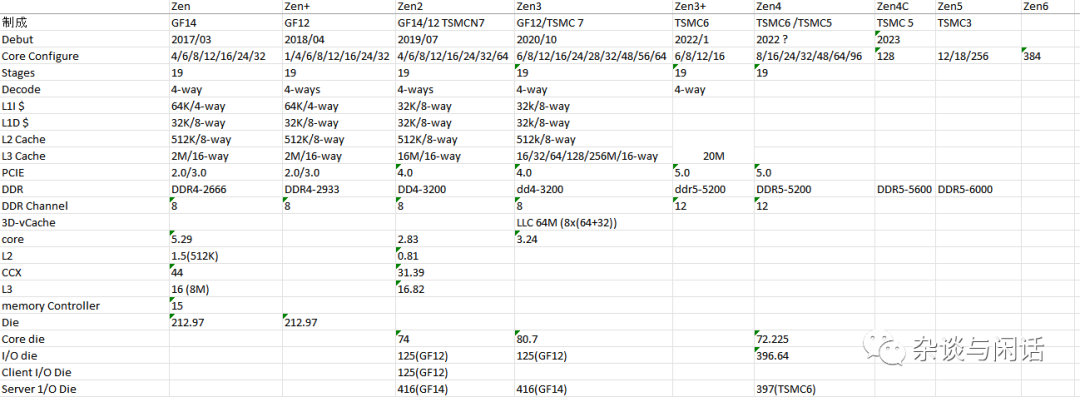

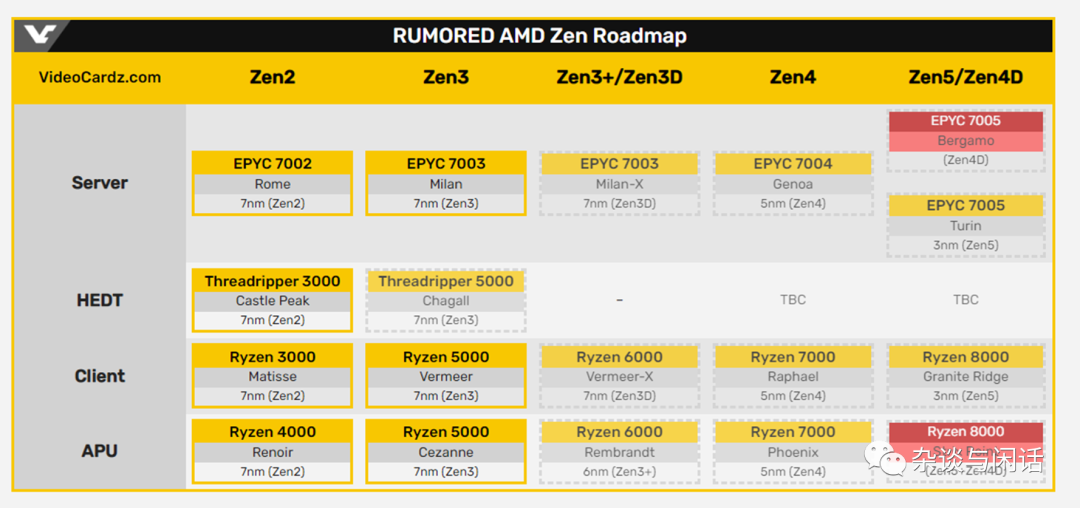

架构从Zen开始,到Zen+/Zen2/Zen3/Zen3+/Zen4/Zen4C(D)/Zen5/Zen6 基本已经很整齐了。很多Xilinx的同学如果转AMD CPU,基本可以做到退休了。

从GF14开始,现在全面转向TSMC,基本上基于Core Die 和IO Die的整合模式。在Zen2/3的时候,需要使用GF的IO Die,这个还说得过去。在Zen4 的时代,全面转向TSMC,core die是5nm,而IO die是6nm。感觉这个io die之后越来越大的话,可能和core die 一样,放多个。反正AMD的CPU 自己就可以做NUMA 分割,从1到2到4, 在12 core die的时代还是NPS4。说不定后面出现NPS6/8.

从core的架构上,Zen从GF转到TSMC之后,微架构上变化不大了,主要的变化就在玩弄IO Die的DDR 控制器和LL Cache,已经加上了 GPU的APU, 还有就是最近比较热的3D Vcache,Milian-X 可以支持8X (32M (core die)+ 64M(Vcache) )=784M 的L3 cache,这个估计Intel要哭死了。当然还有上个星期传出来的Xilinx 的AIE 引擎, 我对于Xilinx在AI方面的投入一直是持否定态度的,对于这个AIE+IODie +Core Die 我谨慎乐观。

从Zen2 开始,io die也分Client 和 Server 两类,这个估计以后会一直分下去,两种IO Die的主要不同应该在DDR 控制器和PCIE 接口上,以后会有更大的不同?.

从Die size上看,毫无疑问IO die是整个封装中最大的了, 实在有点惊诧Zen的core 的size居然如此之小,core die里面的2/3应该都是cache 了。

Zen+和Zen3+都类似于Intel的tock,架构不改,改工艺。但是Zen3+其实更像一个鸡肋,只有6000系列。

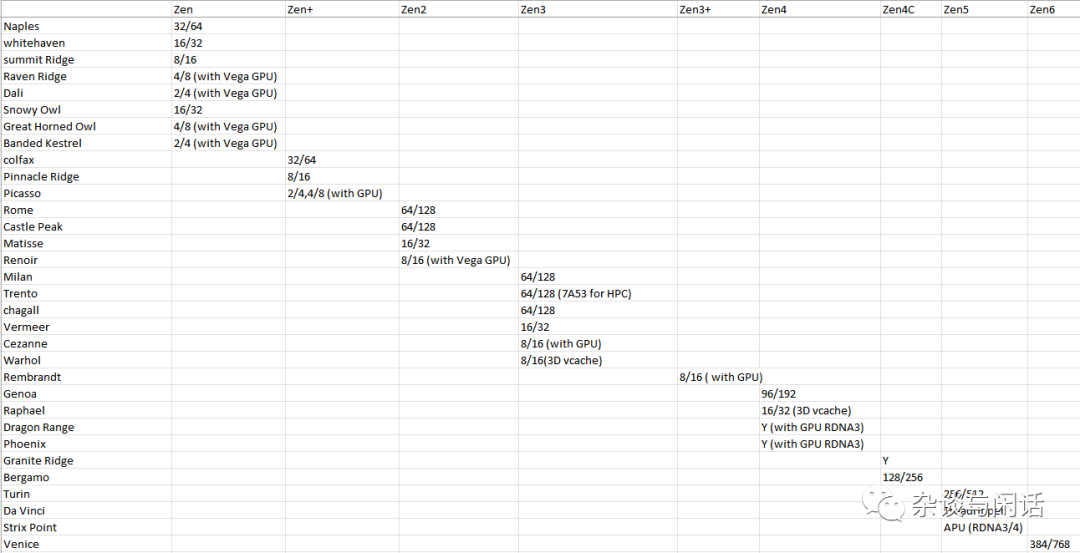

后面就是另一个比较复杂的信息了,codename,和Intel的lake不同,AMD对于意大利是比较执着的。

这个里面基本上涵盖了AMD的主要CPU的产线。

Embedded的CPU 的命运比较搓了,好像转了TSMC之后就没有了。在Zen的时候感觉有好多。

Zen3 有一个HPC定制款,据说是加了AI的功能,应该是AVX-512和BF16之类的支持,如果以后把AIE加进去,我先呵呵了。

从产品的排布来看,Zen 和Zen2的差别要比Zen2 和Zen3的差别大,对于Zen3和Zen4的差别,这个后面等着更多的产品信息泄露吧。

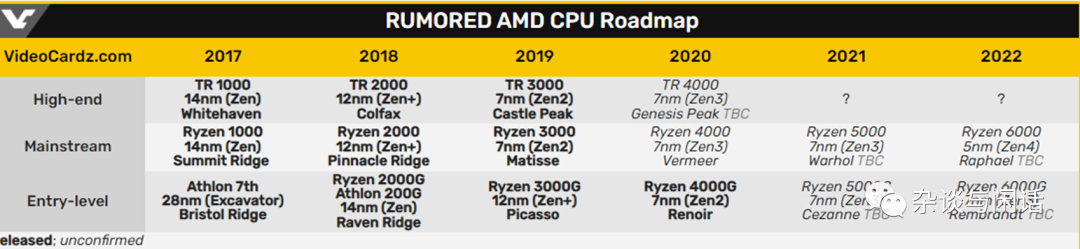

对于AMD的产品,初看还是比较乱的,但是如果把握市场,还是很清晰的。

Desktop

这个可以看到Entry-level主要是给笔记本这类的,往往会包含GPU,core die的数量只有1个,甚至有一些都是单die的。

而High-end的CPU的core数量和Server基本上可以相等,但是后面的Threadripper真的会到96Core 吗?

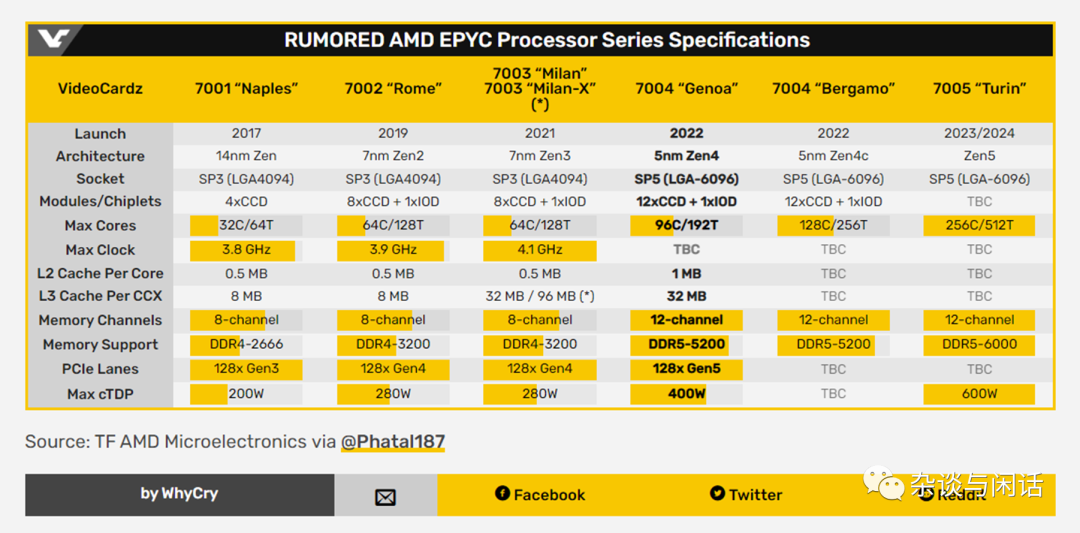

Server

最早的热那亚传说是128core,现在基本上应该是96 core,估计是看Intel落后太多,也要挤挤牙膏了。

PCIE5.0+DDR5应该是标配了,虽然DDR5的高价给了Intel ice lake的机会,但是该来还会来的。后面AMD的Server CPU会增加啥功能,估计应该像Intel一样增加Ethernet接口了。否则,在PCIE5 待上3代,有点无聊。

这个图基本上把Ryzen和EPYC的都放进来了,整个图就说明一件事,都是TSMC,而且目前Chiplets的路应该是定局了。

今天的总结到此,目前对于AMD的产品有了一定的了解了。后面需要从CPU的微架构,cache/memory 以及data flow 来细细琢磨AMD的一路走来。

审核编辑:刘清

-

AMD揭开Zen CPU核心技术Ryzen神秘面纱2016-12-15 1686

-

总结一下定时器的几种输出比较模式2023-07-21 80601

-

总结一下串口的几种使用方法2022-02-10 1340

-

AMD CPU核心2009-12-17 1124

-

AMD CPU核心简介2009-12-24 1220

-

AMD CPU的发展简史:从x86-64位技术到全新的 Ryzen 架构2017-04-21 20522

-

了解一下CPU的各种接口2018-06-11 12422

-

AMD与Intel的CPU插槽区别2019-06-25 11439

-

电磁炉加热一下就停一下什么原因及解决办法2020-03-18 288953

-

电磁炉加热一下就停一下什么原因2021-06-04 41940

-

外媒公布AMD锐龙CPU第一季度产量信息2021-01-25 1946

-

总结一下OpenCV遍历图像的几种方法2023-01-18 2441

-

剖析一下CPU对代码的识别和读取2023-02-13 1983

-

工业用冷水机使用时常见的十大故障,今天就给大家总结一下2022-07-04 2485

-

总结一下LM317的几种经典应用电路2024-05-01 11988

全部0条评论

快来发表一下你的评论吧 !