FPGA定点数截位的基本准则

可编程逻辑

描述

FPGA内部表示正负数,小数的规则。两者相比之下,定点数实现简单,表达更为直观,所以在很多时候FPGA通常使用定点数表示小数。但在各种运算下,定点数的位宽会不断增大,为了节省资源,这个时候必须进行取舍,进行一定的截位。

截位的规则比较简单,但在FPGA内部使用广泛。

首先,在讲截位之前,我们需要了解FPGA定点数运算的扩位规则,规则如下:

1.两个有符号定点数相加减,位宽大的数需要扩展一位符号位,位宽小的数扩展符号位至两数位宽一致。然后再进行加减,防止溢出。

比如,两个数,A数m位,C数n位,m > n;

A在最高位补充一个符号位,位宽变为m+1; B在最高位补充符号位,使位宽变为m+1,A+C最终运算结果为m+1位;

2.两个无符号定点数相加减,位宽大的数需要扩展一位,扩展位为0,;然后再进行加减,防止运算结果溢出。

比如,1111 + 1 转变为:0 1111 + 1 = 1 0000;

A数m位,C数n位,m > n;

A在最高位补充一个符号位,位宽变为m+1; A+C最终运算结果为m+1位;

3.两个定点数做乘法,运算结果位宽为两数位宽之和。

A数m位,C数n位,m > n;

A*C最终运算结果为m+n位;

经过一次乘法运算后,结果比原来的数据位宽大了许多,一个系统往往不止一次乘法,为了节省资源,这里就引入了截位。截位不是随便截,截位的优先级如下:

1.首先截取数据符号位

前面的文章提到,符号位不影响数据的大小,只影响数据的正负,所以一个数据里面只需要有一个符号位即可;

两个有符号定点数相乘,符号位位数至少是乘数与被乘数的符号位数之和;这就说明了两个1位符号位的定点数相乘,结果里面至少有两位小数。

这个时候我们可以放心的截取掉最高位,因为这个数里面不止一位符号位;

数据的符号位

一个正常的有符号定点数的最高位一定是符号位,从高往低,与其变化一致的都是符号位,当一个数在它最大的时候,有几位数据与最高位保持一致,数据就有几个符号位。

有符号定点数至少需要保持一位符号位,否则数据会失真。因此这意味着截取符号位的策略不能激进,需要保守。

2.截取低位数据

这一步弃车保帅,损失一部分精度节省资源;很好理解,舍弃低位数据相比舍弃高位数据损失精度会更小。

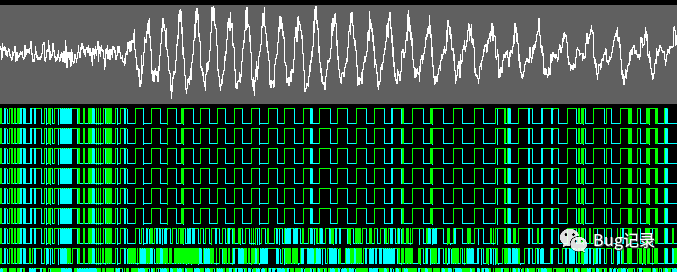

舍弃低位

图中框住的正是截位的过程,coef是一个位宽2W的值,截去了3位符号位,舍去了低W-3位数据。'2W-4-:W'运算符代表从2W-4位开始向下共W位数据。

截位还有些其他的作用,例如将某个数除8,可以将这个数的低三位截取,同时补充高三位的符号位,就达到了除8的作用。

例子:

0100 000 / 8 --> 0000 1000

原理是微机原理的知识,计算机内部的数据是二进制表达,左移一位数据代表数据乘以2,右移一位数据代表数据除以2;

-

固定点数运算案例的程序2025-12-12 94

-

定点数表示实数的方法以及定点数在硬件上的运算验证2025-10-28 194

-

扩充浮点运算集是否需要自己在FPGA板子上设置一个定点数转为浮点数的部分?2023-08-11 584

-

定点数和浮点数的区别是什么2022-02-21 2214

-

定点数和浮点数在STM32单片机中使用傅里叶(FFT)变换的理解2021-12-24 1961

-

功能函数中的浮点数转换为定点数2021-08-17 1732

-

DSP功能函数-定点数互转2021-08-11 1926

-

verilog程序定点数的资料2019-03-27 2414

-

6618虚拟定点数学库IQmath2018-06-21 2567

-

在FPGA里浮点数与定点数表示法原理展示2017-11-18 9364

-

LabVIEW中定点数有什么用途?LabVIEW中定点数应用解析2017-11-16 10431

-

第7章 DSP定点数和浮点数2016-09-22 4392

-

【安富莱——DSP教程】第7章 DSP定点数和浮点数(重要)2015-06-03 9050

-

浮点数与定点数2013-03-27 3353

全部0条评论

快来发表一下你的评论吧 !