FPGA在线调试的方法简单总结

可编程逻辑

描述

Xilinx被AMD收购的事情把我震出来了,看了看上上一篇文章讲了下仿真的文件操作,这篇隔了很久远,不知道该从何讲起,就说说FPGA的在线调试的一些简单的操作方法总结。

文章以Altera的Quartus II, Xilinx的Vivado工具为例,其他工具(如ISE的Chipscope)就暂不赘述了。

其实很多时候,为了图方便,FPGA的Verilog设计完之后,会省掉仿真的过程,直接使用FPGA的在线调试工具来检查电路逻辑是否有问题。包括我自己刚开始学习FPGA时,没感觉到仿真相比在线调试的优势,重点去学习在线调试了。但现在来看,这样的操作很不规范,而且随着项目的规模越来越大,这样做的效率也会迅速下降。

但这种方法在某些验证领域还是占有一席之地,而且小规模模块验证时,它也很有优势。

而且相对于仿真来说,FPGA的板级调试结果会更加真实些。

Altera

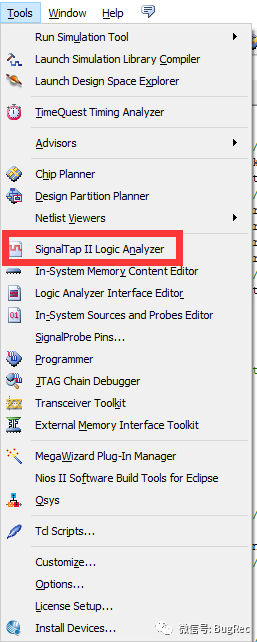

在Quartus II找到下图的工具

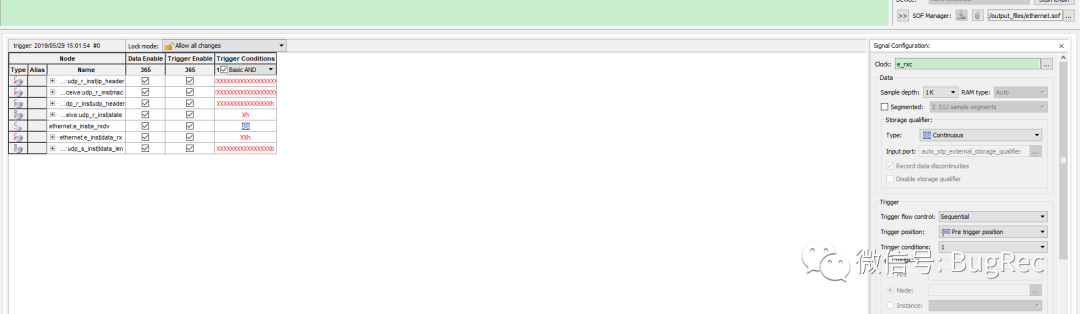

进入之后,找到这个界面

首先设置后右上角的SOF文件,然后顺着SOF文件的下方,依次设置Clock(采样时钟),Sample depth(采样深度)等参数。

Clock参数会影响信号的显示值,可以理解为如果采样时钟没有数据变化快,那么采到的数据中间会漏掉某些值,而且不论快慢,都可能造成采样上的一些问题。所以这里推荐使用与驱动被采数据或者说相同时钟域下的时钟。注意,只是影响信号的抓取显示值,不大会影响信号的真实值

Sample depth参数会影响信号抓取的深度,设置小了可能对调试不方便,比如抓取传输包的帧头,抓到后想看看整个数据包的格式,但是深度太小没有显示出来;设置大了占用的面积会增大,可能会超出资源。

然后在左边空白处双击,选择信号

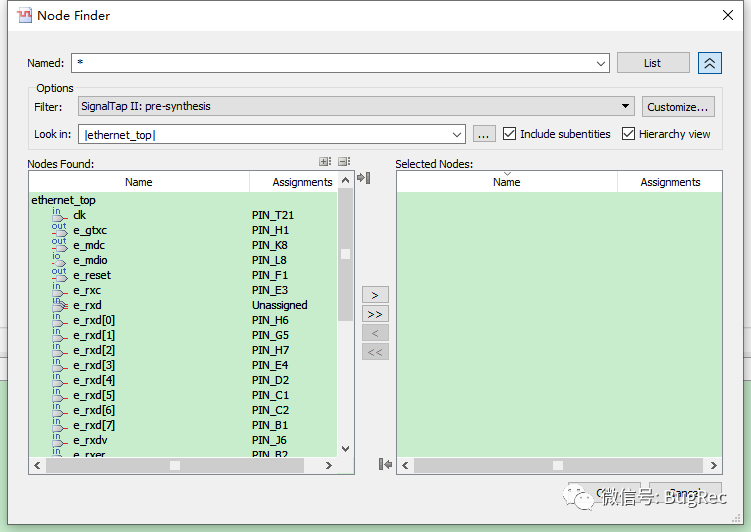

注意,Filter是选择某个特定时期的信号,比如pre-synthesis,意思就是综合前的信号,此时信号跟我们RTL代码中的信号,名字保持一致,最方便查找,所以我经常使用这个类型的Filter。

然后点击List,选择想要抓取的信号,点击ok,然后保存文件,重新走一遍综合,布局布线,生成bit文件的路子。最后就可以在这个工具中下载响应的sof文件,然后开始在线抓取信号。

Xilinx

vivado中,在线调试的方法就很多了,使用mark_debug和ILA核的方式。

- mark_debug

可以在被抓取信号的定义语句开头插入(* MARK_DEBUG="true" *),使得工具自动识别需要抓取的信号。如下图示例

(* MARK_DEBUG="true" *)wire [7:0] read_data ;

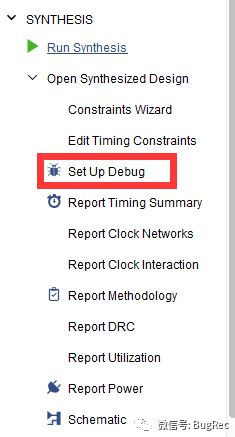

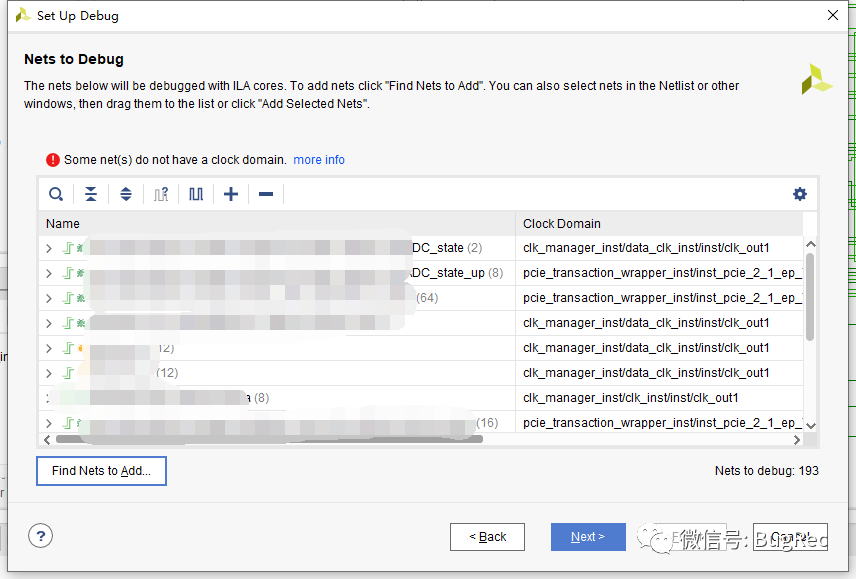

一路Next后,你可以看到这个

图里的信号就是之前使用了Mark_debug标识的信号,如果有哪些信号不想抓取了,可以直接在这里删去,如果你有信号忘记做标识了,也可以使用左侧的Find Nets to Add方法。

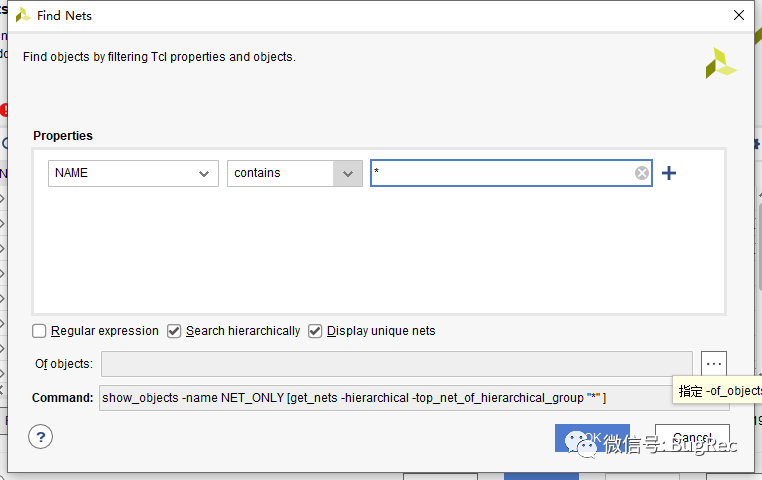

使用通配符*加上信号的名字,可以搜索到对应的信号然后直接加入到信号列表。

注意,有些信号可能没有自动指定合适的时钟网络,需要自己手动指定,然后才能Next

然后工具会自动根据前面的设置向相应的XDC文件写入参数,如果打开了XDC文件,一定要看是否保存了最新的结果。我刚开始很多次在这里没注意,导致XDC还在以旧版的内容运行,设置的内容没有生效。

如果这个步骤中多个信号存在多个时钟域,最终生成的调试文件下载进入板子后,会出现多个ILA调试界面。

- ILA IP核

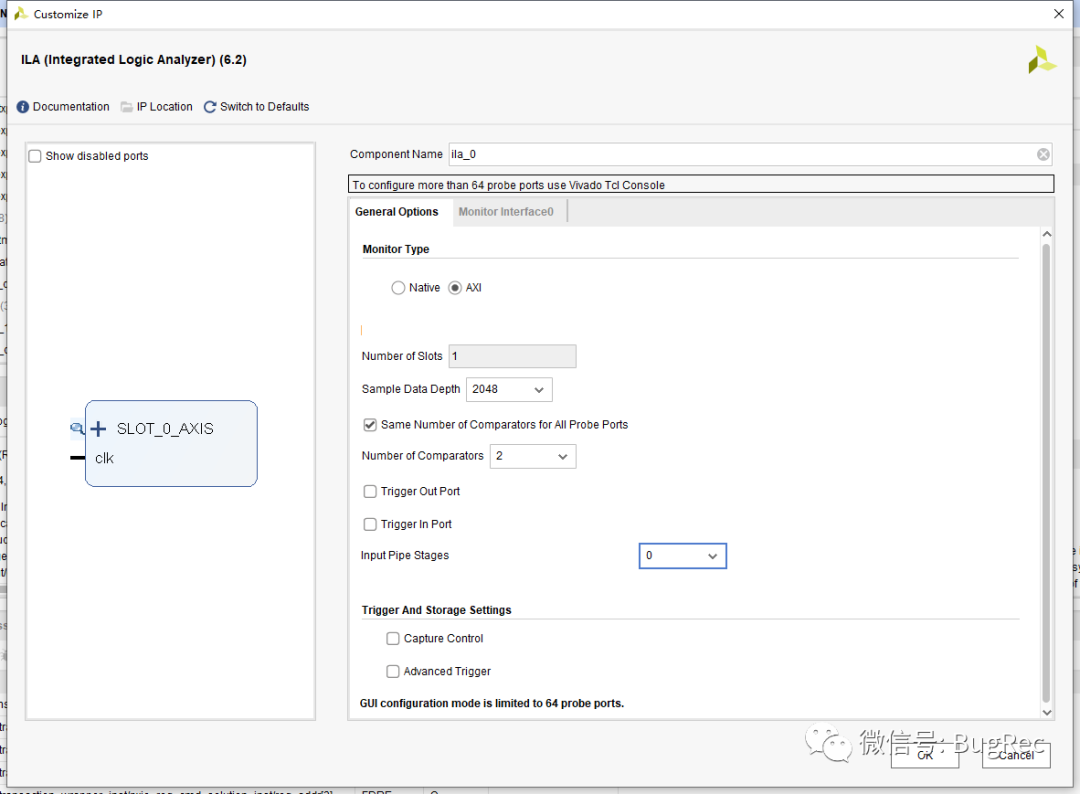

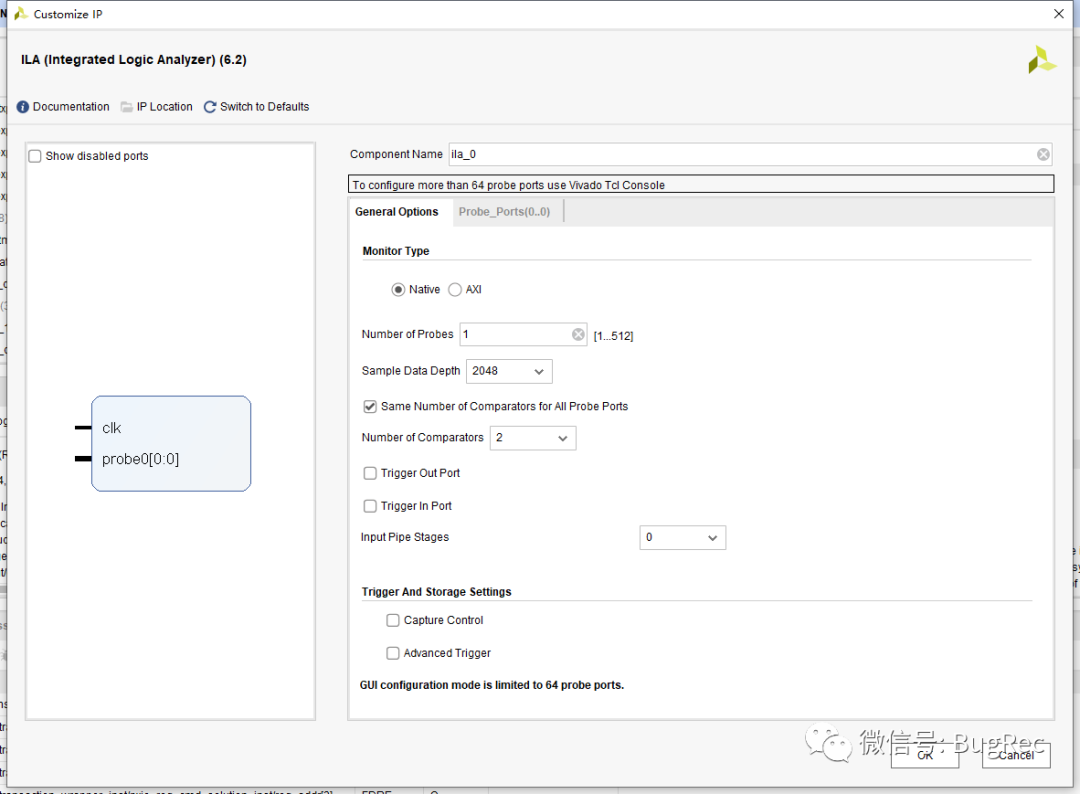

可以在IP Catalog寻找ILA IP核, IP设置中,如下图,可以选择Monitor Type

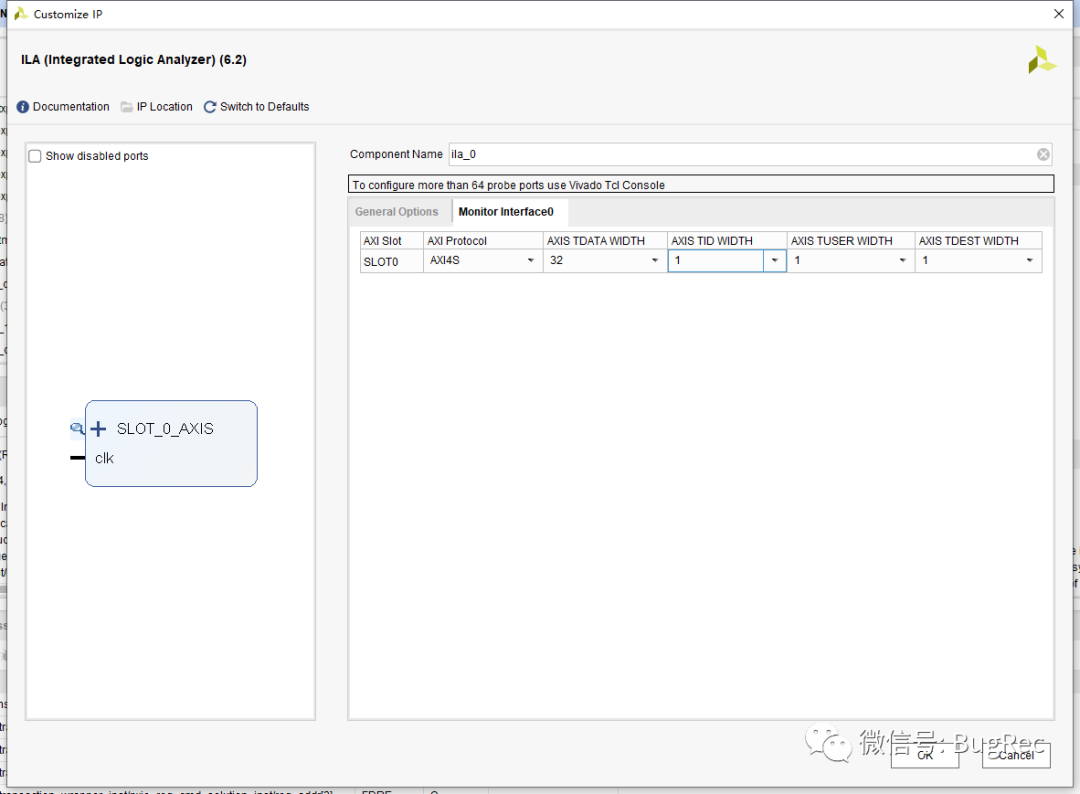

如果选择AXI,则在第二个设置界面,需要选择AXI协议类型,AXI数据位宽,地址位宽等等参数。

关于AXI协议内容可以看看之前的内容回顾。

也可以选择Native的Monitor类型,那么就可以设置Number of Probe,这个参数决定了被抓取信号的通道数,Sample Data Depth是抓取深度。

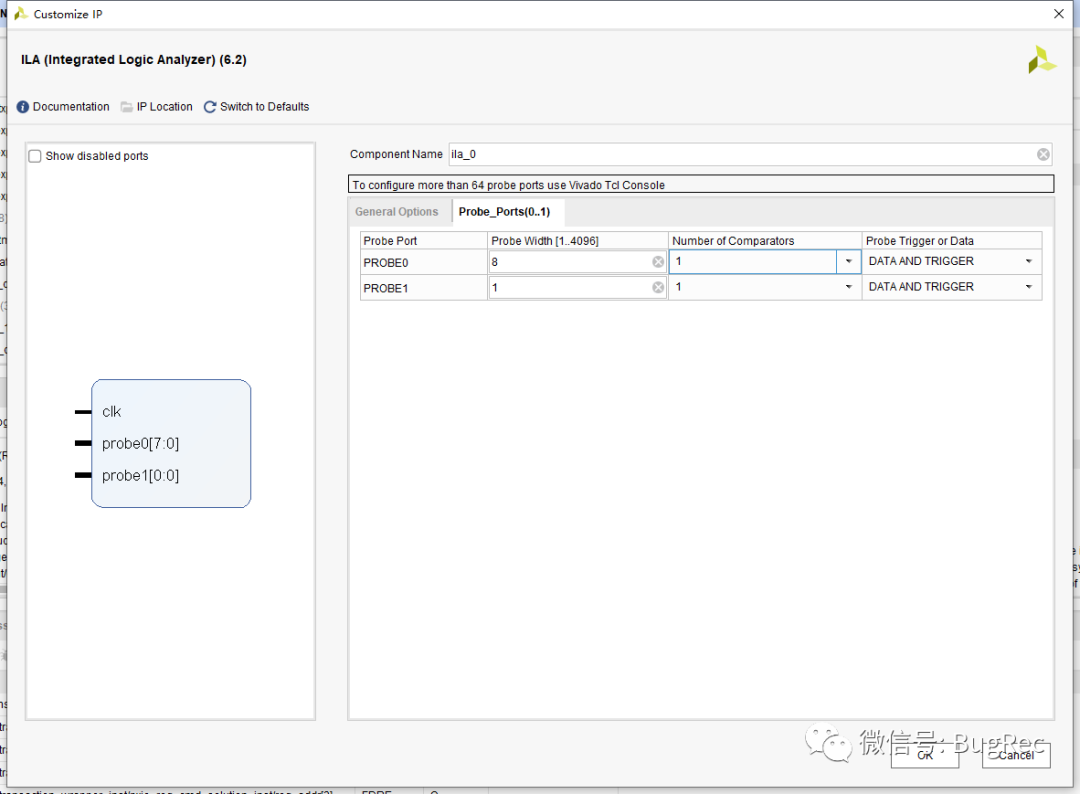

这样在第二个设置选项里,可以设置每个数据通道的数据位宽等参数

最后,不管是哪种方法,都需要重新走一遍综合,布局布线,生成bit文件的步骤,然后将调试文件和bit文件一起下载到FPGA芯片进行调试。

-

fpga时序分析案例 调试FPGA经验总结2023-08-01 3389

-

介绍FPGA在线调试的一大利器—VIO2023-06-20 9971

-

Xilinx FPGA远程调试方法(一)2023-05-25 4515

-

FPGA开发在线调试和配置过程2020-11-01 5717

-

FPGA设计与调试教程说明2020-09-22 1186

-

IAR 在线调试查看各种变量的不同方法2020-03-12 15477

-

玩转Zynq连载5——基于Vivado的在线板级调试概述2019-05-24 3193

-

chipscope使用教程以及FPGA在线调试的方法2018-03-02 1350

-

FPGA实战演练逻辑篇69:基于FPGA的在线系统调试概述2015-09-02 4830

-

远程在线更新FPGA程序的方法2012-02-22 30407

-

基于SoPC的FPGA在线测试方法2011-04-18 1608

-

FPGA硬件系统的调试方法2010-02-08 3172

-

混合CPU_FPGA系统的调试方法2009-07-23 777

-

单片机的在线调试方法2009-04-22 653

全部0条评论

快来发表一下你的评论吧 !