基于ZYNQ的能源电力解决方案分享

描述

一、背景说明

近年来,“工业互联网”技术在能源电力行业得到了长足发展。随着能源互联网信息一体化、电力市场售电改革、新能源微电网与储能、智能配电终端、能源四表集抄网络、电力智能巡检等概念与政策的陆续推出,能源电力行业在基于“工业互联网”的核心指导方向下,对嵌入式解决方案在上述背景下的创新应用与升级换代的需求日益旺盛。

作为国内知名的嵌入式产品平台提供商,Tronlong凭借在嵌入式方案领域多年的深耕经验,以及对能源电力行业的创新理解,全新推出系列化的行业解决方案,涵盖TI OMAP-L138、AM335x、AM5708、AM5728、TMS320F2837x,Xilinx ZYNQ等平台,覆盖了电能采集、振动故障诊断、通信管理控制、电力电子、配电终端测控、电力智能巡检等专业技术领域。

二、方案介绍

1 方案名称

基于ZYNQ的分布式能源及微电网通信与控制单元

2 方案特点

(1) 采用Xilinx Zynq-7000 SoC高性能低功耗处理器,集成PS端单核/双核ARM Cortex-A9 + PL端Artix-7架构可编程逻辑资源;

(2) 通过配置CPU/RAM/FLASH组合,实现成本可优化/高性价比的多任务处理能力、数据本地存储、现场组网与高速通信能力;

(3) 外部可扩展LCD显示与触摸屏控制,分辨率支持2048*2048,支持1080P高清视频播放与HDMI视频输出,满足多种屏幕与人机交互的功能需求;

(4) 支持操作系统运行(Linux/RT-Linux),支持多种通信协议转换(IEC61850、DL/T645、DL/T667-1999(IEC60870-5-103))、线路潮流与控制逻辑运算、应用软件远程升级等功能算法;

(5) 可通过PL端Artix-7架构可编程逻辑资源按需扩展外部通信接口,只要资源满足,理论上无数量限制。典型应用:CAN(4路)、千兆以太网(2路)、百兆以太网(4路)、UART(12路)、SPI(5路)。

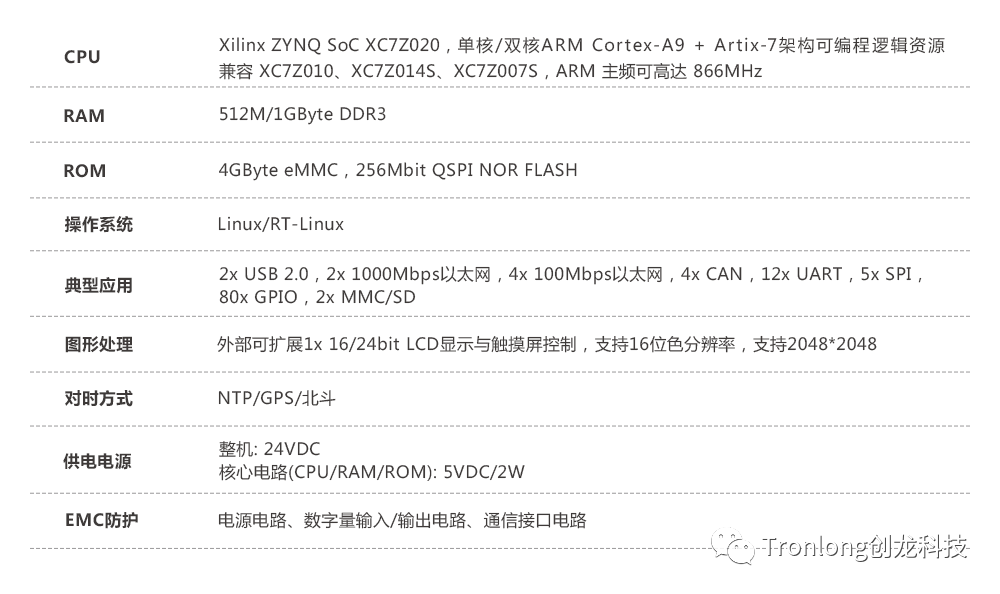

3 技术参数

图 1

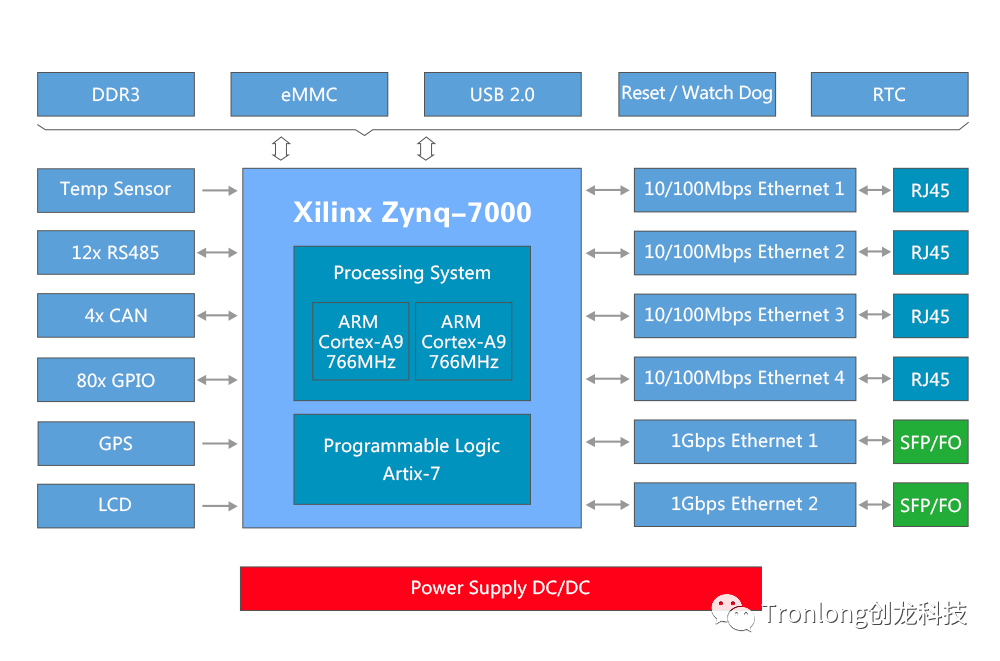

4 方案框图

图 2

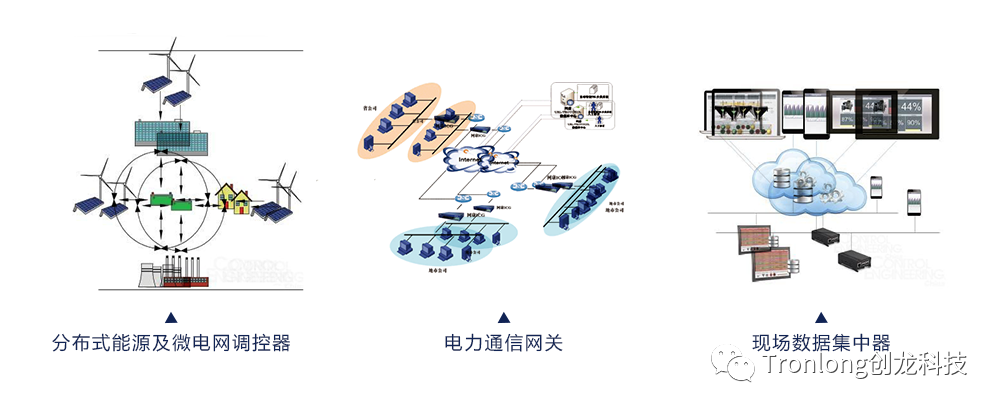

5 应用领域

可广泛用于分布式能源与负荷调控、微电网中央控制、电力通信网关、数据集中器等要求,同时接入/接出多路不同通信总线、或多种通信协议集中处理转换的应用场合。

图 3

6 AD7606经典开发案例

AD7606是最最最为经典的电力数据采集IC,在大部分电力场合应用广泛。创龙科技ZYNQ评估板TLZ7x-EasyEVM-S提供基于AD7606的AD采集与处理开发案例。下面讲解的开发案例说明基于ad7606_fft例程。

6.1 功能说明

PL端采集AD7606的8通道AD信号,采样率为200KSPS,并通过DMA IP核将数据缓存到PS端DDR中(每通道各采样4096个点),再通过FFT IP核将数据进行FFT运算,然后将FFT运算结果保存到PS端DDR中,最后通过ILA显示第一个通道的原始波形和FFT运算结果波形。

备注:由于本案例消耗逻辑资源较多,因此本案例不支持xc7z010,仅支持xc7z020。

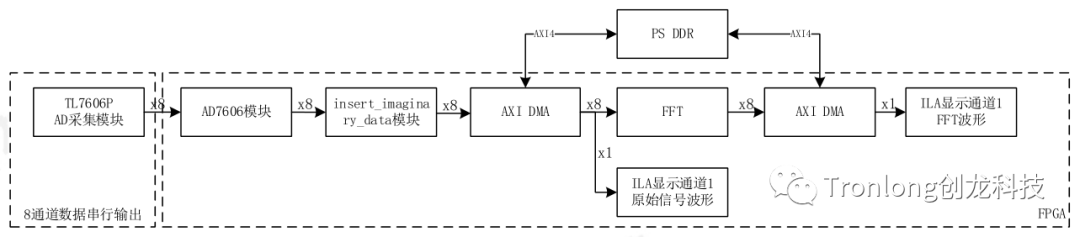

6.2 案例框图

图4

备注:x1表示1个通道的数据,x8表示8个通道。

6.3 硬件平台简介

6.3.1 TLZ7x-EasyEVM-S评估板

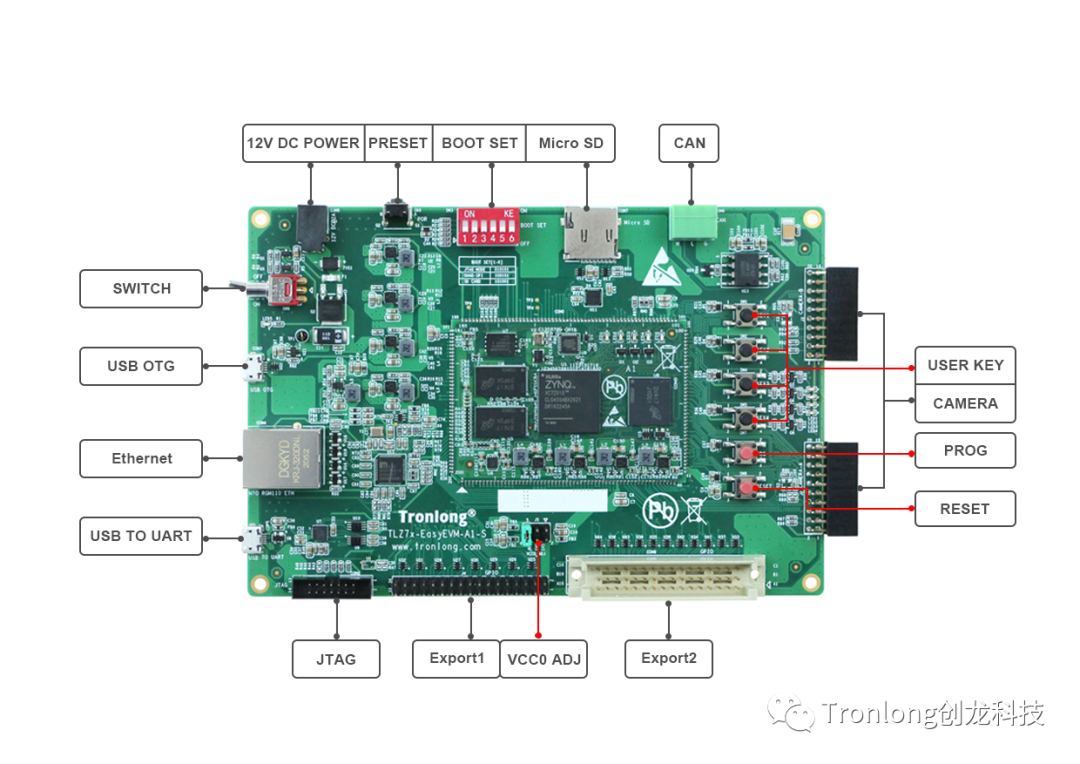

图 5

点击产品视频查看详细介绍↓↓↓

6.3.2 AD7606模块

案例使用Tronlong的TL7606P AD模块。

点击图片/图注即可了解产品更多资料↓

图 6

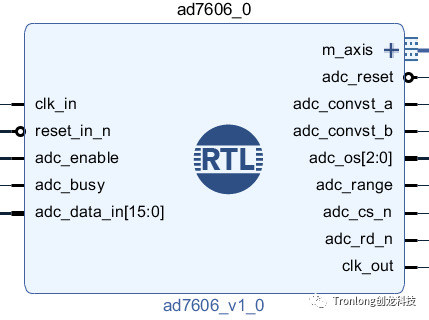

图 7

模块功能说明:

该模块控制AD7606对8通道AD信号按200K采样率进行采集,并将数据通过AXI4-Stream接口进行发送。

6.4 案例测试

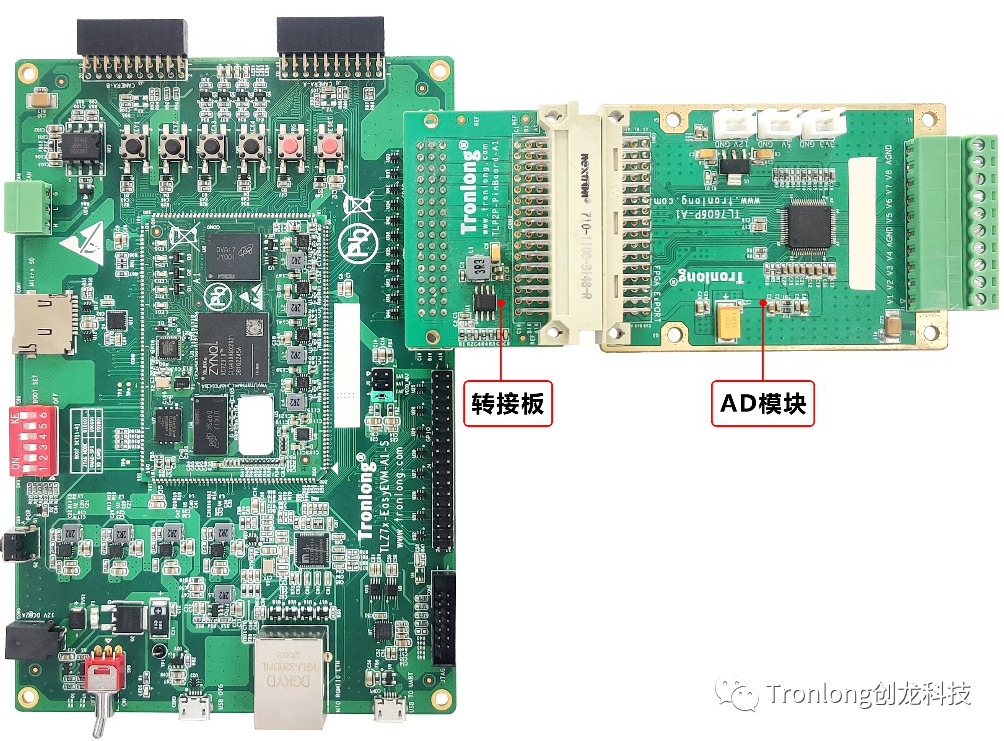

将TLP2P-PinBoard转接板接到评估板CON8接口,再将AD模块TL7606P与转接板连接。

图 8

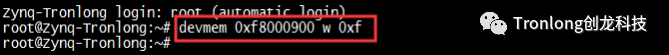

进入评估板文件系统,执行如下命令配置PS-PL电平转换寄存器。

Target# devmem 0xf8000900 w 0xf

图 9

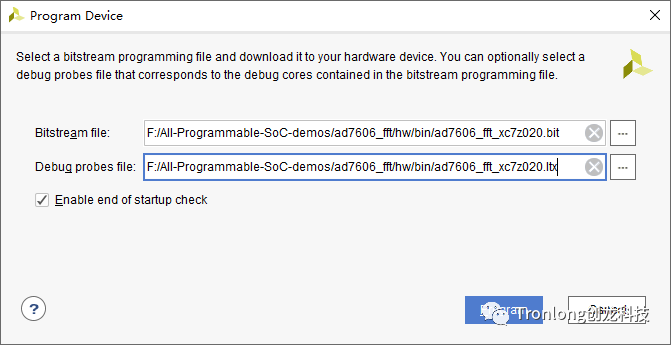

使用下载器加载PL端程序以及和PL端程序同目录下的.ltx文件。

图 10

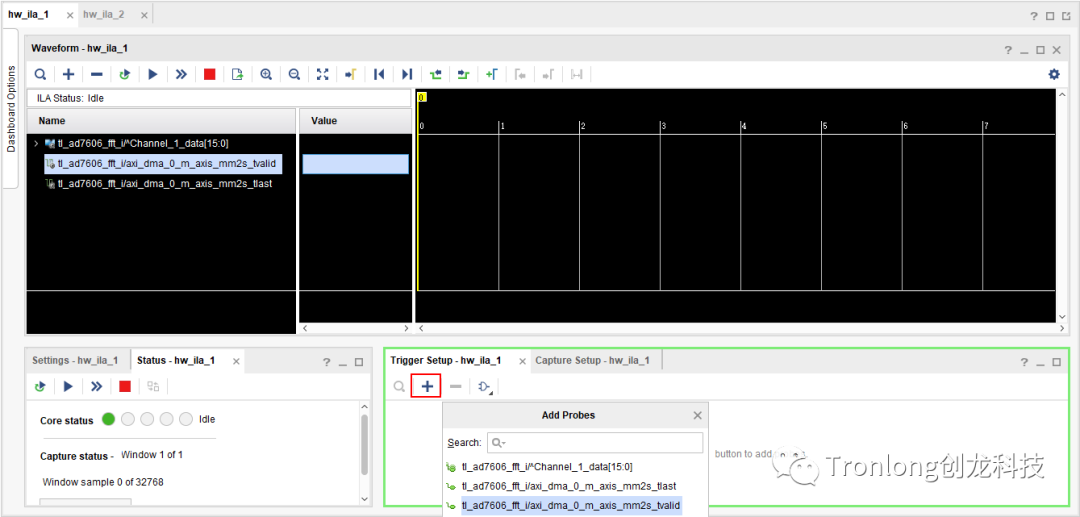

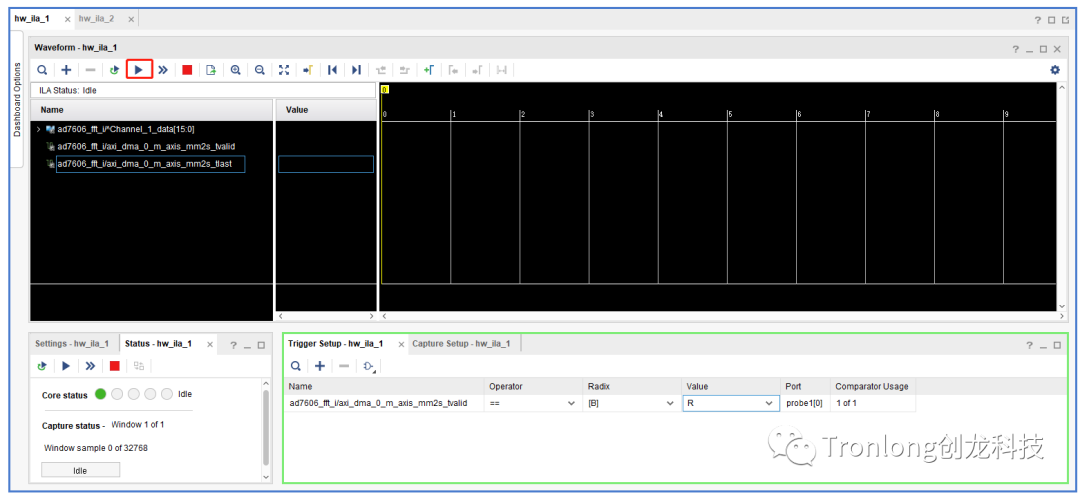

在ila_1的Trigger Setup窗口点击按钮,双击axi_dma_0_m_axis_mm2s_tvalid将其添加为触发信号。

图 11

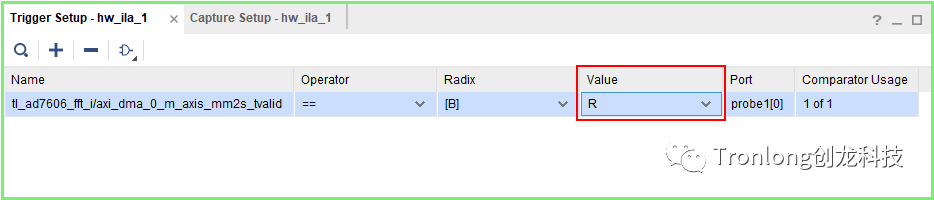

将Value的值改成R,设置为上升沿触发。

图 12

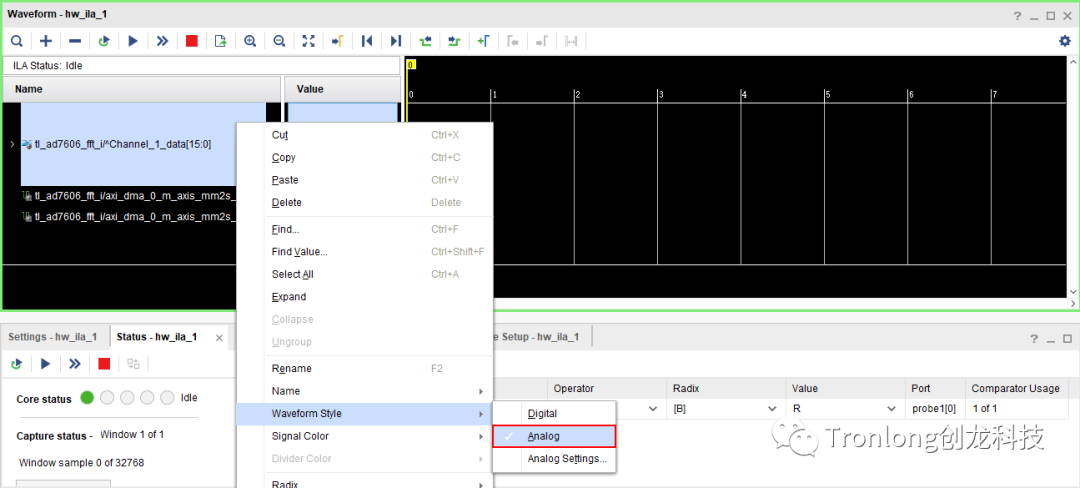

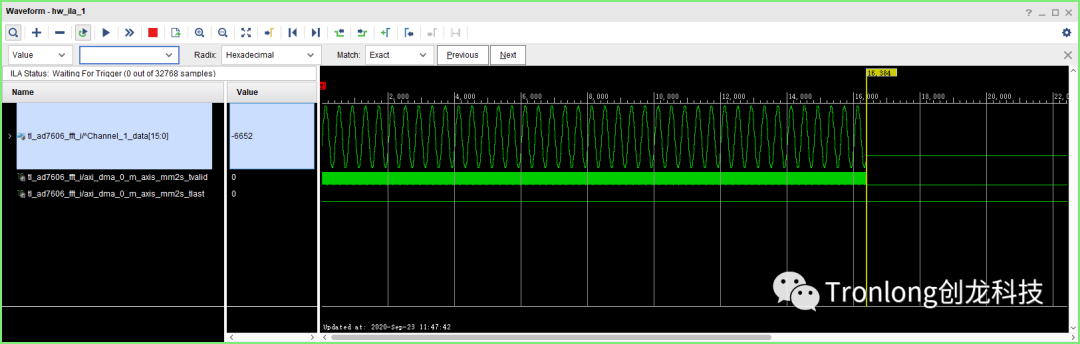

右击Channel_1_data[15:0],点击“Waveform Style -> Analog”将通道1的原始信号设置为模拟波形。

图 13

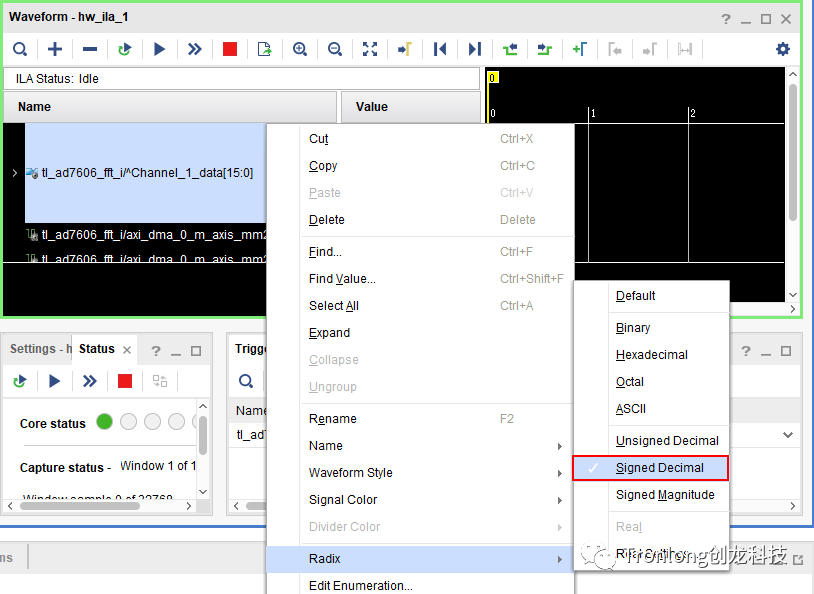

右击Channel_1_data[15:0],点击“Radix -> Signed Decimal”设置数据为有符号类型。

图 14

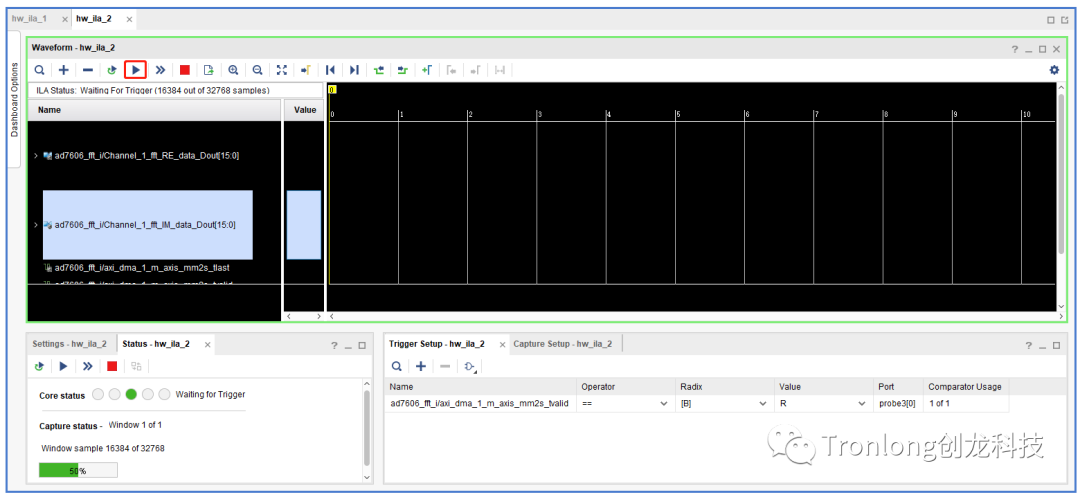

参考上面的步骤,在ila_2将axi_dma_1_m_axis_mm2s_tvalid添加为触发信号,设置为上升沿触发,将FFT IP核输出数据的实部和虚部信号分别设置为模拟波形,并设数据为有符号类型。

图 15

图 16

使用信号发生源向TL7606P模块的8个通道分别输入信号,本案例测试的输入信号是频率为2KHz、峰峰值为3.3Vpp的正弦波。

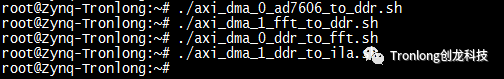

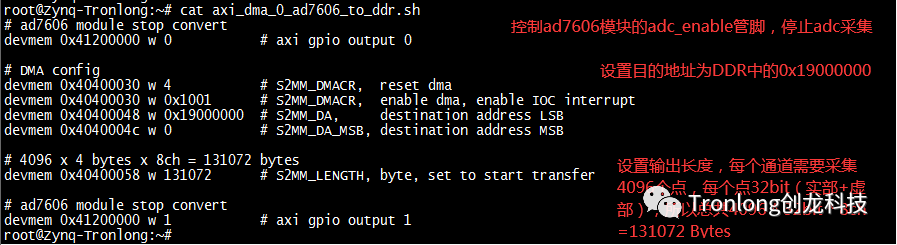

将案例“sw\linux_system\image\”目录下所有脚本文件拷贝至评估板文件系统。执行如下命令使能axi_dma_0的S2MM通道,将数据采集到PS端DDR中。

Target# ./axi_dma_0_ad7606_to_ddr.sh

执行如下命令使能axi_dma_1的S2MM通道(FFT转换后数据保存到PS端DDR),等待FFT IP核工作。

Target# ./axi_dma_1_fft_to_ddr.sh

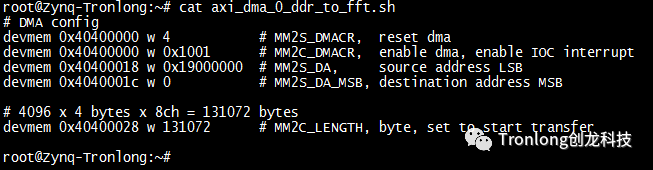

执行如下命令使能axi_dma_0的MM2S通道,把原始数据从DDR送到FFT IP核。

Target# ./axi_dma_0_ddr_to_fft.sh

执行如下命令使能axi_dma_1的MM2S通道,把FFT转换后的数据从DDR送到ILA显示。

Target# ./axi_dma_1_ddr_to_ila.sh

图 17

axi_dma_0_ad7606_to_ddr.sh

配置axi_dma_0的S2MM通道,将数据传输到DDR。

图 18

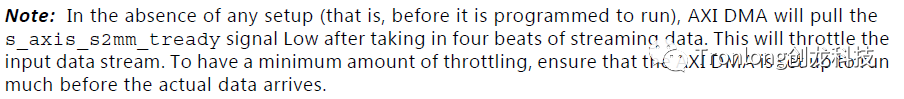

配置好DMA后,配置axi gpio输出1,设置adc_enable为1,使能ADC转换。需确保DMA已配置好,再使能ADC转换并进行数据传输。

图 19

axi_dma_0_ddr_to_fft.sh

配置axi_dma_0的MM2S通道,将DDR中的数据通过AXI4-Stream发送给FFT IP核。

图 20

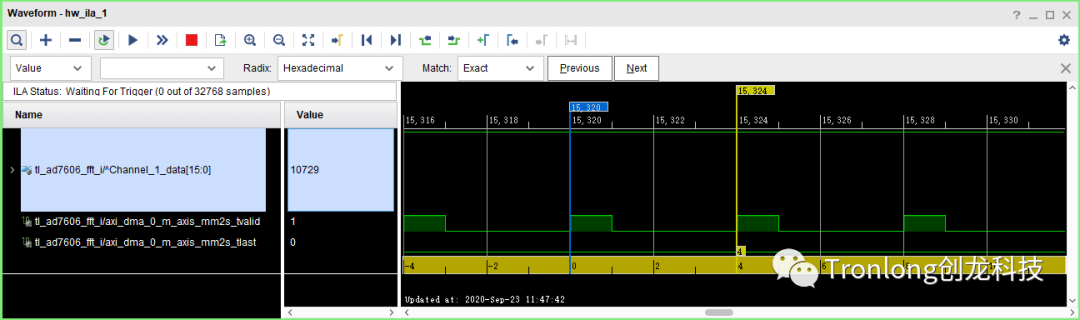

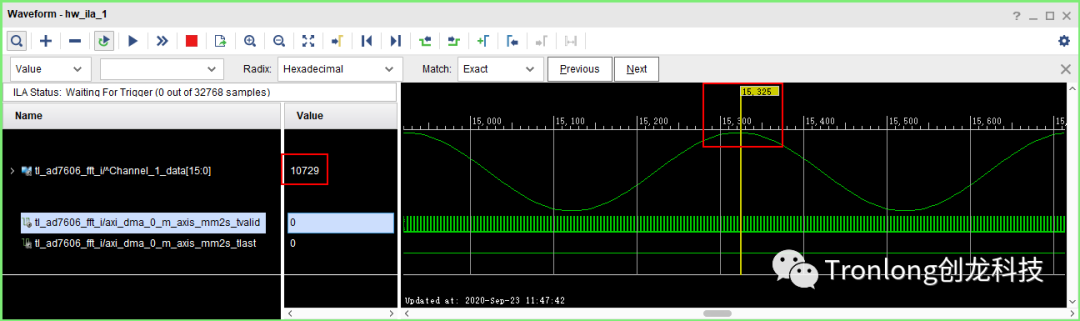

ila_1原始波形

输入信号是频率为2KHz、峰峰值为3.3Vpp(电压幅值为1.65V)的正弦波。一共4096个采样点,每个采样点4个时钟周期,即4096=16384/4。

图 21

图 22

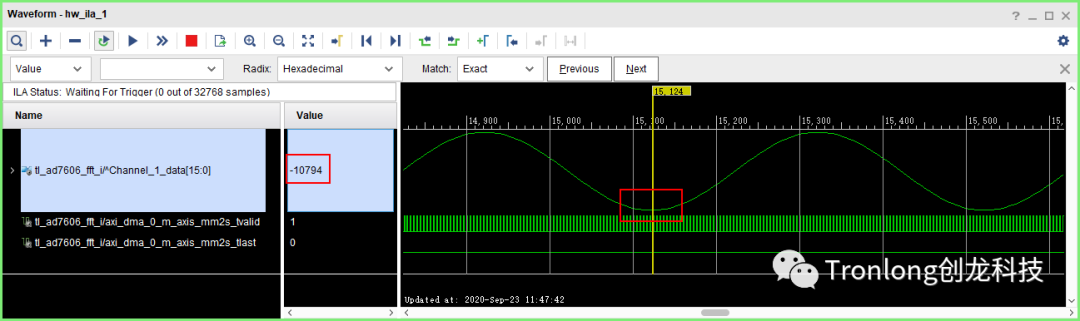

波峰值为+10729,波谷值为-10794,峰峰值=(10729 + 10794)/(2^16)x10V≈3.2841V,采样范围为±5V。

图 23 波峰值

图 24 波谷值

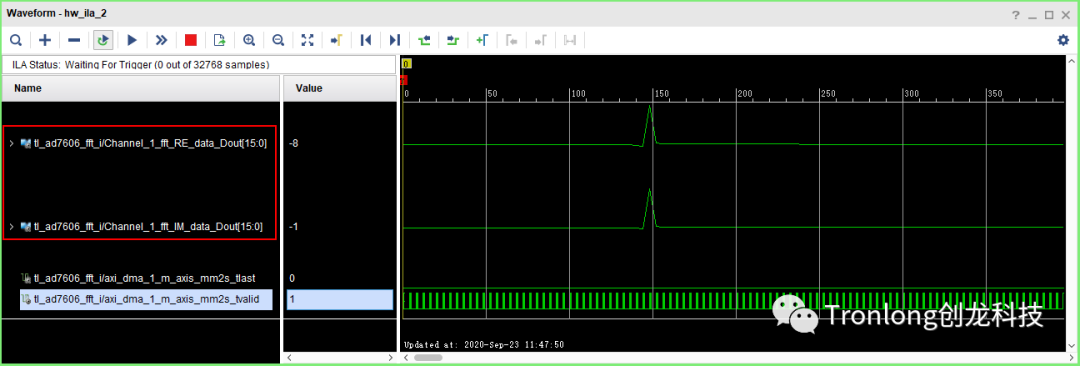

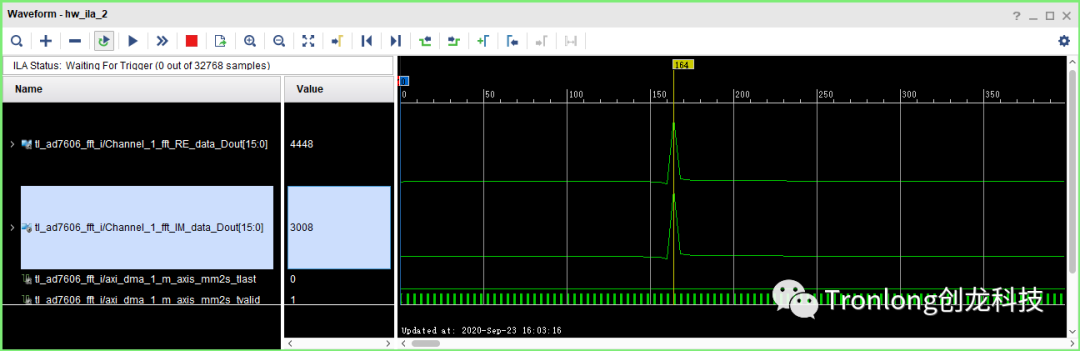

Ila_2 FFT波形

Channel_1_fft_IM_Dout为虚部,Channel_1_fft_RE_Dout为实部。

图 25

频率计算

FFT变换点数N=4096,AD采样率Fs为200KSPS。某点n所表示的频率Fn=(n-1)*(Fs/N)(n>=1)。当n=1时,Fn为0,由于第一点表示的是直流分量,因此频率为0,幅值也为0,该正弦波无直流分量。

从下图可知,在第164个周期(即第42个采样点)处出现信号,则信号频率Fn=(42-1)*(Fs/N)=41*200KHz/4096=2001.95Hz,与原始信号频率2KHz基本一致。

图 26

幅值(波峰值)计算

某个点的幅值An=(根号(实部^2 + 虚部^2))*压缩倍数/(N/2),则信号幅值An=(根号(4448^2 + 3008^2))x4096/4096x2≈10739.23,信号电压幅值=10739.23/(2^16/2)x5V≈1.64V,与原始信号电压幅值1.65V基本一致。

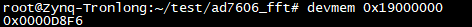

查看原始数据

每个采样点32bit(包括实部和虚部),每个通道的数据的地址依次递增,从地址0x19000000开始。

Target# devmem 0x19000000 //查看V1通道原始数据

Target# devmem 0x19000004 //查看V2通道原始数据

Target# devmem 0x19000008 //查看V3通道原始数据

Target# devmem 0x1900000c //查看V4通道原始数据

Target# devmem 0x19000010 //查看V5通道原始数据

Target# devmem 0x19000014 //查看V6通道原始数据

Target# devmem 0x19000018 //查看V7通道原始数据

Target# devmem 0x1900001c //查看V8通道原始数据

图 27 查看V1通道原始数据

查看FFT数据

每个采样点32bit(包括实部和虚部),每个通道的数据的地址依次递增,从地址0x19100000开始。

Target# devmem 0x19100000 //查看V1通道FFT数据

Target# devmem 0x19100004 //查看V2通道FFT数据

Target# devmem 0x19100008 //查看V3通道FFT数据

Target# devmem 0x1910000c //查看V4通道FFT数据

Target# devmem 0x19100010 //查看V5通道FFT数据

Target# devmem 0x19100014 //查看V6通道FFT数据

Target# devmem 0x19100018 //查看V7通道FFT数据

Target# devmem 0x1910001c //查看V8通道FFT数据

图 28 查看V1通道FFT数据

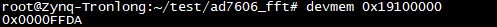

三、更多方案

图 29

-

解决方案丨EasyGo新能源系统实时仿真应用2024-10-18 1360

-

用于Xilinx FPGA Zynq7的电源解决方案2022-09-05 978

-

基于Xilinx Zynq-7020/7010实现的双系统解决方案2022-04-20 4238

-

基于ZYNQ的能源电力解决方案2021-11-02 2450

-

AnDAPT为Xilinx Zynq平台FPGA和SoC设备推出完整电源解决方案2021-06-01 3550

-

电力计量的固态解决方案2021-05-25 694

-

能源解决方案2021-05-15 701

-

备份电力解决方案2021-05-12 753

-

Xilinx FPGA Zynq 7全套电源解决方案包括BOM及原理图2018-09-11 4278

-

2016年拉丁美洲(智利)国际电力能源展览会2015-09-16 1681

-

电池电力存储解决方案的机遇2015-05-15 4727

-

用于 Xilinx FPGA Zynq 7 的电源解决方案2015-04-14 3971

-

2.4G无线电力测温解决方案2012-05-18 4960

-

微型能源采集技术的关键应用问题及解决方案2011-09-29 3130

全部0条评论

快来发表一下你的评论吧 !