Allegro小技巧 | 如何设置差分线能够有效减少报错

描述

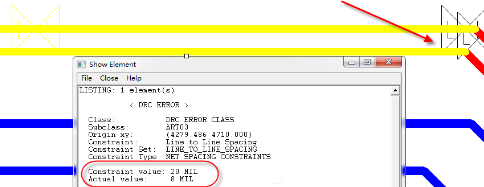

在PCB设计过程中,差分信号是比较重要的信号,一般设置差分信号到其它信号的间距是20mil,但是设置完差分信号到其它信号的间距之后,差分对内PN之间不满足20mil的间距,会报错,如1所示:

图1 差分信号对内报错示意图

如图2所示,差分信号到其它信号的间距是20mil,但是差分按照阻抗线宽走线,间距是8mil,所以出现DRC的错误。

本文向大家介绍如何将所有的差分线的设置到其它信号的间距是20mil并满足自身的阻抗间距不报错,具体操作步骤如下:

01规则设置

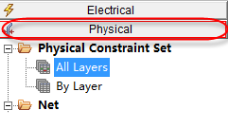

打开规则管理器,执行菜单命令Setup-Constrains,在下拉菜单中选择Constraint Manager,进行规则设置,左侧选择Physical Constraint Set,如图2所示,点击all layers;

图2 进入物理规则设置示意图

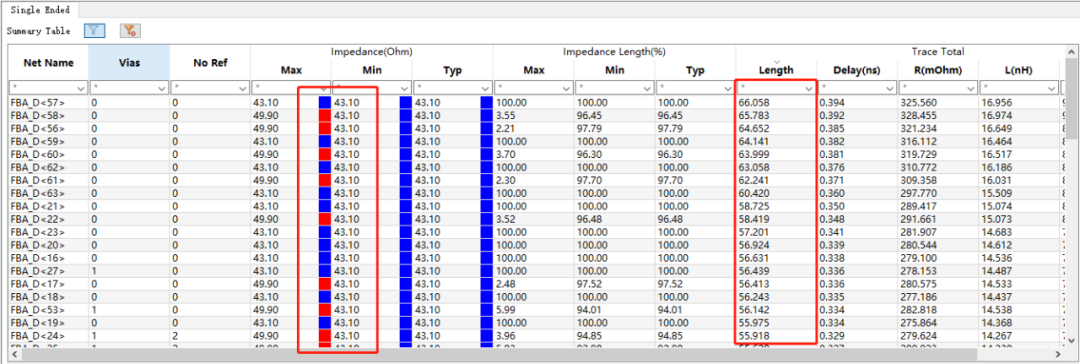

02设置差分默认间距

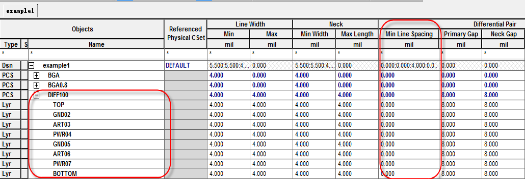

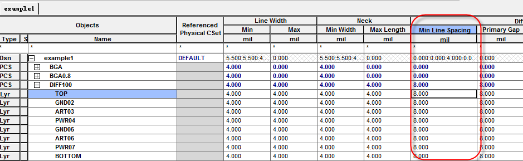

差分走线设置的规则,是DIFF100的规则,在差分属性的Min Line Spacing最小间距,目前是0,如图3所示,我们将其设置为差分默认的间距8mil,如图4所示;

图3 默认差分间距设置示意图

图4 差分最小间距设置示意图

03PCB界面

设置完成以后,回到PCB界面,如图5所示,差分线已经不会报错了,对内满足阻抗要求,对外到其它信号满足20mil间距。

图5 差分信号不报错示意图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- PCB设计

-

差分线 画蛇形线2012-07-11 8795

-

差分线绕线方法比较2014-04-15 4464

-

PADS PCB功能使用技巧系列 —— 如何走差分线?2015-01-12 38821

-

Allegro 差分对出线方式可以设置吗?2016-06-29 6631

-

PADS PCB的差分线优势2019-05-20 3078

-

请问走差分线可以设置等长吗?2019-07-31 4140

-

如何设置组间及差分线与其他信号之间的间距?2019-09-10 20692

-

如何设置allegro差分线单走线?2019-09-19 9801

-

请问差分线过孔间距可以设置吗?2019-09-25 6753

-

AD19:如何设置 差分线对与单端线之间的线间距?2019-11-19 9891

-

差分线的优势和走线要求2020-10-29 3472

-

教你设置Allegro差分线2010-06-24 34776

-

allegro_差分线等长设置2016-02-22 2336

-

AD中关于差分线的设置和走线的方法详细资料说明2019-02-11 5288

-

差分线pcb走线原则2023-12-07 8138

全部0条评论

快来发表一下你的评论吧 !