虹科方案 | 网管+冗余,虹科MRS交换机IP核实现具有冗余的以太网功能!

描述

IP核(Intellectual Property core)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片,从而帮助开发人员减少工作量,并加快产品上市。

虹科1G 网管冗余交换机IP核

HongKe 1G Managed Redundant Switch IP Core /

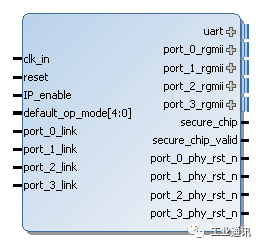

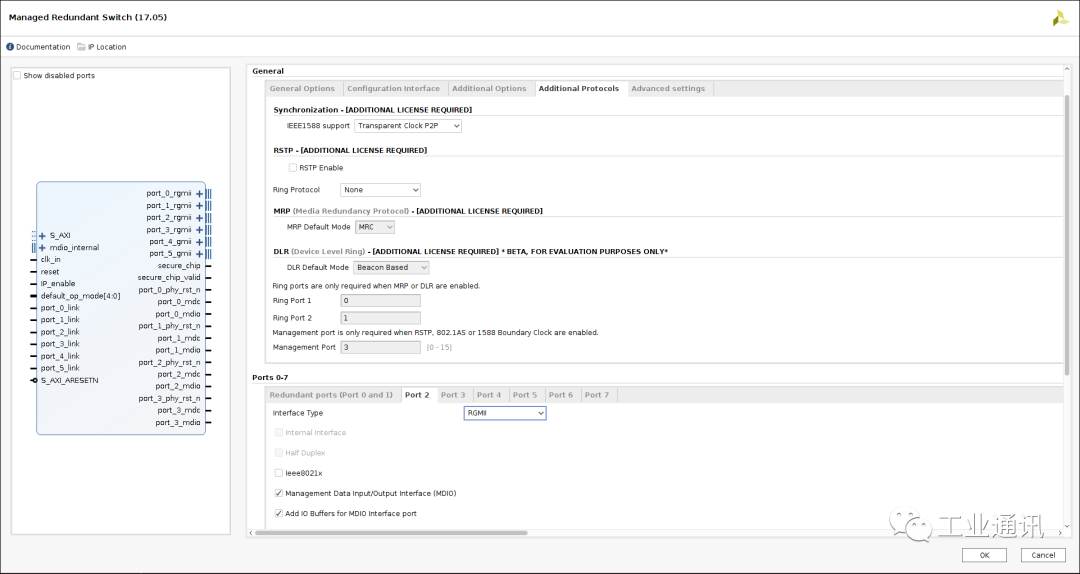

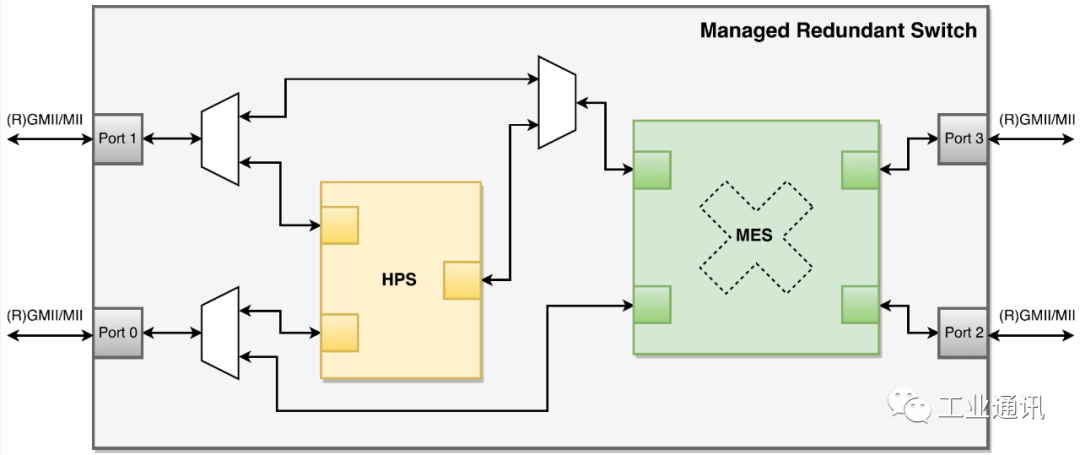

网管冗余交换机IP核(MRS)是虹科HSR-PRP交换机(HPS)和网管以太网交换机(MES)IP核的组合,具有冗余的以太网交换功能。MES模块是一个无阻塞交叉开关矩阵,允许在所有端口之间进行连续传输。它实施存储转发的交换方法,以完全满足以太网标准策略关于转发每个帧之前校验帧的完整性。另一方面,HPS模块在所需的端口中引入了HSR和PRP冗余功能。HSR 的切换方法是 Cut-Through(直通)。因此,MES和HPS的组合提供了最高的性能和与标准的最大兼容性。

虹科网管冗余交换机可以利用新的 Xilinx Vivado 工具轻松集成到用户的FPGA 设计中,该工具允许在图形用户界面中使用 IP 内核并以简单的方式配置 IP 参数。

以下Xilinx FPGA系列可以支持虹科MRS IP核 :

6 系列(Spartan、Virtex)

7 系列(Zynq、Spartan、Artix、Kintex、Virtex)

超大规模(Kintex、Virtex)

Ultrascale+(Zynq MPSoC、Kintex、Virtex)

虹科

用于Xilinx Vivado工具的

1G网管冗余交换机 /

虹科网管冗余交换机IP核的主要功能

HongKe 1G MRS IP Core Key Features

1

# 接口

全双工10/100/1000 Mbps以太网接口

半双工10/100 Mbps以太网接口

全双工10 Gbps以太网接口(开发中)

可配置的3至16个以太网端口

MII/GMII/RGMII/SGMII/QSGMII物理层设备(PHY)接口

每个端口支持不同的数据速率

铜缆和光纤介质接口:10/100/1000Base-T,100Base-FX,1000Base-X

2

# 交换

具有自动MAC地址学习和老化的动态MAC表(最多2048个条目)

静态MAC表(最多2048个条目)

巨型帧管理

基于以太网的交换

入口端口镜像

广播/多播风暴防护

每端口速率限制(广播、多播和单播流量)

3

# 流通管理

多播帧过滤

交换端口掩码:用户定义的帧到具体端口的转发

基于端口的VLAN支持

服务质量(QoS):优先级(PCP-802.1p,DSCP TOS,以太类型)

IEEE 802.1X EAPOL硬件处理

DSA(分布式交换体系结构)标记:使用DSA的理想情况是以太网交换机支持“交换机标签”

4

# 组态

MDIO,UART,AXI4-Lite或CoE(以太网配置)管理接口

以太网配置(COE):通过连接到CPU的同一以太网链路全面访问内部寄存器

购买IP核时提供驱动程序

5

# 冗余协议

RSTP(需要软件堆栈)

MRP(不需要软件堆栈)

DLR(不需要软件堆栈)

HSR(不需要软件堆栈)

PRP(不需要软件堆栈)

虹科网管冗余交换机IP核

虹科工业控制团队

-

网管型与非网管型工业以太网交换机有何区别?广州邮科为你解析2026-01-22 299

-

虹科应用 增强型以太网交换机:如何实现同IP控制的高效网络管理?2024-08-16 1186

-

虹科案例丨VLAN不再难懂:一台转换器+交换机轻松解锁VLAN配置2024-05-24 1259

-

OT网络中网管型工业以太网交换机的优势2023-04-19 2444

-

虹科方案 | 虹科UES IP核——用最少的资源,解决最大的吞吐量!2022-04-14 1599

-

虹科方案 | 强大而灵活的虹科10G网管以太网交换机IP核,开发交换机的好帮手!2022-03-10 2530

-

虹科TSN(时间敏感网络)交换机,无缝实施确定性以太网的可靠助手!2021-10-14 3282

-

工业级以太网交换机在应用上具有哪些优越特性2020-12-08 2728

-

5电口环网冗余工业以太网交换机案例分享2018-11-14 4184

-

5电口环网冗余工业以太网交换机2018-11-12 2798

-

MOXA推出16+2G口千兆网管型冗余工业以太网交换机--E2009-12-24 1693

全部0条评论

快来发表一下你的评论吧 !