基于SoPC的双边带调幅波系统设计

FPGA/ASIC技术

描述

调幅就是用低频调制信号去控制高频波信号的振幅。经过振幅调制的高频载波称为调幅波,它保持着高频载波的频率特性,但包络线的形状和信号波形相似。产生调幅波的主要方法是利用波形合成技术。目前波形合成技术主要有两种通用的方法,一种是使用专用的数字频率合成DDS芯片,另一种是基于SoPC的解决方案。专用DDS芯片的功能比较多,但控制方式固定、不灵活。而在FPGA芯片上利用DDS信号可以很容易地实现各种比较复杂的调频、调相和调幅信号,具有良好的实用性。

1 DSB的基本原理与调制模型

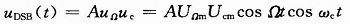

当调制信号为单频信号时,若设调制信号为uΩ(t)=UΩmcosΩt,载波信号为uc(t)=Ucmcosωct,通常要求ωc>>Ω,则双边带调幅信号的数学表示式为:

式中:A为乘积电路的电路常数;AUΩmUcmcosΩt为双边带调幅信号的振幅,它与调制信号成正比。

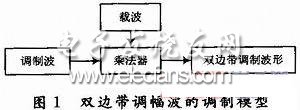

双边带调幅信号由图1所示框图来实现,其核心部分在于实现调制信号与载波相乘。

2 系统具体设计

2.1 硬件电路

2.1.1 DDS信号源

双边带调幅波的调制模型中的载波和调制波是通过DDS信号源实现的。其DDS结构原理图如图2所示,DDS是由频率合成器、相位累加器、波形ROM、D/A转换器和低通滤波器LPF构成。

2.1.2 硬件原理图

系统顶层设计图如图3所示。图中加法器通过QuartesⅡ软件直接用VHDL语言编写,波形ROM查找表则利用Matlab软件生成。

低频DDS中主要用的是32位加法器、8×8的ROM查找表;其中第一个32位加法器完成对频率控制字的累加,第二个32位加法器则用于相位控制。高频DDS中主要用的是8位加法器、8×8的ROM查找表;其中8位加法器完成对频率控制字的累加。

2.2 软件设计

系统顶层设计的核心是由可裁剪的Nios软核与可存储正弦波形信号的DDS模块(如图3)组成。Nios软核接收到不同按键信息,根据按键信息设置不同的DDS输出波形参数(载波相位、频率与调制波相位、频率),经由PIO口将被选择的信号传输给DAC芯片。其程序流程图如图4所示,选择程序部分如下:

3 测量结果及分析

不断地调整输入频率控制字PWORD,PWORD1,可以得到下面一组仿真结果(见图5)。这组图形中,时钟频率fc=16 384 Hz。图5(a)是高频DDS的输出波形,频率为6 250 Hz;图5(b)是低频DDS的输出波形,频率为3.9 Hz;图5(c)是在高频fWORD1=6 250 Hz,低频fWORD=3.9 Hz,相位M=13时的双边带调幅波形;图5(d)是在高频fWORD1=6 250 Hz,低频fWORD=3.9 Hz,相位M=101时的双边带调幅波形;图5(e)是在高频fWORD1=6 250 Hz,低频fWORD=12.5 Hz,相位M=101时的双边带调幅波形。

从图5中可以很轻易地看出几点:

(1)调幅后的波形的包络(见图5(c))是低频正弦波(见图5(b))周期的50%;

(2)低频调制波的相位对调幅后的波形的包络长度没有影响(见图5(c)和图5(d));

(3)低频调制波的相位对调幅后的波形的幅度有影响,当它变大时,调幅波形的幅度也变大(见图5(c)和图5(d)),但并不是线性变化;

(4)低频DDS的输入频率会改变调幅波形的包络长度,当低频DDS的输入频率变大即周期变小时,调幅波形的包络长度也变小(见图5(d)和图5(e));

(5)低频DDS的输入频率不会改变调幅波的幅度,当低频DDS的输入频率变大即周期变小时,调幅波形的幅度没有发生明显的变化(见图5(d)和图5(e))。

综上所述,这些均符合双边带调制波形的特征,完成了设计要求。

4 结语

本文介绍了一种基于SoPC的双边带调幅波系统设计方案,阐述了整个设计流程,并对设计结果进行了仿真分析。利用SoPC设计双边带调幅波系统,方法简单、灵活、参数便于修改,具有良好的实用性。

-

单边带调制和双边带调制的区别2024-08-14 9171

-

双边带调幅波为什么要用相敏检波电路检波呢?2023-05-05 1268

-

NI Multisim 10经典教程分享--抑制载波双边带调幅(DSB/SC AM)解调电路2023-02-16 4052

-

[10.2.2]--抑制载波的双边带调幅波(DSB波)学习电子知识 2022-11-25

-

单边带调幅对讲机设计2021-03-18 1745

-

双边带调制原理_双边带调制的优缺点2020-03-11 25371

-

一文看懂单边带和双边带的波形及区别2018-03-13 154656

-

模拟乘法器实现调幅电路的设计2017-02-18 5751

-

双边带调制2010-05-18 4715

-

10m双边带发射机2009-10-10 1046

-

双边带调制波形2009-07-31 1957

-

双边带AM调制器电路2009-03-20 1144

全部0条评论

快来发表一下你的评论吧 !