On chip ESD和EOS保护设计

描述

IC片上保护设计对EOS的影响

全面的方法可以减少与EOS相关的故障

通常理解的是,芯片上ESD保护是必不可少的,以满足人体模型(HBM)和充电装置模型产品合格(CDM)ESD应力的可靠性要求。由工业委员会确定的ESD目标水平的当前最低安全水平(在IC行业中已广为接受),对于HBM为1kV,对于CDM为250V,在成熟技术中具有良好的ESD设计实践,可以提供更高的水平以确保更高的利润。

尽管这是理想的,但在某些问题上,过高的ESD设计水平可能会导致设计良好的ESD电路在更长的时间内承受过电流,从而使其更易遭受持续时间短暂的瞬态感应EOS事件和意外损坏。同样,如果不遵守适当的规则,处理闩锁事件中的过电流的设计也会对EOS产生一些影响。

本文简要回顾了这些问题,以说明强大的ESD保护不能保证IC设计免受意外EOS影响。它还总结了各种IC设计应用和相应的ESD设计方法,这些方法应说明任何不必要的EOS损坏情况。

ESD设计窗口

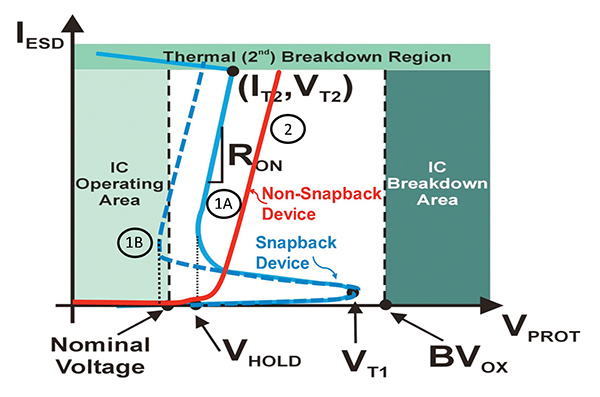

首先,必须确保ESD保护设计严格用于实现能够保护所需的组件级HBM和CDM目标级别,同时又不对与栅极氧化物相关的功能和/或IC引脚可靠性产生任何负面影响的最佳电路,结或互连损坏。ESD工作区称为“设计窗口”,如图1所示。

图1:ESD保护策略的典型设计窗口

任何ESD设计均受IC工作区域,IC可靠性区域以及保护钳定义的热效应的限制。因此,设计人员选择合适的ESD器件,电路器件,并包括可以实现该目标的任何限制电阻。保护设备的触发电压(V t1)定义了它设计为导通的电平;触发后的保持电压(V Hold)是指应高于施加电压的钳位电平。最后,I t2是指ESD故障电流水平。图1中常用保护设备的选择是:

如蓝色曲线(1A或1B)所示,NMOS晶体管在触发点V t1处进入双极击穿(npn),并迅速恢复为称为V Hold的保持电压,并保护高达故障电流I ESD对应于ESD目标水平。(I t2,V t2)是指保护设备可能烧坏的散热点,因此该I t2必须大于I ESD目标电流水平(例如,目标1.5 kV HBM的电流为1 Amp)。如果保护设备的导通电阻(R on)太高,则V t2也可能达到可靠性电压极限。钳位电路必须有效触发,以使其电压累积不超过栅极氧化层击穿电压(BV ox)或晶体管击穿电压。晶体管的V Hold经过设计,使其具有一定的工作电压裕度,如曲线1A所示。相反,在具有V Hold的快速恢复装置小于工作电压(曲线1B)的情况下,存在EOS损坏的风险。

图1中的第二个选择也可以是非突跳设计,其中钳位器调谐并传导电流,如红色曲线2所示。有两种器件和电路技术都可以应用于传统的突跳器件来产生这种情况。行为。

另一个选择是pnpn器件,它以相似的V t1触发,但具有更低的V Hold(等于或低于曲线1B所示的V Hold,因此要小心,以免在电路工作期间意外触发)。如果将此pnpn器件放置在VDD引脚上,则非常危险,因为很可能会意外或意外触发。本质上,ESD设计人员仅专注于ESD电池和通过组件的保护路径。具有较低的V Hold的ESD优势会带来EOS风险,这是一个折衷方案:如果在正常操作期间触发ESD电池,则存在无法关闭ESD电池并会传导大量电流的高风险。持续时间比设计的时间更长。

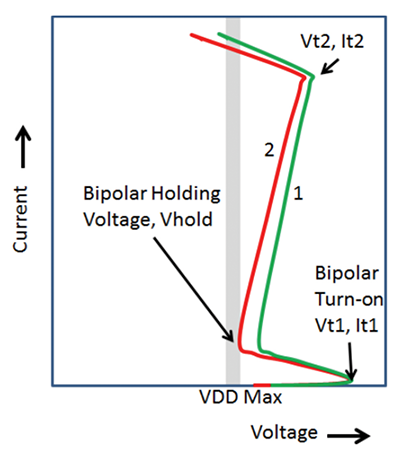

尽管通常ESD保护的设计并非旨在防止EOS事件,但根据特定的应用和操作,上述器件的ESD保护的IC 设计风格确实可以影响EOS损坏导致的故障率。环境。图2说明了两个不同的骤回设备,其中设备1与设备2的设计相比相对安全。设备2的EOS风险增加是由于V Hold参数低于最大允许VDD。雷卯电子可以提供ON CHIP ESD design 服务。

图2:避免EOS损坏的快照设计

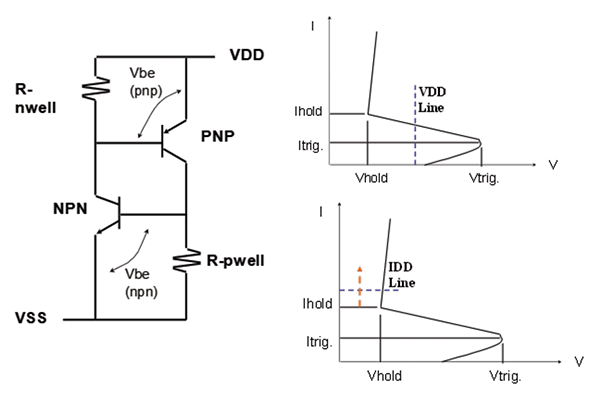

闩锁和EOS

如前所述,如果不采取适当的预防措施,pnpn设备对于EOS可能会出现更多问题。图3说明了这种容易产生EOS的ESD设计操作。此类设备的V Hold必须高于V dd或I Hold(将其保持在闩锁模式所需的电流)要大于电源Idd电流。有一些设计方法可以实现此目的,以防止意外闩锁导致EOS损坏。在保护设备类型错误(例如电源引脚上的pnpn)的情况下,已经观察到EOS损坏。

图3:PNPN ESD保护设备的设计操作显示了EOS的脆弱性

即使设计人员真诚地进行了照顾,但如果OEM厂商通常没有就应用中的实际电压尖峰水平向他们进行咨询,也会出现问题。因此,在某些意外情况下,可能会导致EOS损坏。此外,此外,某些涉及触发电压和保持电压的设计风格可能会对整个系统产生更大的影响。因此,设计者只能防止客户指定的应用程序需求引起的那些事件。

在根据JEDEC闩锁规范(JESD78)进行闩锁可靠性测试期间,如果不了解某些条件,则IO引脚上可能会发生EOS损坏。如果IO引脚具有高输入阻抗,则电压(在注入电流以测试闩锁时)可能会积聚得足够高,从而在达到测试所需的闩锁极限之前,在意想不到的路径上造成结击穿损坏。 这会造成不必要的EOS损坏,从而引起一些客户误解。 在即将发布的文档修订版中,对JEDECJESD78测试方法进行了更好的描述,以避免这种错误的评估。

高速设计

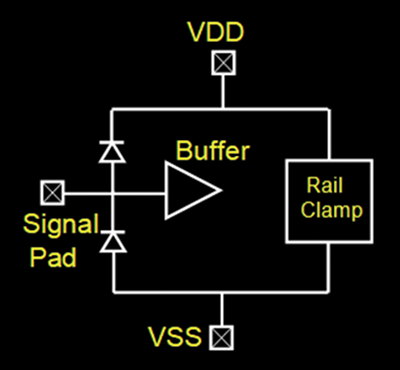

代替在IO引脚上钳位器件的方法,用于大型数字IO环组的一种常用设计风格(参见图4)是“轨钳位”VDD保护设备,其中MOS保护设备在“正常工作”线性和饱和区域中工作在ESD事件传导期间,器件不会发生双极性击穿。它包括一个有源MOSFET作为VDD和VSS之间的钳位器件,其特性如图1中的红色曲线所示。即使在这些情况下,如果设计不能正确解决某些情况,EOS损坏也可能成为问题。例如,在正常应用期间,电源上出现的IO转换引起的“dv/ dt”压摆率可能会导致该设备进入电流传导模式。

图4:用于ESD保护策略的非快速回弹钳

第二个考虑因素是需要先进技术的高速应用程序的数量不断增加。通常,调整工艺技术以减轻ESD设计对EOS的意外损坏是不可取的,因为该技术针对IC应用,速度性能和产品规格需求进行了优化。ESD设计在技术表征期间进行,并在技术成熟后逐渐成熟。因此,由ESD设计人员或IO设计人员(有时由两者)解决由特定ESD保护设计方法引起的任何EOS问题。

片上系统设计

另一方面来自使用多个电源电压电平的片上系统(SOC)设计。在这些情况下,电源排序通常会成为任何意外触发的内部二极管的问题。这些二极管会在顺序转换期间消耗大量功率,从而导致EOS损坏。芯片(尤其是具有多个电源域的SoC)的设计越复杂,存在意想不到的寄生路径的可能性就越大。除非遵循仔细的设计技术,否则可能会导致EOS损坏的退货。因此,SOCESD保护设计必须考虑到这一点。

高压与低压ESD设计

有人可能会认为,施加电压越低,器件对ESD和EOS问题的敏感性就越高。相反,如果遵循谨慎的策略来保护薄栅极氧化物和晶体管较低的结击穿电压,则可以安全地为ESD设计低压器件。唯一的例外可能是由于高速应用而降低了ESD目标水平。一旦设计用于ESD,它们的EOS问题就相对不那么普遍了。

另一方面,高压应用经常使用SCR型保护器件。尽管这些器件提供更高的ESD保护级别,但同时它们的设计窗口通常更窄(最大工作电压和IC击穿区域之间的开销较小),并且几乎总是使V Hold远低于最大工作电压。在非ESD条件下触发这些设备可能会导致EOS事件。

要考虑的另一方面是,与使用低压设备的保护设计相比,使用高压设备的保护设计在开启模式下具有更高的功耗。这样,当设备无法保护或ESD设备本身发生故障时,可利用更多的能量在故障区域造成材料损坏。EOS损坏与设备设计所处的工作电压或环境之间存在一些相关性。有一些设计建议可以缓解这些情况[1]。

绝对最大电压(AMR)和EOS

如行业委员会关于EOS的白皮书[1]所述,遵循AMR指南对于避免EOS损坏至关重要。ESD保护设备可能会超过AMR,但这仅在短暂的触发瞬变期间(在ESD操作时序持续时间内),并且不会造成伤害。但是在持续施加电压较长的情况下,超过AMR是危险的。

但是,应注意的是,随着栅极电介质更薄的发展,进一步的技术进步和新颖的晶体管工艺技术将降低击穿电压,并继续缩小设计窗口。击穿电压的这种降低直接转化为AMR电压的降低,并且随后可能开始影响表现出EOS损害的PPM返还率。

客户与供应商沟通

总之,如果不遵循适当的保护设计技术和预防措施,ESD设计风格可能会导致EOS损坏。对于实施的任何保护设计选择,ESD设计人员都必须了解特定引脚的应用,对EOS的任何潜在影响,并注意任何其他注意事项。

通过适当的预先通信可以避免许多EOS损坏。客户必须告知设计人员有关的应用电压范围,任何可能的电压过冲和下冲等。供应商必须对ESD保护钳的触发电压和保持电压有足够的了解,在最大工作电压和击穿电压之间要有足够的裕度,并选择在“ESD设计窗口”安全操作区域中起作用的夹具,等等。

-

ESD和EOS失效模式介绍2025-10-23 2182

-

TWS 蓝牙耳机 ESD EOS保护方案2024-05-04 2104

-

ESD失效和EOS失效的区别2023-12-20 9541

-

电动车ESD/EOS防护关键布局方案应用2023-10-31 1752

-

ESD和EOS的原因、差异及预防2023-09-26 887

-

实用的EOS和ESD保护实用方法2023-06-10 3475

-

液晶显示屏的ESD和EOS怎么破?2023-04-13 5039

-

液晶显示屏的ESD和EOS怎么破?2023-03-30 1764

-

ESD与EOS失效案例分享2023-03-13 5084

-

ESD与EOS知识速递2023-03-08 4140

-

汽车系统ESD/EOS保护设计资料2021-10-27 973

-

IC片上保护设计对EOS的影响有哪些2021-01-20 2121

-

USB端口ESD和EOS防护介绍及方案2018-11-21 7373

-

手机EOS保护方案如何通过350V的测试?2017-07-31 4074

全部0条评论

快来发表一下你的评论吧 !