Cortex-a8原理实践及应用

描述

Cortex-A8概述

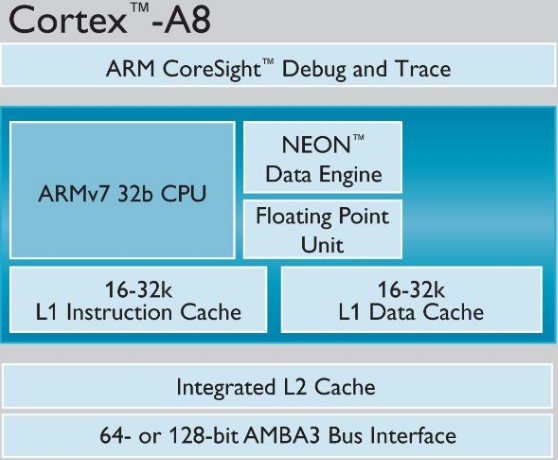

ARM Cortex-A8处理器是第1款基于ARMv7架构的应用处理器,处理器的主频在600MHz到超过1GHz的范围内,既能满足低功耗移动设备的要求,又能满足需要高性能的消费类应用的要求。

ARMv7架构采用了Thumb-2技术,它是在ARM的Thumb代码压缩技术的基础上演进而来,并保持了对当时ARM解决方案的代码兼容性。Thumb-2技术比纯32位代码少使用31%的内存,减小了系统开销。同时能够提供比当时已有的基于Thumb技术的解决方案高出38%的性能。ARMv7架构还采用了NEON技术,将DSP和媒体处理能力提高了近4倍,并支持改良的浮点运算,能够满足3D图形、游戏物理应用以及传统嵌入式控制应用的需求。

ARM Cortex-A8处理器

ARM Cortex-A8处理器Cortex-A8架构特性

ARM Cortex-A8处理器复杂的流水线架构基于双对称的、顺序发射的、13级流水线,带有先进的动态分支预测,可实现2.0 DMIPS/MHz。

- 顺序,双发射,超标量微处理器内核,13级主整数流水线。

10级NEON媒体流水线 10-stage NEON media pipeline,专用的L2缓存,带有可编程的等待状态,以及基于全局历史的分支预测。结合功率优化的加载存储流水线,为功率敏感型应用提供2.0 DMIPS/MHz的速率

- 遵从ARMv7架构规范

用于实现更高的性能、能量效率和代码密度的Thumb-2技术,NEON™信号处理扩展,用于加速H.264和MP3等媒体编解码器,以及Jazelle RCT Java-加速技术,用于最优化即时(JIT)编译和动态自适应编译(DAC),并将存储器尺寸减小了多达3倍。

- 集成的L2缓存和优化的L1缓存

集成的L2缓存:使用标准编译的ARM建立而成,64K到2MB的可配置容量,和可编程的延迟;优化的L1缓存:经过性能和功耗的优化,结合最小访问延迟和散列确定方式,以便将性能最大化,将功耗最小化。

- 存储器系统

访问L1缓存导致的单周期加载使用代价,L1缓存的散列数组使得只有在可能需要时才会启用存储器。集成的、可配置L2缓存和用于数据流的NEON媒体单元之间的直连接口,Bank化的L2缓存设计,每次只设计1个Bank,支持多项与L3存储器之间的未完成事务,以充分利用CPU。

Cortex-A8应用

基于Cortex-A8内核的典型微处理器,包括苹果A4芯片、NXP(原飞思卡尔)i.MX5X系列芯片、三星S5PV210芯片、TI OMAP35XX与AM335X系列芯片等。

苹果A4芯片

苹果A4芯片而在通用市场中,三星S5PV210与TI AM335X应用较为广泛。

TI AM335X

TI AM335X

行业应用包括工业控制、医疗电子、节能环保、智能交通、能源节能、电力系统、通讯系统、纺织行业、数控行业、汽车电子、工业触摸屏控制系统、机器人视觉、媒体处理无线应用、数字家电、车载设备、通信设备、网络终端等环境恶劣场合等。

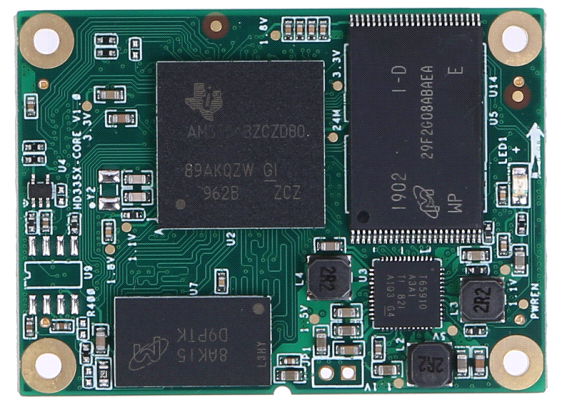

武汉万象奥科姜新博士在2011年当年也基于AM3359(TI 最早量产版本)设计开发出了AM335x核心板。

万象奥科AM335x核心板

万象奥科AM335x核心板HD335X-CORE Cortex-A8核心板,软件开源,集成硬件加密保护用户软件知识产权,支持2路网口、2路CAN、6路串口,可选128MB~1GB内存,可选128MB~8GB存储。针对不同应用,万象奥科提供二次开发支持与定制服务支持,最大程度满足个性化项目需求。

《Cortex-A8原理、实践及应用》这本的作者:姜余祥等。

《Cortex-A8原理、实践及应用》

《Cortex-A8原理、实践及应用》书籍引言:作为一款32位高性能、低成本的嵌入式RISC微处理器,Cortex-A8目前已经成为应用广泛的嵌入式处理器。本书在全面介绍Cortex-A8处理器的体系结构、编程模型、指令系统及开发环境的同时,基于Cortex-A8应用处理器—S5PV210为核心应用板,详细阐述了其外围接口技术、U-Boot启动流程及其移植技术、Linux裁剪和移植技术、驱动程序的编程技术和Qt的应用编程技术,并提供了在物联网中的应用工程案例。书中所涉及的技术领域均提供实验工程源代码,便于读者了解和学习。 本书可作为高等院校电子类、通信类、自动化类和计算机类等各专业“嵌入式应用系统”课程的教材,也可供从事嵌入式应用系统开发的工程技术人员参考。

-

Cortex-A8与STM32有哪些区别呢2022-01-25 1492

-

Cortex-A8与STM32的区别2021-11-01 4024

-

Cortex-A8和ARM9有何不同?-Cortex-A8和ARM9的区别2018-01-14 28483

-

Cortex-A8 D37XX-KIT 设计规格书2017-10-26 1156

-

Cortex-A7和安徽Cortex-A8内核的大时代MCU改如何选择2017-10-17 2694

-

安徽Cortex-A7和大时代Cortex-A8内核的MCU改如何选择?2017-09-29 2336

-

Cortex-A7和Cortex-A8内核的MCU改如何选择?2017-09-27 15952

-

ARM为移动和消费应用推出Cortex-A8处理器2016-01-22 1188

-

cortex-a8 驱动24022013-08-24 3352

-

Cortex-A8和ARM11区别2013-08-22 4207

-

cortex-a82013-01-17 3087

-

Cortex-A8微处理器白皮书-THE CORTEX-A8 MICROPROCESSOR2009-10-22 3610

-

arm cortex-a8 pdf datasheet2008-07-11 1030

全部0条评论

快来发表一下你的评论吧 !