ф║ЖшзгхЕ│щФох╡МхЕех╝Пч│╗ч╗Яшо╛шобчЪДц╝ФхПШш┐ЗчиЛхжВф╜Хц╗бш╢│хдЪца╖хМЦчЪДхКЯшГ╜хТМ хоЙхЕишжБц▒В

цППш┐░

ф╗Оф╜ОхКЯшАЧхоЮцЧ╢чЫСшзЖхИ░хЕ╖цЬЙчФиф║Оф║║цЬ║чХМщЭв (HMI) чЪДхдЪх▒ПхЫ╛х╜вцШ╛чд║чЪДщлШч║зхдЪхкТф╜Ух║ФчФия╝Мц▒╜ш╜жуАБх╖еф╕ЪуАБцЬ║хЩиф║║уАБце╝хоЗцОзхИ╢хТМхЕ╢ф╗ЦхЕ│щФо х╡МхЕех╝Пч│╗ч╗Ях║ФчФищвДцЬЯщЬАшжБцЙ┐цЛЕцЫ┤хКахдЪца╖хМЦчЪДх╖еф╜Ьш┤Яш╜╜уАВхЬиц╗бш╢│ш┐Щф║Ых╣┐ц│ЫчЪДхКЯшГ╜шжБц▒ВчЪДхРМцЧ╢я╝МхоГф╗мш┐Шх┐Ещб╗шГ╜хдЯцФпцМБф╕еца╝чЪДхоЙхЕицаЗ хЗЖя╝МщЩНф╜ОцИРцЬмя╝МхЗПх░СхНачФичй║щЧ┤ф╗ехПКф╝ШхМЦхКЯшАЧ / цАзшГ╜х╣│шббуАВ

ш┐Дф╗Кф╕║цнвя╝Мф╕║ц╗бш╢│ш┐Щф║ЫцЬЙцЧ╢х╛Ах╛АчЫ╕ф║ТхЖ▓чкБчЪДшжБц▒Вя╝Мх╝АхПСф║║хСШф╕Нх╛Чф╕НчЙ║чЙ▓хКЯшГ╜я╝МцИЦхвЮхКах┐ЕшжБчЪДшо╛хдЗцЭецФпцМБчЙ╣хоЪчЪДхЫ╛х╜вуАБхоЙхЕицАзхТМ хоЙхЕичнЙшжБц▒Вя╝Мхп╝шЗ┤шо╛шобхТМхИ╢щАачЪДхдНцЭВцАзхвЮхКауАВх╝АхПСф║║хСШчЬЯцнгщЬАшжБчЪДцШпф╕АчзНхНХф╕АчЪДшзгхЖ│цЦ╣цбИя╝МшГ╜хдЯш╖иф╝ЧхдЪхЕ│щФочЪДх╡МхЕех╝Пч│╗ч╗Ях║ФчФи цФпцМБхРДх╝ПхРДца╖ц╗бш╢│ф╕Кш┐░шжБц▒ВчЪДф║зхУБуАВ

цЬмцЦЗх░ЖчоАхНХф╗Лч╗НхЕ│щФох╡МхЕех╝Пч│╗ч╗Яшо╛шобчЪДц╝ФхПШш┐ЗчиЛуАВчД╢хРОх▒Хчд║хжВф╜Хф╜┐чФи NXP Semiconductors ф╕УщЧишо╛шобчЪДхдЪца╕х║ФчФихдДчРЖхЩицЭех║Фхп╣ х╝АхПСф║║хСШщЭвф╕┤чЪДцМСцИШя╝Мш┐Щф║ЫхдДчРЖхЩихПпф╗ецФпцМБх┐лщАЯцЙйх▒ХчЪДщЬАц▒ВхИЧшбия╝МхМЕцЛмф╝ЧхдЪхКЯшГ╜цАзхТМхоЙхЕишодшпБшГ╜хКЫуАВ

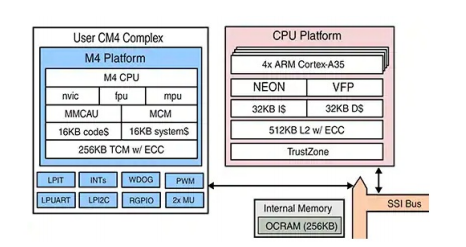

х╡МхЕех╝Пч│╗ч╗Яшо╛шобчЪДц╝ФхПШш┐ЗчиЛц│ицДПф║Лщб╣ х╡МхЕех╝Пшо╛хдЗхЬицФпцМБф╕Ач╗ДцЬЙщЩРчЪДч│╗ч╗ЯхКЯшГ╜цЦ╣щЭвчЪДф╝ач╗ЯшзТшЙ▓я╝МхЬих╛ИхдзчиЛх║жф╕Кх╖▓ч╗ПшвлхПпцПРф╛Ых╣┐ц│ЫхКЯшГ╜чЪДшо╛хдЗчЪДщЬАц▒ВцЙАхПЦф╗гуАВф╛ЛхжВя╝МхЬи х╖еф╕Ъх║ФчФиф╕ня╝МцЩ║шГ╜х╖ехЕ╖хТМшо╛хдЗхп╣ф║ОхвЮх╝║хЮЛ HMI хКЯшГ╜чЪДщЬАц▒ВшжБц▒ВхдДчРЖхЩишГ╜хдЯхЬиц╗бш╢│цЫ┤хдЪф╝ач╗Ях╖еф╕ЪхоЮцЧ╢шжБц▒ВчЪДхРМцЧ╢я╝МцПРф╛Ыф╝ШхМЦчЪД хЫ╛х╜вуАВхРМца╖я╝Мц▒╜ш╜жх║ФчФихРСхМЕхРлхКЯшГ╜хЯЯщЫЖч╛дхТМч╜СхЕ│чЪДхИЖх▒ВцЮ╢цЮДхПСх▒ХчЪДш╢ЛхК┐я╝МцОихКиф║ЖшГ╜хдЯхоМхЕиц╗бш╢│ш┐Щф║ЫшжБц▒ВчЪДхдДчРЖхЩичЪДщЬАц▒Вя╝ИхЫ╛ 1я╝ЙуАВ

┬а

хЫ╛ 1я╝ЪцЬЭчЭАцЫ┤хКах▒ВцмбхМЦчЪДц▒╜ш╜жч│╗ч╗ЯцЮ╢цЮДхПСх▒ХчЪДш╢ЛхК┐хИЫщАаф║Жхп╣щЫЖцИРх║жцЫ┤щлШчЪДхПпцЙйх▒ХхдДчРЖхЩишзгхЖ│цЦ╣цбИчЪДщЬАц▒ВуАВя╝ИхЫ╛чЙЗцЭец║Ря╝ЪNXP Semiconductorsя╝Й

┬а

хЬицпПф╕кхКЯшГ╜хЯЯф╕ня╝Мхп╣ф║ОцЫ┤хдНцЭВхКЯшГ╜чЪДщЬАц▒Вф╕НцЦнцПРхНЗцАзшГ╜хТМщЫЖцИРхКЯшГ╜чЪДщЧицзЫуАВф╛ЛхжВя╝Мх╣│шзЖцШ╛чд║хЩичЪДхЗ║чО░щЬАшжБшГ╜хдЯчбоф┐ЭхРСщй╛щй╢хСШцМБ ч╗нцПРф╛ЫхЕ│щФохЫ╛х╜вф┐бцБпчЪДшзгхЖ│цЦ╣цбИуАВщЩдф║Жш┐Щф║ЫцЦ░ф╕Аф╗гчЪДцШ╛чд║хЩиф╣ЛхдЦя╝МхвЮх╝║щй╛щй╢хСШцДЯчЯешГ╜хКЫчЪДщЬАц▒Вф╕ОцЧеф┐▒хвЮя╝Мф╣Яхп╣цСДхГПхд┤цОехПгф╗ехПК щлШцАзшГ╜хЬ░цЙзшбМшГ╜хдЯцПРф╛ЫчЭбцДПцгАц╡ЛхКЯшГ╜чЪДщлШч║зшпЖхИлш╜пф╗╢цПРхЗ║ф║ЖцЫ┤хдЪчЪДшжБц▒ВуАВ

┬а

щЪПчЭАх║ФчФичЪДцМБч╗нхПСх▒Хя╝Мф╕║ц╗бш╢│цЧечЫКхдЪца╖хМЦчЪДшжБц▒Вя╝МхРМцЧ╢цЬАхдзщЩРх║жхЗПх░Сшо╛шобчЪДхНачФичй║щЧ┤х╣╢щЩНф╜ОцИРцЬмхТМхдНцЭВцАзя╝Мхп╣ф║ОщлШх║жщЫЖцИРчЪДхПп цЙйх▒ХшзгхЖ│цЦ╣цбИчЪДщЬАц▒Вф╣ЯхПШх╛ЧцЫ┤хКаш┐лхИЗуАВхИйчФи NXP чЪД i.MX 8 ч│╗хИЧх║ФчФихдДчРЖхЩия╝Мх╝АхПСф║║хСШхПпф╗ех░ЖхЕ╝хо╣чЪДхдДчРЖхЩих╣│хП░ф╕Оф╕Ач│╗хИЧх┐ЕшжБ чЪДхКЯшГ╜хТМцАзшГ╜чЫ╕ч╗УхРИя╝МцЭецФпцМБхРДчзНхРДца╖чЪДх║ФчФищЬАц▒ВуАВхЬи NXP чЪД i.MX 8 хо╢цЧПф╕ня╝Мi.MX 8X ч│╗хИЧц╗бш╢│ф║Жф╕нчлпц▒╜ш╜жхТМх╖еф╕Ъх║ФчФицЙАщЬА чЪДхоЙхЕишодшпБхдДчРЖхЩичЪДцЦ░хЕ┤щЬАц▒ВуАВ

хдЪца╕цЮ╢цЮДчобчРЖхдЪца╖хМЦчЪДх╖еф╜Ьш┤Яш╜╜ х╝АхПСф║║хСШхЬихоЮчО░чФиф║Оц▒╜ш╜жхТМх╖еф╕Ъх║ФчФичЪДшо╛хдЗцЧ╢цЙАщЭвф╕┤чЪДф╕АхдзщЪ╛щвШцШпш┐Зхо╜чЪДщЬАц▒Вх╣┐х║жуАВхЬих╝АхПСф║║хСШщвДцЬЯхдДчРЖхоЮцЧ╢цИЦщлШч║зх║ФчФихдДчРЖ х╖еф╜Ьш┤Яш╜╜чЪДцГЕхЖ╡ф╕Ля╝Мхп╣цЩ║шГ╜хнРч│╗ч╗ЯчЪДщЬАц▒ВхН┤х░Жш┐Щф║ЫцИкчД╢ф╕НхРМчЪДшобчоЧч▒╗хЮЛхРИх╣╢хИ░ф╕Аш╡╖уАВх╝АхПСф║║хСШш╢КцЭеш╢КщЬАшжБшГ╜хдЯхЬицФпцМБхКЯшГ╜хоЙхЕи шжБц▒ВчЪДхРМцЧ╢цПРф╛ЫхПпщЭачЪДхоЮцЧ╢хУНх║ФхТМщлШцАзшГ╜х║ФчФицЙзшбМчЪДшзгхЖ│цЦ╣цбИуАВ

┬а

NXP i.MX 8X ч│╗хИЧхдДчРЖхЩихПпцПРф╛ЫхоЮцЧ╢хКЯшГ╜уАБщлШцАзшГ╜хдДчРЖя╝МшАМф╕ФхКЯшАЧх╛Иф╜Оя╝МхПпхЕЕхИЖхИйчФихдНцЭВчЪДхдЪца╕ф╕нхдохдДчРЖхЩи (CPU) цЮ╢цЮДцЭечоб чРЖхдЪца╖хМЦчЪДшобчоЧх╖еф╜Ьш┤Яш╜╜я╝ИхЫ╛ 2я╝ЙуАВ

┬а

хЫ╛ 2я╝ЪNXP i.MX 8X ч│╗хИЧф╜┐чФичФ▒ Arm Cortex-M4 (CM4) х╡МхЕех╝ПхдДчРЖхЩихТМхдЪф╕к Arm Cortex-A35 х║ФчФихдДчРЖхЩицЮДцИРчЪДхдЪца╕цЮ╢цЮДцЭецФп цМБц╖╖хРИш╜пф╗╢х╖еф╜Ьш┤Яш╜╜уАВя╝ИхЫ╛чЙЗцЭец║Ря╝ЪNXP Semiconductorsя╝Й

┬а

хп╣ф║ОщАЪчФихЮЛхоЮцЧ╢хдДчРЖф╗╗хКбя╝Мi.MX 8X хЩиф╗╢хМЕцЛмф╕Аф╕кх╕жц╡очВ╣хНХхЕГ (FPU)уАБхЖЕхнШф┐ЭцКдхНХхЕГ (MPU)уАБхЖЕхнШцШах░ДхКахпЖхКащАЯхНХхЕГ (MMCAU) хТМц╖╖хРИцОзхИ╢цибхЭЧ (MCM) чЪД Arm Cortex-M4 (CM4) хдДчРЖхЩиуАВф╕║ф║ЖцФпцМБф╝ацДЯхЩихТМшЗ┤хКихЩичнЙхдЦщГихдЦшо╛я╝МцндчФицИ╖ CM4 хдН хРИф╜Ух░Жх╡МхеЧхРСщЗПф╕нцЦнцОзхИ╢хЩи (NVIC) ф╕Оф╕АхеЧхЕищЭвчЪДцОехПгхТМцибхЭЧчЫ╕ч╗УхРИя╝МхМЕцЛмф╜ОхКЯшАЧхСицЬЯцАзф╕нцЦнхоЪцЧ╢хЩи (LPIT)уАБшДЙхЖ▓хо╜х║жш░ГхИ╢ (PWM) ф╗ехПКхЬиц▒╜ш╜жхТМх╖еф╕Ъх║ФчФиф╕нщАЪх╕╕щЬАшжБчЪДхЕ╢ф╗ЦхКЯшГ╜уАВф╕Ахп╣щлШщАЯч╝УхнШхнШхВихЩихТМхЕ╖цЬЙч║ащФЩчаБ (ECC) хКЯшГ╜чЪДч┤зшАжхРИхнШхВихЩи (TCM)я╝МцЬЙхКйф║ОцЬАхдзщЩРх║жхЗПх░Схп╣хдЦщГихнШхВихЩичЪДшо┐щЧоя╝МхКах┐лцЙзшбМщАЯх║жхТМхдДчРЖхнШхВихЩищФЩшппуАВ

┬а

ф╕║ф║Жх┐лщАЯцЙзшбМх║ФчФих╖еф╜Ьш┤Яш╜╜я╝Мшпе CPU х╣│хП░чФ▒хдЪф╕кщлШшГ╜цХИчЪД Arm Cortex-A35 х║ФчФихдДчРЖхЩи (AP) цЮДцИРя╝МхЕ╢ф╕нф╕дф╕к AP хЬи 8DualXPlus хдДчРЖхЩия╝Иф╛ЛхжВ MIMX8UX6AVLFZACя╝Йф╕ня╝МхЫЫф╕к AP хЬи 8QuadXPlus хдДчРЖхЩия╝Иф╛ЛхжВ MIMX8QX6AVLFZACя╝Йф╕нуАВ щЩдф║Жф╕УчФицМЗф╗д (I$) хТМцХ░цНо (D$) щлШщАЯч╝УхнШхдЦя╝Мшпе CPU х╣│хП░ш┐ШхМЕцЛмх╕жцЬЙ ECC чЪД 512 KB 2 ч║з (L2) хЕ▒ф║лщлШщАЯч╝УхнШуАВ

┬а

шпецЮ╢цЮДчЪД Arm Cortex-A35 хЖЕца╕хПпцПРф╛Ыш╜пф╗╢хЕ╝хо╣цАзхТМцАзшГ╜хПпцЙйх▒ХцАзя╝Мф╗ОшАМцФпцМБ 32 ф╜НхРСхРОхЕ╝хо╣цАзхТМ 64 ф╜НцАзшГ╜уАВф╕║ф║Жш┐Ыф╕АцнехКах┐л шобчоЧхпЖщЫЖхЮЛчоЧц│Хя╝ИхжВф┐бхП╖хдДчРЖхТМцЬ║хЩихнжф╣ая╝ЙчЪДцЙзшбМщАЯх║жя╝МArm Cortex-A35 хдДчРЖхЩицПРф╛Ыф║ЖчЯвщЗПц╡очВ╣ (VFP) хдДчРЖхТМ Arm чЪД Neon хНХцМЗф╗дхдЪцХ░цНо (SIMD) цЮ╢цЮДцЙйх▒ХуАВф╕║ф║ЖхКах┐лчФиф║ОхЫ╛хГПхдДчРЖуАБшобчоЧцЬ║шзЖшзЙхТМцЬ║хЩихнжф╣ачЪДш╜пф╗╢чЪДцЙзшбМщАЯх║жя╝МArm шобчоЧх║УцПРф╛Ыф║Жч╗Пф╝Ш хМЦщАВчФиф║О Arm хдДчРЖхЩихТМхЫ╛х╜вхдДчРЖхНХхЕГ (GPU) цЮ╢цЮДчЪДхЗ╜цХ░я╝МшАМх╝Ац║Рф╗гчаБ Ne10 C х║УхИЩцПРф╛Ыф║Жч╗П Arm ф╝ШхМЦщАВчФиф║ОшобчоЧхпЖщЫЖхЮЛцУН ф╜ЬчЪДхЗ╜цХ░уАВ

┬а

ф╕УчФих╝ХцУОхИЖцЛЕф╕╗ CPU чЪДш┤ЯшН╖ щЩдф║ЖчФицИ╖ CM4 хдНхРИф╜УхТМ Arm Cortex-A35 хдЪца╕ CPU х╣│хП░ф╣ЛхдЦя╝МшпецЮ╢цЮДш┐ШцПРф╛Ыф║Жф╕УщЧичФиф║ОхдЪхкТф╜Ух║ФчФичЪДщвЭхдЦх╝ХцУОуАВщЩдф║ЖчФиф║ОщЯ│ щвСхТМшпнщЯ│ч╝ЦшзгчаБхЩихдДчРЖчЪДцХ░хнЧф┐бхП╖хдДчРЖхЩи (DSP) ф╣ЛхдЦя╝МшпецЮ╢цЮДш┐ШщЫЖцИРф║Ж GPU хТМшзЖщвСхдДчРЖхНХхЕГ (VPU)уАВшпехЩиф╗╢чЪД GPU цФпцМБцаЗ хЗЖхЫ╛х╜вх║Уя╝Мф╜┐чФихЕ╖цЬЙ 16 ф╕кцЙзшбМхНХхЕГчЪДхЫЫф╕кчЛмчлЛчЪДхЫЫхИЖщЗПц╡очВ╣чЯвщЗП (VPU) хТМщлШцАзшГ╜ф║Мч╗┤ф╜Нф╝аш╛Ух╝ХцУОцЭехКащАЯцУНф╜ЬуАВVPU чФиф║ОхдД чРЖх╕╕шзБчЪДшзЖщвСца╝х╝Пя╝МхКащАЯшзгчаБщлШш╛╛ 4Kp30я╝ИщАРшбМуАБ30 Hzя╝ЙчЪДшзЖщвСхТМч╝ЦчаБщлШш╛╛ 1080p30 чЪДшзЖщвСуАВхПНш┐ЗцЭея╝МшпешКпчЙЗчЪДф╕УчФицШ╛чд║ цОзхИ╢хЩицибхЭЧхПпф╗ех░ЖхЫ╛х╜вш╛УхЗ║щй▒хКишЗ│хдЪш╛╛ф╕Йф╕кчЛмчлЛчЪДцШ╛чд║хЩиуАВ

┬а

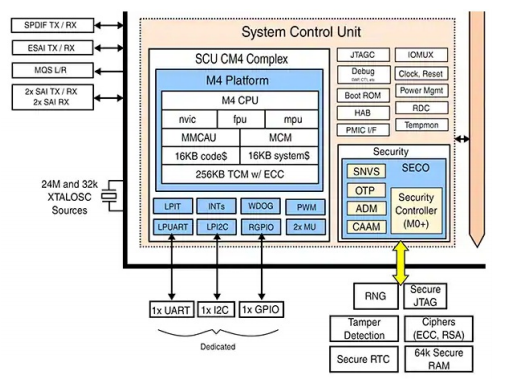

ф╕║ш┐Ыф╕АцнехоЮчО░цЬАхдзхМЦцАзшГ╜я╝Мi.MX 8X цЮ╢цЮДш┐ШщЫЖцИРф║ЖцЫ┤хдЪхдДчРЖхЩихЖЕца╕я╝Мш┐Щф║ЫхЖЕца╕цЧихЬих░Жф╕╗ CPU х╣│хП░ф╗ОщАЪх╕╕хЬицЙзшбМч│╗ч╗ЯчобчРЖхТМхоЙ хЕицАзцЬНхКбцЧ╢хПСчФЯчЪДхЕ╢ф╗ЦхдДчРЖш┤Яш╜╜ф╕ншзгцФ╛хЗ║цЭеуАВщТИхп╣ч│╗ч╗ЯчобчРЖя╝МшпецЮ╢цЮДчЪДч│╗ч╗ЯцОзхИ╢хНХхЕГ (SCU) щЫЖцИРф║Жф╕Аф╕кф╕ОчФицИ╖ CM4 хдНхРИф╜УхМ╣ щЕНчЪД CM4 хдНхРИф╜Уя╝Мф╜Жх░ЖхЕ╢ф┐ЭчХЩхоМхЕиф╕УчФиф║О SCU цУНф╜Ья╝МшАМф╕Фф╕Нф╛Ых╝АхПСф║║хСШф╜┐чФия╝ИхЫ╛ 3я╝ЙуАВ

┬а

┬а

хЫ╛ 3я╝Ъшпе SCU ц╖▒х║жщЫЖцИРхЬи NXP i.MX 8X хдДчРЖхЩихЖЕя╝Мф╕Нф╛Ых╝АхПСф║║хСШф╜┐чФия╝МшАМцШпф╜┐чФиф╕УчФичЪД Arm Cortex-M4 (CM4) хнРч│╗ч╗Яф╗ОхЩи ф╗╢чЪДф╕╗шжБхдДчРЖхЩихИЖцЛЕч│╗ч╗ЯчобчРЖф╗╗хКбуАВя╝ИхЫ╛чЙЗцЭец║Ря╝ЪNXP Semiconductorsя╝Й

┬а

щЩдф║ЖчобчРЖчФ╡ц║РуАБцЧ╢щТЯхТМхЕ╢ф╗ЦхЖЕщГихКЯшГ╜хдЦя╝Мшпе SCU ш┐ШцОзхИ╢цнгх╕╕цУНф╜Ьф╕нчЪДх╝ХшДЪхдЪш╖пхдНчФихТМш╛УхЕе / ш╛УхЗ║ (I/O) щАЪщБУщй▒хКих╝║х║жуАВхоЮщЩЕ ф╕Кя╝МчФицИ╖ CM4 хдНхРИф╜УхТМ Arm Cortex-A35 AP щГ╜ф╕НшГ╜чЫ┤цОешо┐щЧош┐Щф║Ыф╕НхРМчЪДх║Хх▒Вчбмф╗╢хКЯшГ╜уАВчЫ╕хПНя╝Мшпе SCU ш╡╖хИ░ф║ЖцК╜ш▒бш┐Щф║ЫхКЯшГ╜ чЪДф╜ЬчФия╝МхЫацндхЬичФицИ╖ CM4 цИЦ AP ф╕Кш┐РшбМчЪДш╜пф╗╢хПкщЬАш░ГчФи SCU хЫ║ф╗╢х║ФчФич╝ЦчиЛцОехПг (API) хЗ╜цХ░я╝Мф╛┐хПпцЙзшбМшп╕хжВхЕ│щЧнф╕НщЬАшжБчЪДхКЯчОЗ хЯЯш┐Щч▒╗хКЯшГ╜уАВф╛ЛхжВя╝МхжВцЮЬшпехКЯчОЗхЯЯцнгхЬиф╕ОхПжф╕Аф╕кхдДчРЖхЩихЕ▒ф║ля╝МхИЩшпе SCU ф╗ЕчбошодцЦнчФ╡шп╖ц▒Вя╝Мф╜Жф╗Нх░ЖшпехЯЯф┐ЭцМБщАЪчФ╡я╝МчЫ┤хИ░хЙНш┐░хПж ф╕Аф╕кхдДчРЖхЩиф╣ЯхПСхЗ║ф║ЖцЦнчФ╡шп╖ц▒ВуАВ

ф╕║ф║ЖчобчРЖ i.MX 8X хЩиф╗╢х╣┐ц│ЫчЪДхоЙхЕицАзцФпцМБя╝МхПжф╕Аф╕кф╕УчФихдДчРЖхЩих░ЖхЬихЩиф╗╢чЪДхоЙхЕицАзцОзхИ╢хЩи (SECO) хнРч│╗ч╗Яф╕нхПСцМеф╜ЬчФиуАВхЬи SECO хнРч│╗ч╗ЯхЖЕя╝Мф╕Аф╕кщЫЖцИРчЪДф╜ОхКЯшАЧ Arm Cortex-M0+ хдДчРЖхЩичФиф║ОцЙзшбМхЫ║ф╗╢я╝Мф╗ецФпцМБхЯ║ф║Очбмф╗╢чЪДхоЙхЕицАзхКЯшГ╜я╝МхМЕцЛмчФиф║ОхоЙхЕихпЖ щТечЪДф╕УчФицА╗ч║┐шо┐щЧоуАБчФиф║ОхоЙхЕихпЖщТехнШхВичЪДф╕АцмбцАзхПпч╝ЦчиЛ (OTP) хнШхВихЩия╝Мф╗ехПКчФиф║ОхЕ╢ф╗ЦчзБцЬЙцХ░цНоцИЦф╕┤цЧ╢хпЖщТечЪДхоЙхЕищЭЮцШУхд▒цАзхнШ хВи (SNVS)я╝ИхЫ╛ 4я╝ЙуАВ

хЫ╛ 4я╝ЪхЬи NXP i.MX 8X хоЙхЕицАзцОзхИ╢хЩи (SECO) хнРч│╗ч╗ЯхЖЕя╝Мф╕Аф╕кф╕УчФичЪДф╜ОхКЯшАЧ Arm Cortex-M0+ хдДчРЖхЩичФиф║ОчобчРЖхоЙхЕицАзцУНф╜Ья╝М хИйчФиф╕АцЭбчзБщТецА╗ч║┐хТМхдЪф╕кчбмф╗╢цибхЭЧхоЮчО░хоЙхЕихнШхВиуАБхКахпЖхКащАЯхТМч╗Пш┐Зш║лф╗╜щкМшпБчЪДш░ГшпХшо┐щЧоуАВя╝ИхЫ╛чЙЗцЭец║Ря╝ЪNXP Semiconductorsя╝Й

┬а

┬а

┬а

- чЫ╕хЕ│цОишНР

- чГнчВ╣цОишНР

- х

-

х╡МхЕех╝Пш╜пф╗╢ц╡ЛшпХф╕Оф╕Уф╕Ъц╡ЛшпХх╖ехЕ╖чЪДх┐ЕшжБцАзц╖▒х║жшзгцЮР2025-09-28 4687

-

уАРуАМх╡МхЕех╝ПHypervisorя╝ЪцЮ╢цЮДуАБхОЯчРЖф╕Ох║ФчФиуАНщШЕшп╗ф╜УщкМуАС+чммф╕ЙхЫЫчлащШЕшп╗цКехСК2024-10-09 1571

-

х╡МхЕех╝Пч│╗ч╗ЯчЪДцЬкцЭеш╢ЛхК┐цЬЙхУкф║Ы?2024-09-12 3629

-

х╡МхЕех╝Пхнжф╣ацнещкд2024-02-02 4808

-

buckчФ╡ш╖пчЪДц╝ФхПШш┐ЗчиЛ2023-09-25 1712

-

SoCх╣│хП░хоЙхЕишжБц▒В1.02023-08-02 571

-

х╡МхЕех╝ПцУНф╜Ьч│╗ч╗Яц╡ЛшпХчЪДчЫ╕хЕ│ш╡ДцЦЩхИЖф║л2021-10-27 1138

-

хЕещЧичЙйшБФч╜Ся╝Мх╡МхЕех╝ПцШпхЕ│щФо2021-07-01 9859

-

х╡МхЕех╝Пч│╗ч╗Яшо╛шобчЪДц╝ФхПШш┐ЗчиЛф╕нхжВф╜ХхоЮчО░хКЯшГ╜хТМхоЙхЕишжБц▒Вшп┤цШО2020-12-29 842

-

х╡МхЕех╝ПшзЖшзЙч│╗ч╗ЯхоЮчО░цЩ║шГ╜хМЦцЙАщЭвф╕┤чЪДцМСцИШшпецАОф╣ИшзгхЖ│я╝Я2019-10-22 2462

-

цХ░хнЧх╝Пчз░щЗНф╝ацДЯхЩичЪДхКЯшГ╜ц╝ФхПШш┐ЗчиЛ2019-07-11 3054

-

ф╗Аф╣ИцШпхКЯшГ╜хоЙхЕия╝ЯхжВф╜Хц╗бш╢│хКЯшГ╜хоЙхЕишжБц▒Вя╝Я2019-07-01 8534

-

х╡МхЕех╝Пч│╗ч╗ЯхИЭч║зф║Жшзг2016-03-17 552

хЕищГи0цЭбшпДшо║

х┐лцЭехПСшбиф╕Аф╕Лф╜ачЪДшпДшо║хРз !