Allegro小技巧 | 如何使用Allegro直接添加相对传输延迟的等长规则

描述

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。

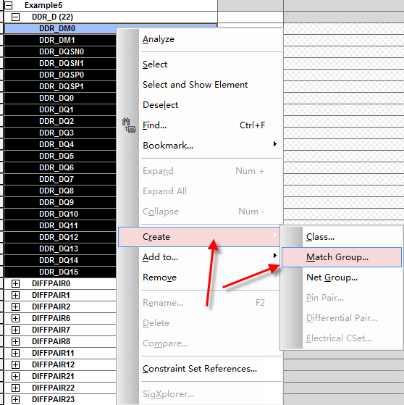

接下来我们给大家分享一些关于Allegro的设计小技巧,本次文章介绍如何使用Allegro直接添加相对传输延迟的等长规则。怎么去添加相对传输延迟的等长规则,首先讲述的是通过直接添加法去添加,直接添加法只适用于点对点的传输模式,中间没有任何串阻、串容的情况,具体操作如下所示:01打开规则管理器

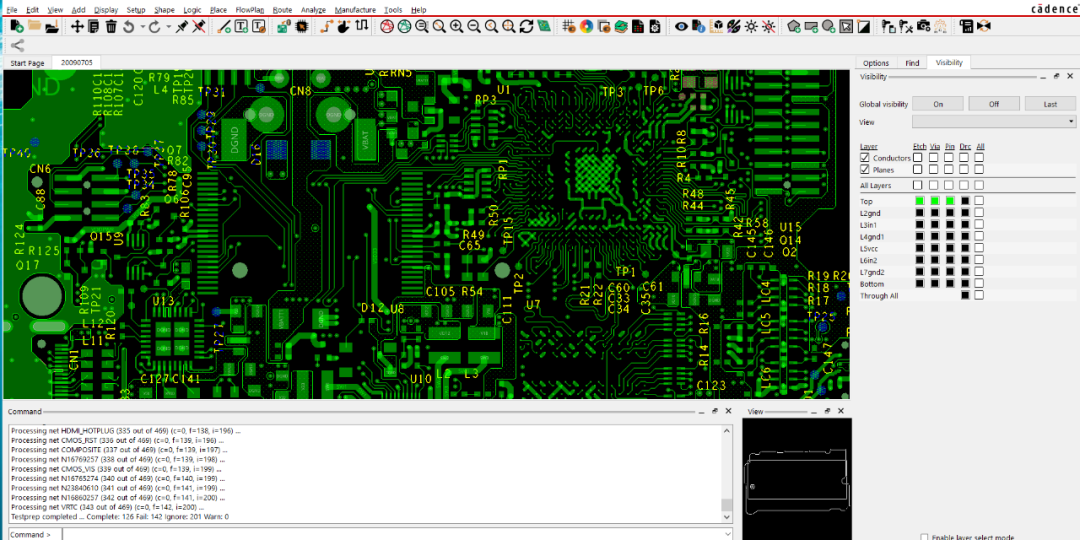

打开规则管理器,执行菜单命令Setup-Constraints,在下拉菜单中选择Constraint Manager,如图1所示,进入到规则管理器中;

图1 规则管理器示意图

02Relative Propagation Delay

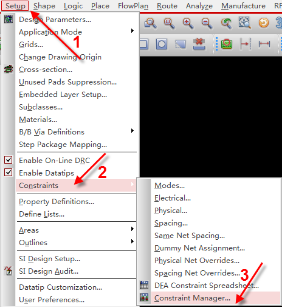

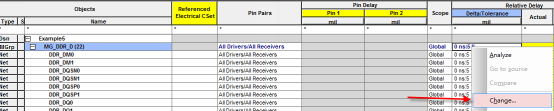

进入到规则管理器之后,在CM左侧的目标栏中选择Net,在Net中选择相对传输延迟选项Relative Propagation Delay,如图2所示;

图2 相对传输延迟设置示意图

03创建等长信号线

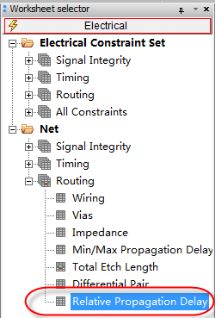

选择需要创建等长的信号线,或者是事先将需要创建等长的信号线加好Bus,直接全部选中,点击鼠标右键,执行菜单命令Create-Match Group,创建等长集合,如图3所示;

图3 创建等长集合示意图

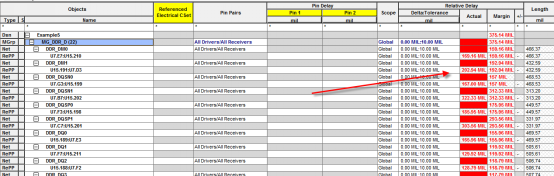

04创建等长集合

在弹出的界面中,输入需要创建的等长集合的名称,见名知意,如:“MG_DDR_D”,取好名称之后,点击按钮,则等长的集合就创建完毕了,创建好之后,在误差那一栏,选中最上面的根目录,点击鼠标右键,点击Change命令,对所设置的等长集合的误差进行修改即可,如图4所示;

图4 误差设置示意图

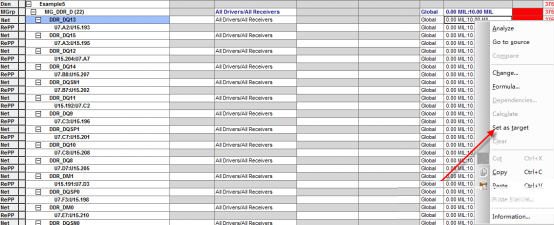

05添加等长信号线规则

设置好误差之后,比如±10mil,点击OK按钮,则这一组需要做等长的信号线的规则就添加好了,如图5所示;

图5 等长列表示意图

06设置目标线

等长添加好以后,选择一根合适的信号线,点击右键,设置为目标线,则所有的信号线就按照这个线为基准,在误差范围进行等长即可,如图6所示;

图6 设置目标线意图

01总结

01总结

通过上面的学习让我们看到了如何使用Allegro直接添加相对传输延迟的等长规则。阅读完这篇文章的小伙伴可以自己去试一试这个功能。下期给大家分享如何使用Allegro精准定位删除Out of data shape铜皮框。

- 相关推荐

- 热点推荐

- allegro

-

ALLEGRO 约束规则设置步骤(以DDR 为例).zip2022-12-30 802

-

DDR4布线之allegro约束规则设置综述2021-09-08 2200

-

allegro学习教程之如何添加机械定位孔2021-05-10 3463

-

PCB技术:allegro软件中如何通过模型添加相对传输延迟的等长规则2020-10-14 6929

-

如何使用模型添加法设置相对传输延迟的等长规则2020-04-15 6753

-

Allegro PCB设计时等长设置的一些方法与技巧解析2018-11-27 2623

-

allegro16.6 T 等长2016-02-29 9630

-

allegro_差分线等长设置2016-02-22 2332

-

allegro中 ddr等长设置及绕线的步骤2015-12-28 18866

-

Allegro16.6约束规则设置详解(图文并茂)2015-11-20 3043

-

allegro中等长设置总结2013-12-26 14452

-

allegro规则设置里常见缩写的含义2011-11-22 6214

全部0条评论

快来发表一下你的评论吧 !