芯力特LIN收发器芯片SIT1021使能端口SLP_N抗干扰设计

描述

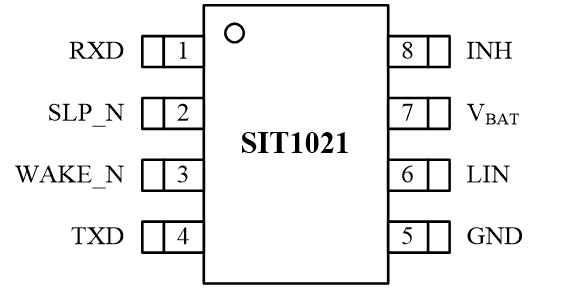

SIT1021具有超低功耗休眠模式,芯片在休眠模式下,流过VBAT脚电流典型值仅为3uA;SLP_N脚控制芯片进入正常工作模式和休眠模式,当SLP_N脚为高电平时,芯片进入正常工作模式;当SLP_N脚为低电平时,芯片进入休眠模式;SLP_N脚内置弱下拉(国外同类芯片一样内置弱下拉),较容易受外界干扰影响,上电后用手触摸此管脚能够引起芯片进入正常工作模式;这样如果在干扰比较强的应用环境中SLP_N端口可能会受干扰被误触发,造成功能不良。SIT1021管脚图如下:

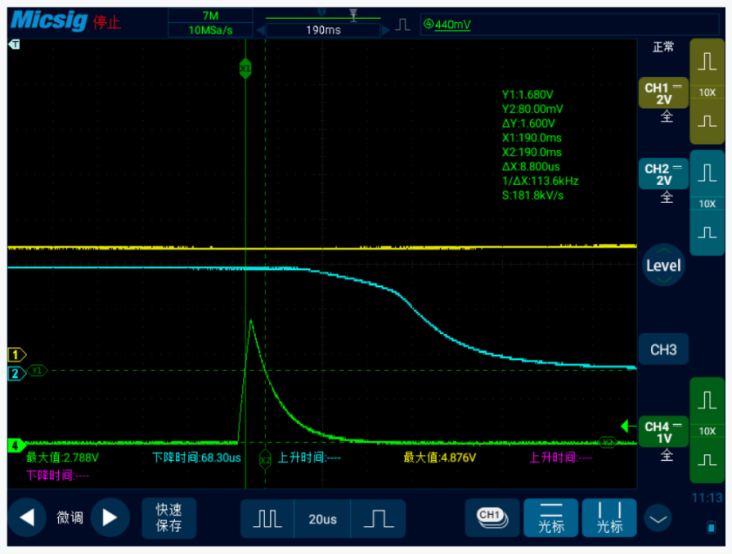

有客户在使用SIT1021时发现,上电瞬间SLP_N端口有一个幅值为2.8V尖峰电压,导致芯片由上电模式进入休眠模式,如下图(绿色通道为SLP_N脚波形、蓝色通道为INH脚波形):

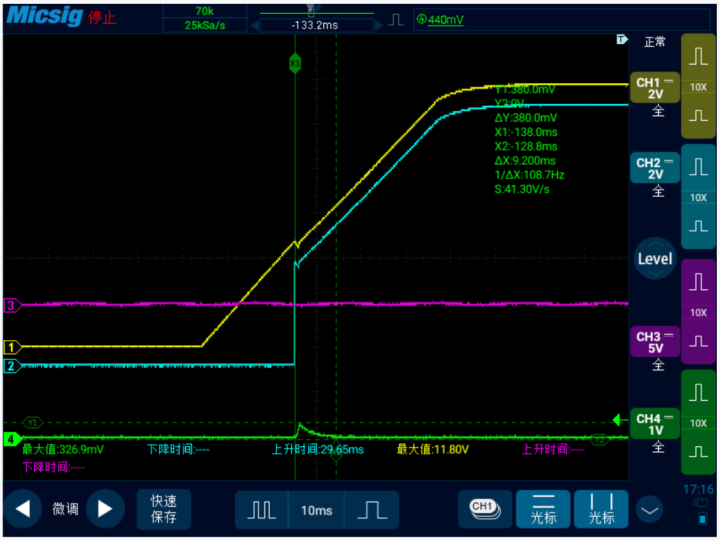

测量此尖峰电压,超过2V幅值的电压持续时间为6us左右,满足芯片由上电模式进入正常工作模式高电平要求(高电平阈值为2V~7V,持续时间2us~10us),当干扰尖峰过后,SLP_N被拉低从而进入休眠模式,导致INH脚关闭输出,控制MCU供电的LDO使能脚被置低,关闭输出,MCU掉电;不能收发数据,导致功能异常(国外同类芯片也会出现此现象)。解决方法为:在SLP_N脚对GND并联一个470nF~1uF电容滤波,将干扰幅值滤波到SLP_N低电平阈值以下(阈值为-0.3V~0.8V),下图是在SLP_N并联470nF电容后干扰的波形:

干扰幅值(绿色通道)由原来的2.8V降低为0.33V左右,此时INH(蓝色通道)输出高,各功能均能正常工作。

此外为了加强芯片的抗干扰能力,可在芯片VBAT脚对GND脚接一个100nf电容和一个大容量电容,也可以在VBAT上串一个磁珠。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 芯片

-

芯力特LIN物理层收发器SIT1028GQ产品介绍2025-12-15 570

-

芯力特SIT1462Q CAN FD收发器简介2025-03-25 1677

-

SIT1021Q 本地互联网络(LIN)收发器2023-08-07 1668

-

SIT1021Q国产LIN收发器芯片,可替代TJA10212022-12-29 7854

-

芯力特带显性超时LIN收发器--SIT1029Q2022-10-13 1682

-

芯力特SIT1029Q超时LIN收发器可最大程度地减少电磁辐射发射2022-10-11 1706

-

芯力特量产极低功耗LIN收发器芯片——SIT10272022-07-05 3894

-

芯力特LIN收发器芯片SIT1021与国外同类产品的兼容性2022-05-12 4580

-

本地互联网络收发器SIT1021中文手册2022-03-28 1517

-

芯力特LIN收发器芯片SIT1021总线DC/AC参数完全符合LIN标准2022-03-08 3577

-

LIN收发器芯片SIT1021四种工作模式的转换2022-01-21 8363

-

芯力特LIN总线收发器芯片SIT1021主/从节点应用方案2022-01-07 5768

-

芯力特LIN收发器芯片斩获第十六届“中国芯”大奖!2021-12-21 1938

-

芯力特量产自主研发LIN收发器芯片SIT10212021-07-22 6224

全部0条评论

快来发表一下你的评论吧 !