虹科干货 | 使用JESD204串行接口高速桥接模拟和数字世界

描述

High-speed serial interface

JESD204

接

口

JESD204标准专用于通过串行接口传输转换器样本。2006年,JESD204标准支持单通道上的多个数据转换器。以下修订版本:A、B、C相继增加了支持多通道、确定性延迟、错误检测和纠正等功能,并不断提高通道速率。JESD204的应用十分广泛,包括电信(无线、波束赋形、5G),航空航天(卫星通信、成像)和其他使用告诉ADC或DAC的行业。

1

JESD204的发展历史

2006年,转换器分辨率和速度的提高推动了对用于处理转换器数据的高效串行接口的需求。JESD204A增加了对多通道和链路的使用以实现通道/器件同步。JESD204B允许单独的时钟驱动系统设备并引入确定性延迟。在8b10b编码下,建议的最大速度增加到12.5Gbps。JESD204C将通道速率提高到32Gbps,并改为使用CRC和FEC的64b66b编码。新的JESD204D目前正在开发中,该版本将使用带有RS-FEC的PAM 4将通道速率提高到116G。

2

转换器面向数据的框架

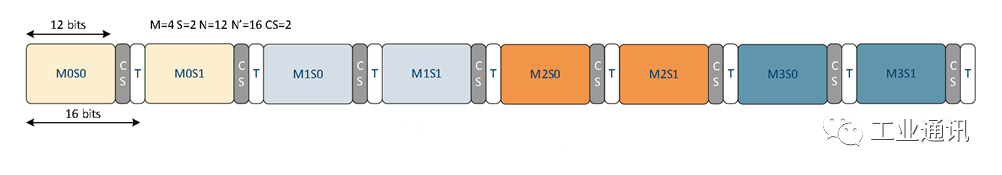

01 JESD输入参数数据

• M - 每个链接的转换器

• S - 每个转换器的样本

• N - 每个样本的位数(分辨率)

• CS - 每个样本的控制位

• N' - 样本容器 N' >= N+CS

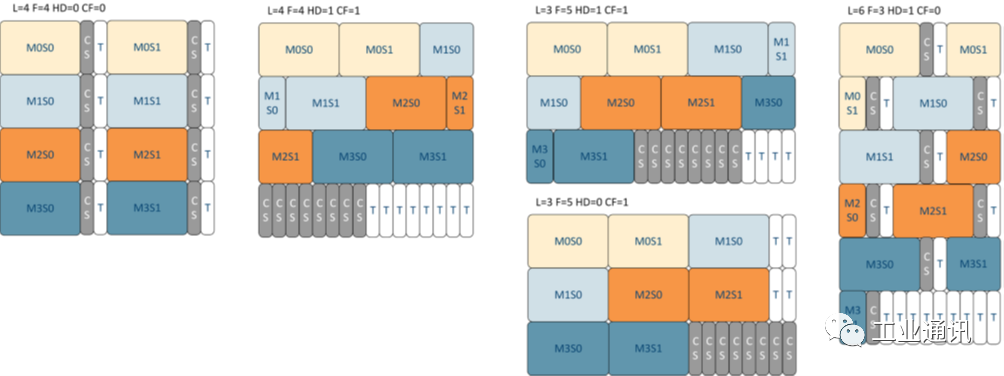

02 JESD成帧参数

• L - 每个链路的通道

• F - 每通道帧中的8位字节

• K - MultiFrame (204B) 中的帧

• E - 扩展多块中的多块 (204C)

• HD - 高密度(允许样品拆分)

• CF - 控制帧(帧末尾的 CS)

转换器样本连续组合成一个帧,然后跨通道拆分

3

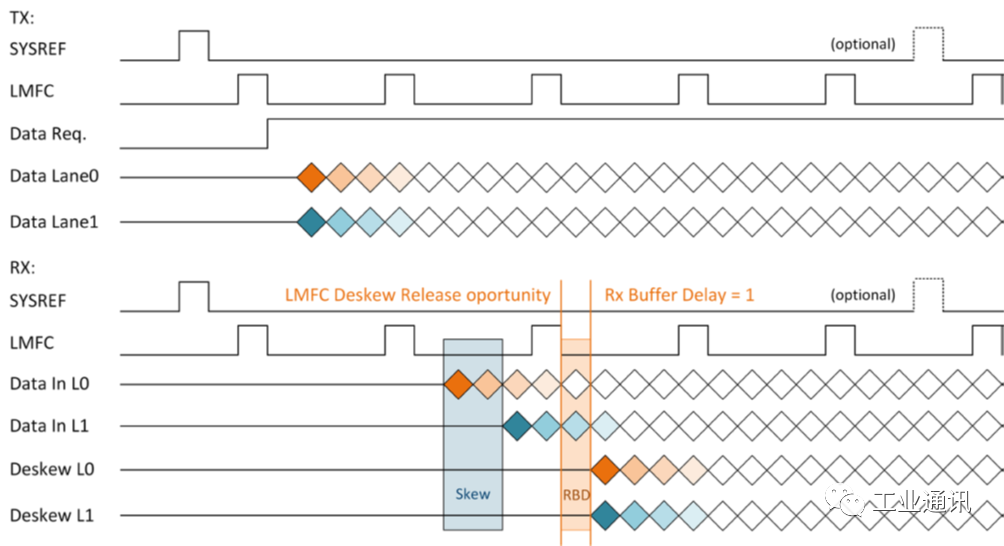

确定性延迟

JESD204B中引入的确定性延迟允许系统在整个复位、上电周期以及重新初始化事件中保持恒定的系统延迟。在大多数情况下,这是通过提供一个系统参考信号 (SYSREF) 来实现的,该信号在发送器和接收器之间建立一个公共时序参考,并允许系统补偿任何延迟可变性或不确定性。

4

主要陷阱和隐患

围绕JESD204标准进行系统设计的主要陷阱和隐患将涉及子类1中的系统时钟,其中确定性延迟是通过使用SYSREF实现的,SYSREF的生成和在不同系统条件下的利用也很关键。选择正确的帧格式和SYSREF类型来匹配系统时钟的稳定性和链路延迟十分具有挑战性。

规范对处理CRC和FEC的比特顺序并不总是很清楚,技术图纸与真值表不匹配,这种差异会导致不同的实现方式,造成不兼容问题。虹科合作伙伴Comcores已经采取了措施来防止这些陷阱和隐患,如位的交换。如果需要这方面的技术支持,欢迎联系虹科技术工程师。

为什么选择

虹科JESD204 IP?

/ Comcores

虹科Comcores JESD204 IP已在所有主要代工厂和低至5nm的工艺中进行了多次流片。此外,该JESD IP已通过与所有主要数据转换器和SerDes/PHY的互操作性测试,从而实现了高度兼容的设计。

-

一种连接数据转换器和逻辑器件的高速串行接口—JESD204介绍2024-04-19 3659

-

AD9683的引脚如何与zynq 7015芯片中的JESD204 ip核端口对应相连?2023-12-15 816

-

虹科即将亮相JESD204网络研讨会2022-02-23 1943

-

宽带数据转换器应用的JESD204B与串行LVDS接口考量2021-11-03 3187

-

LTC2274:16位、105Msps串行输出ADC(JESD204)数据表2021-04-28 801

-

为什么我们要重视JESD204?2021-04-13 1826

-

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?2021-04-06 2958

-

JESD204——它是什么?2021-01-04 3953

-

JESD204评估许可证问题2020-03-11 1744

-

采用JESD204标准的高速串行接口的应用2019-07-05 3696

-

JESD204B串行接口时钟的优势2019-06-19 3654

-

JESD204标准解析2019-06-17 3263

-

JESD204接口简介2019-05-29 2540

-

什么是JESD204B标准为什么需要关注JESD204B接口2019-05-13 13845

全部0条评论

快来发表一下你的评论吧 !