虹科干货 | 如何测试与验证复杂的FPGA设计(1)——面向实体或块的仿真

描述

IP核的开发过程中,面临着许多关键技术,比如IP核的规格定义、基于接口的设计、IP核测试存取结构标准、IP核的验证与打包等。对于IP核的验证,主要是建立参照模型和测试平台,然后进行回归测试和形式验证。这里参照的模型主要用于对系统功能进行验证以及和RTL模型的对照验证,该模型主要用Verilog HDL等语言来构造。测试平台的建立与子模块设计并行,搭建验证环境和开发测试用例,并针对IP核的行为级模型对测试环境和测试用例进行调试,从而同步准备好用来仿真测试RTL级IP核的验证环境和测试用例。

仿真和验证是开发任何高质量的基于 FPGA 的 RTL 编码过程的基础。在本系列文章中,我们将分享我们设计过程中的关键步骤,并将基于虹科以太网IP核产品组合进行介绍。

整个过程的关键步骤如下:

面向实体/块的仿真:通过在每个输入信号上生成激励并验证 RTL 代码行为是否符合预期,对构成每个 IP 核的不同模块进行实体/块的仿真。

面向全局的仿真:一旦不同的模块被单独验证,则意味着下一步将整个IP仿真为单个 UUT(被测试单元)。

(On)硬件测试:尽管扩展的仿真计划提供了良好的可信度,但仍有许多corner的情况无法在虚拟环境中验证。对于这些情况,需要基于硬件的测试计划,这也是获得高质量结果的最后一步。

在本篇文章中,我们将描述第一步:IP 仿真的实体或块级别是如何完成的。

面向实体或块的仿真

“面向实体或块的仿真”这一步骤意味着验证在 IP 核内具有特定操作的特定实体或模块的正确操作。每个 IP 核都由许多实体或块组成,为了测试它们,每个实体会有不同的测试平台,通过在输入受到刺激时观察设计的输出来执行设计。这将有助于检查预期的行为。

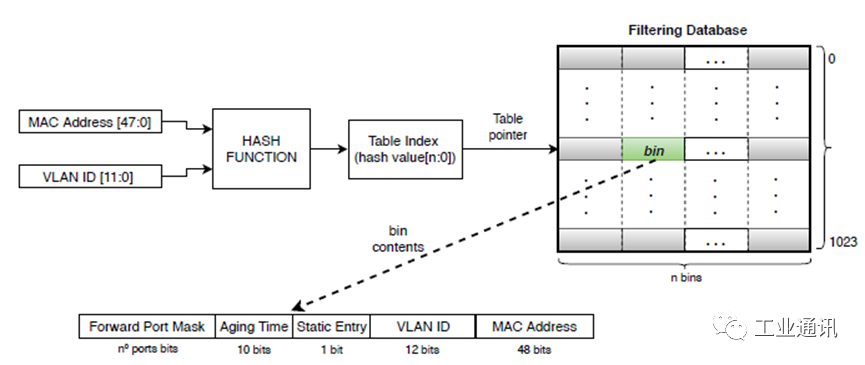

举个例子就可以很好地理解这个步骤。下面我们先介绍虹科以太网交换机 IP 核的过滤数据库。过滤数据库存储 MAC 地址及其相关信息以做出帧转发决策。它是一个基于哈希的存储器,每个地址条目都有一些存储过滤数据的 bin。该哈希算法还生成过滤数据库内存的索引。

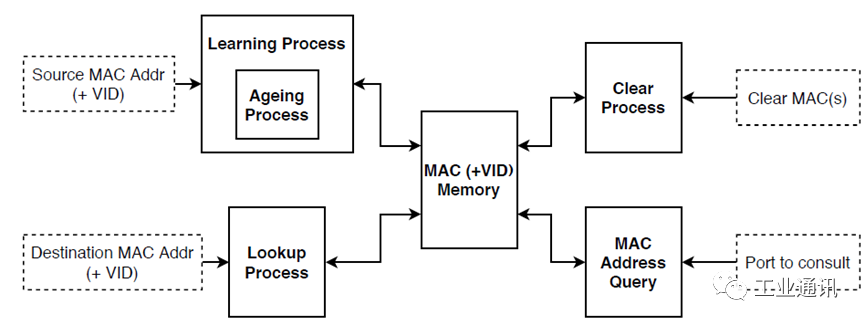

过滤数据库执行有三个主要过程:学习、查找和老化

学习过程负责在满足不同条件时保存帧。

查找过程是在过滤数据库中搜索并获得帧的转发端口掩码的过程。

老化过程根据给定的时间段删除旧的 MAC 条目。

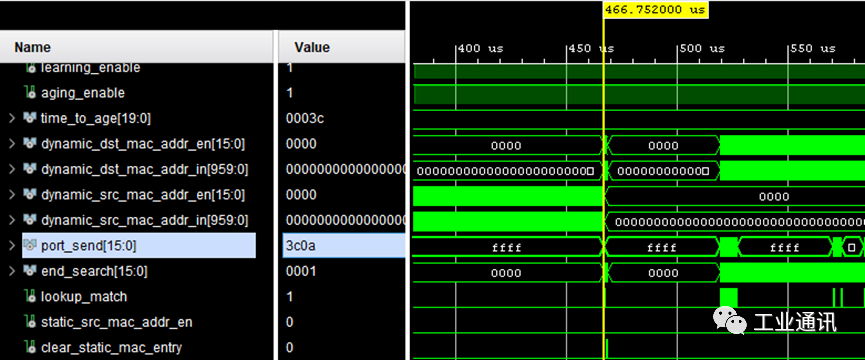

在这个仿真MAC表的具体案例中,请始终尝试测试构成过滤数据库功能的所有机制。从这个意义上说,就像学习不同的MAC,不同的查询、老化是并行完成的,最后需要清除MAC表并验证所有条目都已删除。此外,研究并始终能够测试可能的corner案例也十分重要。

测试和验证复杂 FPGA 设计的第二个关键步骤将在下一篇文章中展开介绍。一旦形成 IP 核的所有实体都按预期工作,全局仿真就会发挥作用。

未完待续

IP核可以使开发人员减少工作量,并缩短产品上市时间。虹科目前已有丰富的IP核产品组合,包括TSN IP核、HSR/PRP IP核、以太网IP核、冗余IP核等,可以轻松集成到用户的FPGA中。若想了解更多信息,欢迎通过sales@hkaco.com联系虹科工业控制团队!

-

FPGA设计的仿真验证概述2019-04-10 2714

-

力科推出仿真设计验证工具2010-02-03 1041

-

科梁基于eFPGAsim的电机硬件在环测试系统2017-08-09 3628

-

【课程笔记分享】面向复杂无线电环境的频谱监测与射频测试方案2022-04-16 1084

-

干货 | 虹科KPA MoDK运行环境与搭建步骤(3)——MoDK例程测试2022-01-19 1754

-

虹科干货 | 如何测试与验证复杂的FPGA设计(1)——面向实体或块的仿真2022-06-10 1016

-

测试与验证复杂的FPGA设计(2)——如何在虹科的IP核中执行面向全局的仿真2022-06-15 1341

-

虹科干货 | 如何测试与验证复杂的FPGA设计(3)——硬件测试2022-06-18 2154

-

虹科干货 | 简单几步教您安装虹科Matrikon Excel Reports软件2022-07-14 1523

-

虹科干货 | 如何通过JMobile软件实现虹科物联网HMI/网关的报警功能2022-07-19 1471

-

虹科干货 | 虹科物联网HMI/网关结合JMobile软件实现调度器功能2022-11-16 1427

-

虹科干货 | 这些预测性维护的专业术语你都了解吗?2023-02-01 1669

-

虹科干货 | 带你玩转虹科HMI中的表格控件!2023-03-29 1273

-

虹科干货 | 虹科Panorama SCADA平台连接OPC UA服务器操作详解2023-04-17 1859

-

虹科在上海汽车测试展和IME的精彩表现2023-08-18 1277

全部0条评论

快来发表一下你的评论吧 !