白皮书 I 基于组网分割的超大规模设计 FPGA原型验证解决方案

描述

引言

Preface

如何快速便捷的完成巨型原型验证系统的组网,并监测系统的连通性及稳定性?

如何将用户设计快速布局映射到参与组网的原型验证系统的每一块 FPGA?

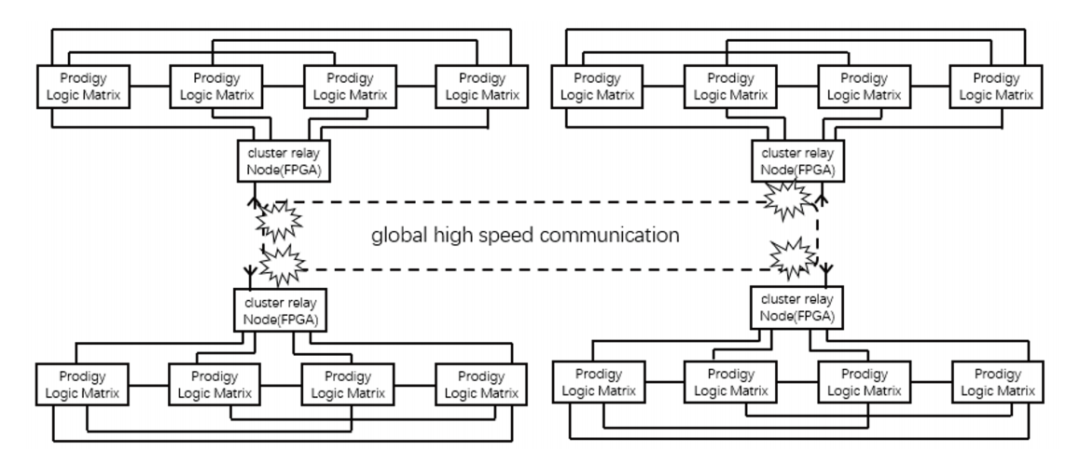

随着用户设计规模的日益增大,传统基于单片 FPGA 或单块电路板的原型验证系统已经远远不能满足用户的设 计验证需求,设计团队常需以灵活组网的方式,将数十甚至上百台原型验证系统“组装”为一个完整的巨型原 型验证系统。鉴于此,以上两个问题成为了亟需解决的问题。

本次国微思尔芯白皮书《基于组网分割的超大规模设计 FPGA原型验证解决方案》阐述了S2C对客户超大型设计的原型验证,从硬件系统的组建,FPGA 互连组网,外设接口的可扩展性,时钟及复位等 全局信号同步性处理,到基于 RTL 或 netlist 的设计分割算法,系统级静态时序分析,增量式设计分割版本迭代的等新挑战的解决思路。

核心内容

Main Point

基于组网的人工可干预聚类分割

如何快速完成硬件组网并正确将用户设计分割映射到每一片 FPGA?欢迎下载了解以下内容:

硬件组网资源

组网拓扑定义

基于 RTL 级的聚类分割方案

基于 netlist 级的 TDM 模块插入

半自动化工具库

常见标准组网

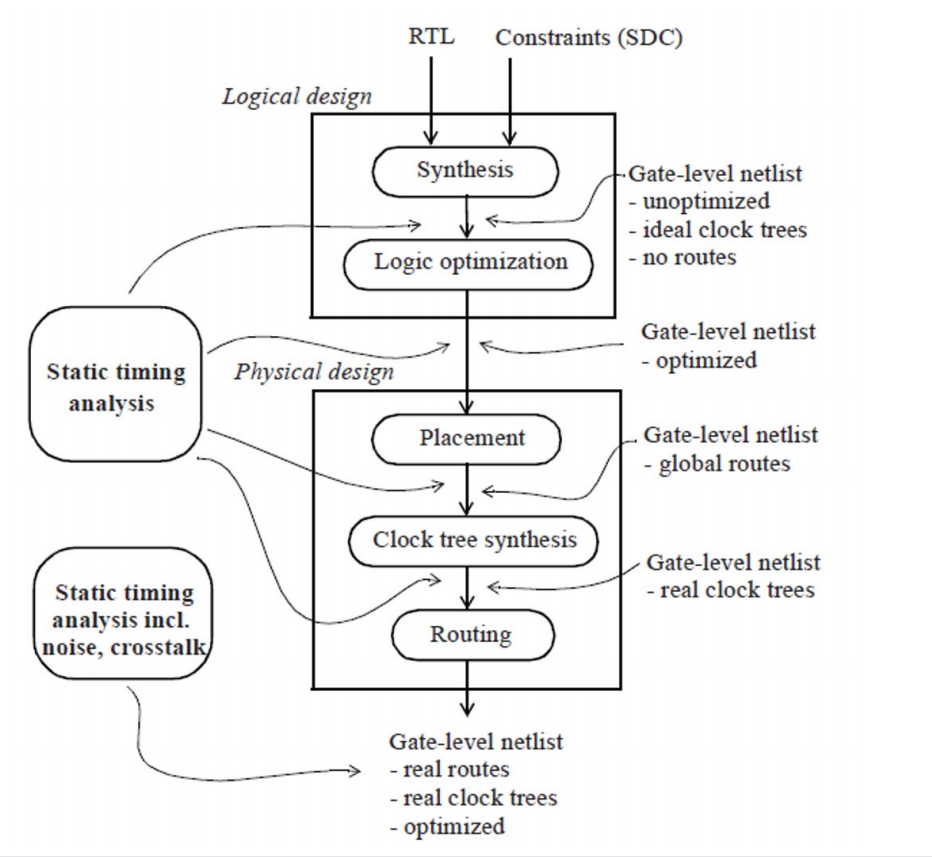

组网聚类分割后的系统静态时序分析与仿真

如何保证分割后设计运行时的稳定性,并优化设计的运行速度?欢迎下载了解以下内容:

系统级静态时序分析 SSTA

STA的限制和不足

数字电路设计中的静态时序分析

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- F

-

超大规模芯片验证:基于AMD VP1902的S8-100原型验证系统实测性能翻倍2025-06-06 1653

-

大规模集成电路逻辑PCI Express MegaRAID白皮书2023-08-16 612

-

《大规模光电集成赋能智能算力网络白皮书》概述2023-06-12 3375

-

i.MX 7ULP产品白皮书2022-12-13 746

-

国微思尔芯发布高密原型验证系统解决方案白皮书2021-12-08 2610

-

IPTV服务质量白皮书2019-10-14 2866

-

用两块Kintex超大规模FPGA开发单板应该如何为两个FPGA供电?2019-04-03 1930

-

Xilinx的超大规模FPGA产品选择指南免费下载2019-02-19 962

-

S2C公司发布超大规模设计的FPGA原型系统2018-06-29 6231

-

连接器顶级专家TE白皮书下载,猜猜哪条方案最受欢迎?答对送积分哦2018-04-20 18430

-

简仪科技怒对LabVIEW的白皮书2017-08-11 18089

-

ZigBee白皮书2012-08-20 10335

-

【经典】智能电网白皮书资料汇编2010-12-23 4008

-

BFD技术白皮书 华为2009-12-12 5538

全部0条评论

快来发表一下你的评论吧 !