жҠҖжңҜиө„и®Ҝ | ејҖе…ізЁіеҺӢз”өи·Ҝдёӯзҡ„еҜ„з”ҹеҷӘеЈ°

жҸҸиҝ°

жүҖжңүзҡ„PCB еёғеұҖйғҪжңүеҜ„з”ҹеӣ зҙ пјҢдҪҶиҝҷдәӣеӣ зҙ 并дёҚдјҡжҖ»жҳҜз»ҷжӮЁзҡ„з”өи·ҜеёҰжқҘйҮҚеӨ§й—®йўҳгҖӮеңЁжҹҗдәӣз”өи·ҜдёӯпјҢе®ғ们еҸҜиғҪйқһеёёйә»зғҰпјҢ并且йңҖиҰҒдёҖдәӣйўқеӨ–зҡ„з”өи·ҜжқҘйҳІжӯўз”ұеҜ„з”ҹеӣ зҙ еј•иө·зҡ„еҷӘеЈ°й—®йўҳгҖӮе…ёеһӢзҡ„дҫӢеӯҗжҳҜејҖе…ізЁіеҺӢз”өи·ҜпјҢе®ғеңЁз»„件е’Ң PCB еёғеұҖдёӯйңҖиҰҒиҖғиҷ‘йҮҚиҰҒзҡ„еҜ„з”ҹеҸӮж•°гҖӮеҜ„з”ҹж•Ҳеә”еңЁејҖе…ізЁіеҺӢз”өи·Ҝзҡ„ PCB еёғеұҖдёӯзҡ„д»ҘдёӢеҢәеҹҹдёӯзү№еҲ«зӘҒеҮәпјҡ

ејҖе…і MOSFET зҡ„з«Ҝеӯҗе’Ңдё»дҪ“дёӯзҡ„з”өж„ҹе’Ңз”өе®№

еҸҚйҰҲеӣһи·Ҝе’Ңй«ҳ dI/dt еӣһи·Ҝдёӯзҡ„еӣһи·Ҝз”өж„ҹпјҲиҫ“е…Ҙе’Ңиҫ“еҮәпјү

PCBеёғеұҖдёӯејҖе…іиҠӮзӮ№е’Ңе…¶д»–еҜјдҪ“д№Ӣй—ҙзҡ„дә’з”өе®№

В

жң¬ж–Үеҗ‘еӨ§е®¶д»Ӣз»ҚдёҖдәӣеҸҜз”ЁдәҺжҺ§еҲ¶жәҗиҮӘиҝҷдәӣеҜ„з”ҹж•Ҳеә”зҡ„еҷӘеЈ°й—®йўҳзҡ„з”өи·Ҝи®ҫи®Ўе’ҢеёғеұҖзӯ–з•ҘгҖӮ

ејҖе…ізЁіеҺӢз”өи·Ҝдёӯзҡ„еҜ„з”ҹй—®йўҳ

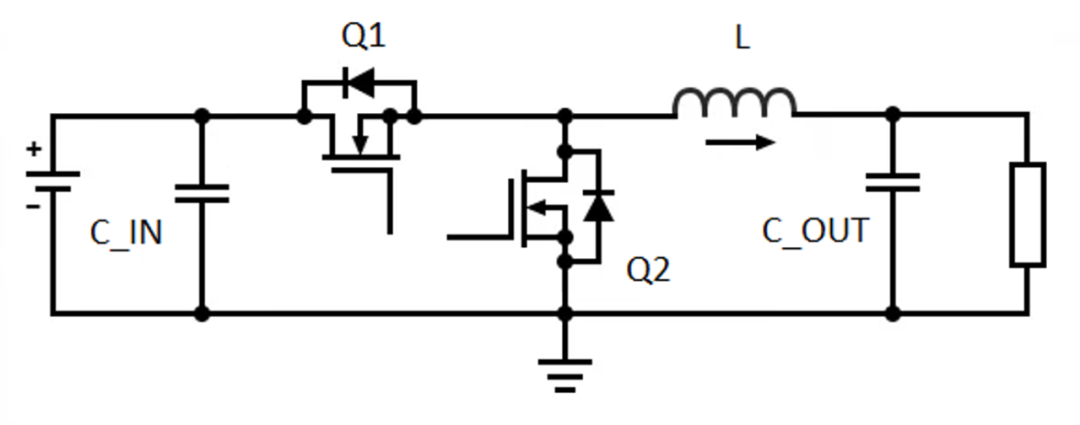

еҰӮжһңе°ҶејҖе…ізЁіеҺӢз”өи·ҜеҺҹзҗҶеӣҫдёҺиҝҷдәӣеҷЁд»¶зҡ„ PCB еёғеұҖиҝӣиЎҢжҜ”иҫғпјҢеҫҲе®№жҳ“зңӢеҮә PCB еёғеұҖдёӯеҸҜиғҪеӯҳеңЁеҜ„з”ҹж•Ҳеә”гҖӮеңЁиҝҷдәӣи®ҫи®ЎдёӯпјҢеҜ„з”ҹз”өе®№е’Ңз”өж„ҹдјҡдә§з”ҹдёҠиҝ°еҷӘеЈ°й—®йўҳпјҢдҪҶдёҖдәӣз®ҖеҚ•зҡ„и®ҫи®Ўзӯ–з•ҘеҸҜд»Ҙеё®еҠ©жҠ‘еҲ¶иҝҷдәӣеҷӘеЈ°й—®йўҳгҖӮеңЁжҺҘдёӢжқҘзҡ„зӨәдҫӢдёӯпјҢжҲ‘们е°ҶдҪҝз”Ёд»ҘдёӢйҷҚеҺӢиҪ¬жҚўз”өи·ҜжқҘиҜҙжҳҺиҝҷдәӣеҺҹзҗҶпјҢзӣёеҗҢзҡ„ж–№жі•д№ҹйҖӮз”ЁдәҺе…¶д»–жӢ“жү‘з»“жһ„гҖӮ

ж ҮеҮҶйҷҚеҺӢиҪ¬жҚўеҷЁжӢ“жү‘

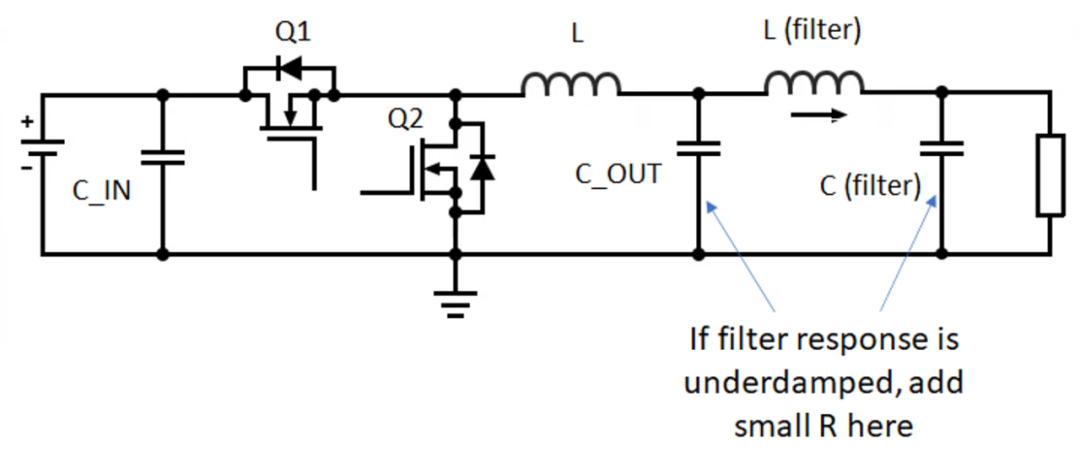

пјҲдёҖпјүгҖҒи®ҫи®Ўиҫ“еҮәж»ӨжіўеҷЁйҷҚдҪҺејҖе…іеҷӘеЈ°зҡ„дёҖз§Қж–№жі•жҳҜеңЁиҫ“еҮәз«Ҝж”ҫзҪ®дёҖдёӘж»Өжіўз”өи·ҜгҖӮиҝҷйҖҡеёёз”ЁдәҺиҫ“еҮәзә§иҒ”зҡ„ LC з”өи·ҜпјҢеҰӮдёӢжүҖзӨәгҖӮеңЁжң¬дҫӢдёӯпјҢз”өе®№еҷЁе°Ҷе…·жңүдёҖдәӣжңүж•ҲдёІиҒ”з”өйҳ» (ESR)пјҢйҖҡеёёиҝңе°ҸдәҺ 1 О©гҖӮ

В

йҷҚеҺӢиҪ¬жҚўеҷЁиҫ“еҮәж»ӨжіўеҷЁзӨәдҫӢгҖӮ

иҝҷз§Қи®ҫи®Ўзҡ„жҢ‘жҲҳжҳҜйңҖиҰҒзЎ®дҝқж–°зҡ„ж»ӨжіўеҷЁе…ғ件дёҚдјҡдёәз”өи·Ҝзҡ„дј йҖ’еҮҪж•°еўһеҠ дёҖдёӘйўқеӨ–зҡ„жһҒзӮ№пјҢиҝҷдјҡеҜјиҮҙж—¶еҹҹдёӯзҡ„ж¬ йҳ»е°јжҢҜиҚЎпјҲжҢҜй“ғпјүгҖӮжҠ‘еҲ¶д»»дҪ•зһ¬жҖҒе“Қеә”зҡ„жңҖз®ҖеҚ•ж–№жі•жҳҜдҪҝз”ЁжӣҙеӨ§зҡ„з”өе®№еҷЁпјҢ并еңЁз”өе®№еҷЁдёҠдёІиҒ”дёҖдёӘе°Ҹз”өйҳ»еҷЁпјҲд»…еҮ О©пјүгҖӮиҝҷйҮҢйңҖиҰҒиҝӣиЎҢдёҖдәӣе®һйӘҢе’Ңд»ҝзңҹпјҢд»ҘзЎ®дҝқжІЎжңүиҝҮеӨҡзҡ„зһ¬жҖҒжҢҜиҚЎпјҢ并确дҝқйҖӮеҪ“ең°жҠ‘еҲ¶ејҖе…іеҷӘеЈ°гҖӮпјҲдәҢпјүжӯЈзЎ®и®ҫи®ЎдәӨжҚўиҠӮзӮ№еҮҶзЎ®дј°и®ЎејҖе…іиҠӮзӮ№зҡ„з”өе®№пјҢд»ҘзЎ®дҝқз”өе®№дёҺй«ҳз«Ҝе’ҢдҪҺз«Ҝ MOSFET з”өе®№зӣёжҜ”дёҚдјҡеӨӘй«ҳгҖӮдҪңдёәдёҖиҲ¬и§„еҲҷпјҢејҖе…іиҠӮзӮ№еҝ…йЎ»и¶іеӨҹеӨ§пјҢд»ҘжөҒйҖҡжүҖйңҖзҡ„з”өжөҒпјҢдҪҶеҸҲиҰҒи¶іеӨҹе°ҸпјҢд»Ҙе…·жңүдҪҺз”өе®№гҖӮеҰӮжһңејҖе…іиҠӮзӮ№з”өе®№еӨӘеӨ§пјҢеҲҷеҸҜиғҪйңҖиҰҒе°Ҷе…¶е°әеҜёзј©е°ҸпјҢд»ҘзЎ®дҝқз”өжөҒйҷҗеҲ¶еңЁејҖе…і MOSFET дёӯпјҢиҖҢдёҚжҳҜйҖҡиҝҮеҜ„з”ҹз”өе®№иҖҰеҗҲгҖӮ

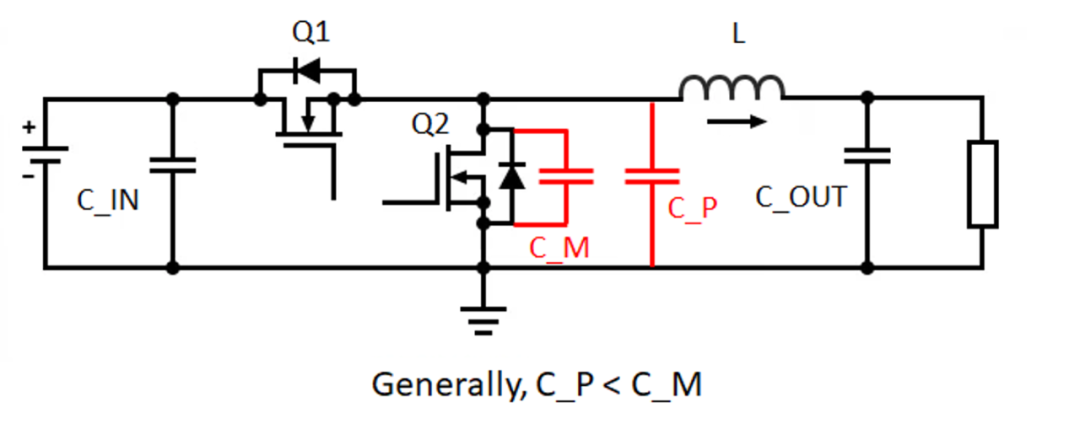

ејҖе…іиҙҹиҪҪз”өе®№дёҺдҪҺз«Ҝ MOSFET з”өе®№гҖӮ

еҖјеҫ—еәҶе№ёзҡ„жҳҜпјҢдёҺдёҠйқўзӨәдҫӢйҷҚеҺӢиҪ¬жҚўеҷЁдёӯжүҖзӨәзҡ„дҪҺз«Ҝ MOSFET з”өе®№зӣёжҜ”пјҢејҖе…іиҠӮзӮ№з”өе®№йҖҡеёёйқһеёёе°ҸгҖӮ

- ејҖе…іиҠӮзӮ№з”өе®№пјҡзәҰ 24 pF/sqгҖӮmmпјҲеҒҮи®ҫеҹәжқҝ Dk = 4пјҢеҺҡеәҰ = 0.1 mmпјҢиҫ№зјҳеӣ еӯҗдёә 4пјү

- l MOSFET DS з”өе®№пјҡеӨ§зәҰ 1-10 nF

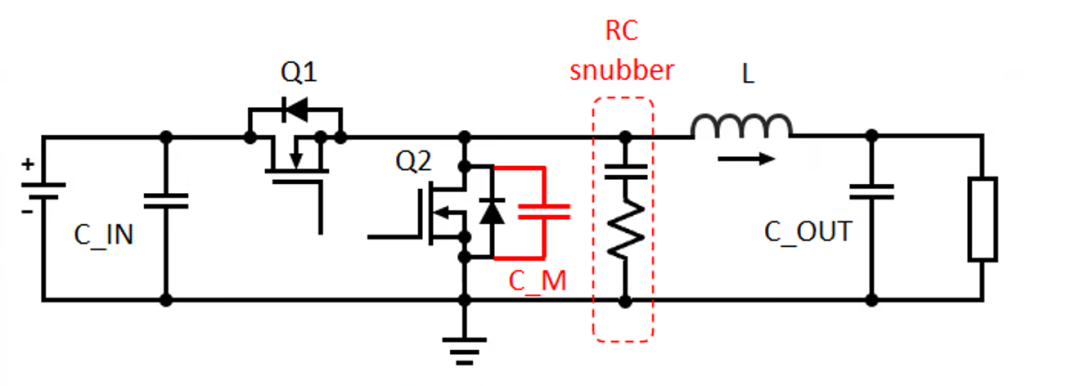

иҝҷж„Ҹе‘ізқҖпјҢеҜ№дәҺе…·жңүй«ҳз”өе®№зҡ„зү©зҗҶеӨ§еһӢ MOSFETпјҢејҖе…іиҠӮзӮ№иҮіе°‘йңҖиҰҒ 40 е№іж–№жҜ«зұіпјҢд»Ҙе…Ғи®ёеҷӘеЈ°з»•иҝҮдҪҺдҫ§ MOSFET 并еҲ°иҫҫжҺҘең°зҪ‘з»ңгҖӮеӣ жӯӨпјҢжҲ‘们йҖҡеёёеҸҜд»ҘеҝҪз•ҘејҖе…іиҠӮзӮ№еҜ№ GND зҡ„з”өе®№гҖӮжӣҙйҮҚиҰҒзҡ„жҳҜдёҺе…¶д»–з”өи·Ҝзҡ„дә’з”өе®№пјҢе®ғе…Ғи®ёеңЁй«ҳ dV/dt ж‘Ҷе№…дёӢиҝӣиЎҢеҷӘеЈ°иҖҰеҗҲгҖӮдҪҝжҺҘең°жӣҙйқ иҝ‘ејҖе…іиҠӮзӮ№жңүеҠ©дәҺеҮҸе°‘иҝҷз§Қдә’з”өе®№гҖӮпјҲдёүпјүгҖҒRC зј“еҶІеҷЁеҪ“жҲ‘们еңЁејҖе…ізЁіеҺӢеҷЁж–№йқўжҸҗеҲ° RC зј“еҶІеҷЁж—¶пјҢе®ғиў«ж”ҫзҪ®еңЁдҪҺз«Ҝ MOSFET дёҠпјҢеҰӮдёӢжүҖзӨәгҖӮ

В

RC зј“еҶІеҷЁж”ҫзҪ®еңЁејҖе…ізЁіеҺӢеҷЁз”өи·ҜдёӯгҖӮ

еҰӮжһң RC ж”Ҝи·Ҝе…·жңүи¶іеӨҹй«ҳзҡ„йҳ»жҠ—пјҲеңЁ MOSFET зҡ„еӣәжңүйў‘зҺҮдёӢйҖҡеёёдёәеҮ О©пјүпјҢеҲҷеҸҜд»ҘжҠ‘еҲ¶ MOSFET зҡ„ејҖе…ізһ¬жҖҒе“Қеә”гҖӮжӯӨ RC ж”Ҝи·Ҝзҡ„и®ҫи®Ўе’Ңд»ҝзңҹйңҖиҰҒдёҖдёӘзІҫзЎ®зҡ„ MOSFET з”өи·ҜжЁЎеһӢпјҢе…¶дёӯеҝ…йЎ»еҢ…жӢ¬еҜ„з”ҹж•Ҳеә”пјҢд»ҘдҫҝжӯЈзЎ®и®Ўз®—е’Ңд»ҝзңҹгҖӮжҖ»з»“

дёҺеҫҖеёёдёҖж ·пјҢеңЁе®һж–Ҫи§ЈеҶі PCB еёғеұҖжҲ–з”өи·Ҝи®ҫи®Ўдёӯзҡ„еҜ„з”ҹй—®йўҳзҡ„и§ЈеҶіж–№жЎҲж—¶пјҢиҜ·еҠЎеҝ…д»ҝзңҹжӮЁзҡ„жғіжі•гҖӮеңЁиҝҷз§Қжғ…еҶөдёӢпјҢжүҖйңҖзҡ„д»ҝзңҹеҢ…жӢ¬зһ¬жҖҒеҲҶжһҗе’Ңйў‘зҺҮжү«жҸҸпјҢд»ҘиҜ„дј°йҷ„еҠ з”өи·ҜйғЁеҲҶе°ҶеҰӮдҪ•дҪңз”ЁдәҺжӮЁзҡ„ејҖе…ізЁіеҺӢеҷЁз”өи·ҜгҖӮ

жҖ»зҡ„жқҘиҜҙпјҢдёӢйқўиҝҷдәӣ PCB и®ҫи®Ўе’ҢеёғеұҖе»әи®®еҸҜд»Ҙеё®еҠ©жӮЁжҠ‘еҲ¶з”өжәҗи°ғиҠӮеҷЁз”өи·Ҝдёӯзҡ„еҷӘеЈ°пјҡ

1. дҪҝең°жӣҙйқ иҝ‘ејҖе…іиҠӮзӮ№

2. дҪҝз”Ёжӣҙе°Ҹзҡ„дәӨжҚўиҠӮзӮ№

3. еҰӮжһңMOSFETжҢҜй“ғеӨӘеӨ§пјҢиҜ·дҪҝз”Ё RC зј“еҶІз”өи·Ҝ

4. дҪҝз”Ёе…·жңүдёҙз•Ңйҳ»е°је“Қеә”зҡ„иҫ“еҮәж»ӨжіўеҷЁжқҘйҷҚдҪҺејҖе…іеҷӘеЈ°пјҢиҖҢдёҚдјҡдә§з”ҹж–°зҡ„зһ¬жҖҒжҢҜй“ғй—®йўҳ

В

еҪ“жӮЁйңҖиҰҒи®ҫи®Ўе’Ңд»ҝзңҹжӮЁзҡ„ејҖе…ізЁіеҺӢеҷЁз”өи·Ҝ并йӘҢиҜҒеҜ„з”ҹз”өе®№зҡ„еҪұе“Қж—¶пјҢCadenceзҡ„PSpiceжҳҜдёҡз•ҢжңҖдҪізҡ„з”өи·Ҝи®ҫи®Ўе’Ңд»ҝзңҹе·Ҙе…·гҖӮPSpice з”ЁжҲ·еҸҜд»Ҙи®ҝй—®ејәеӨ§зҡ„ SPICE жЁЎжӢҹеҷЁд»ҘеҸҠдё“дёҡи®ҫи®ЎеҠҹиғҪпјҢеҰӮжЁЎеһӢеҲӣе»әгҖҒеӣҫеҪўе’ҢеҲҶжһҗе·Ҙе…·зӯүзӯүгҖӮ

В

- зӣёе…іжҺЁиҚҗ

- зғӯзӮ№жҺЁиҚҗ

- з

-

ејҖе…ізЁіеҺӢз”өжәҗ--еҺҹзҗҶгҖҒи®ҫи®ЎдёҺе®һз”Ёз”өи·Ҝ2025-06-24 552

-

[еҲҶдә«]й«ҳйў‘ејҖе…іеһӢзЁіеҺӢз”өжәҗзҡ„з”өзЈҒеҷӘеЈ°й—®йўҳ2009-03-11 3582

-

ејҖе…ізЁіеҺӢз”өжәҗзҡ„и®ҫи®ЎдёҺеә”з”Ё2016-06-11 11695

-

ејҖе…ізЁіеҺӢз”өжәҗе’ҢзәҝжҖ§зЁіеҺӢз”өжәҗ2018-10-12 2940

-

йҷҚеҺӢзЁіеҺӢеҷЁз”өи·ҜдёӯеҪұе“ҚEMIжҖ§иғҪе’ҢејҖе…іжҚҹиҖ—зҡ„ж„ҹжҖ§е’Ңе®№жҖ§еҜ„з”ҹе…ғзҙ2020-11-03 2180

-

ејҖе…іејҸзЁіеҺӢз”өи·Ҝзҡ„е·ҘдҪңеҺҹзҗҶ2021-11-12 2328

-

зәҝжҖ§зЁіеҺӢз”өжәҗе’ҢејҖе…ізЁіеҺӢз”өжәҗзҡ„дёҚеҗҢ2021-11-16 2518

-

ејҖе…іеһӢзЁіеҺӢз”өжәҗзҡ„еҺҹзҗҶз”өи·Ҝ2009-07-25 1592

-

ејҖе…ізЁіеҺӢз”өжәҗз”өи·Ҝи®ҫи®ЎеҸҠеә”з”Ё2011-11-11 1689

-

ејҖе…ізЁіеҺӢз”өи·ҜдёҺдёІиҒ”зЁіеҺӢз”өи·ҜеҲҶеҲ«жҳҜд»Җд№Ҳ2018-05-15 18882

-

ејҖе…ізЁіеҺӢз”өжәҗзҡ„еҺҹзҗҶгҖҒи®ҫи®ЎдёҺе®һз”Ёз”өи·Ҝ2021-03-18 1642

-

дёІиҒ”зӣҙжөҒзЁіеҺӢзЁіеҺӢз”өи·Ҝ2021-08-31 1333

-

LM2576ејҖе…ізЁіеҺӢз”өжәҗз”өи·Ҝи®ҫи®ЎеҸҠеә”з”Ё2021-09-18 2574

-

ејҖе…ізЁіеҺӢз”өи·Ҝе’ҢдёІиҒ”зЁіеҺӢз”өи·Ҝзҡ„еҢәеҲ«2023-08-18 2761

-

жҠҖжңҜиө„и®Ҝ I еҰӮдҪ•иҜҶеҲ«еҗҢжӯҘејҖе…іеҷӘеЈ°2026-02-13 168

е…ЁйғЁ0жқЎиҜ„и®ә

еҝ«жқҘеҸ‘иЎЁдёҖдёӢдҪ зҡ„иҜ„и®әеҗ§ !