EMC工程问题解答(一)

描述

以下内容来源于EMC实战特训营部分问题解答,希望对大家有一些帮助。

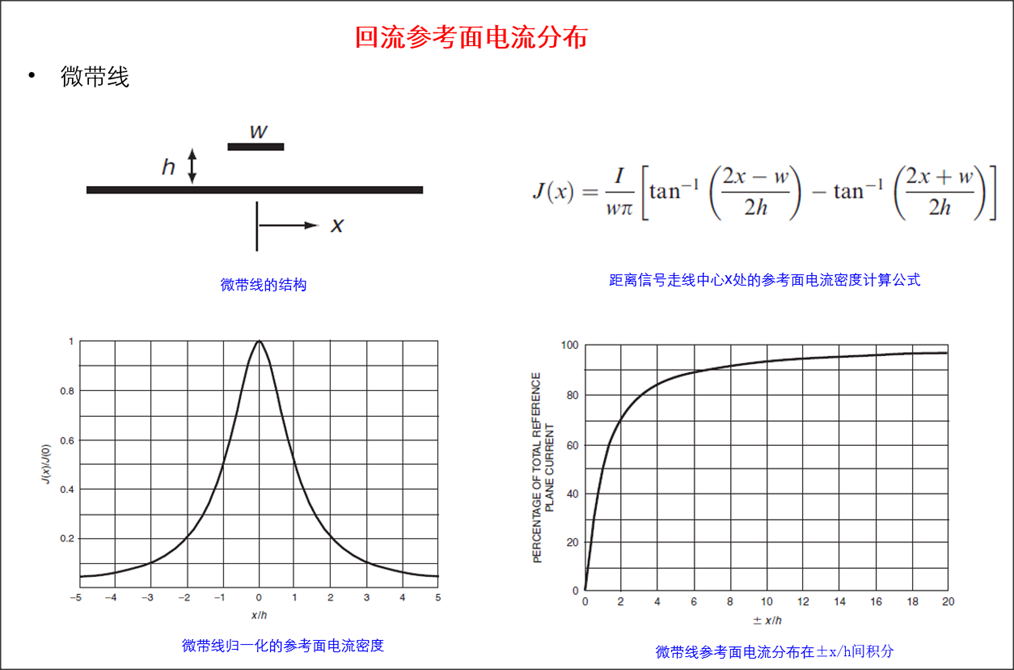

一、距微带线中心范围内回流百分比的数据的有理论计算公式吗?如何净IO的地-通过螺钉导电材料尽可能的接地,请问这个目的是为了降低接地阻抗吗?

答:计算公式可以参考下图所示,J(x)函数是微带线的电流数值计算公式,公式来源于某技术论文。I/O净地的方式就是如你所说的,尽可能降低接口区域的接地阻抗值。

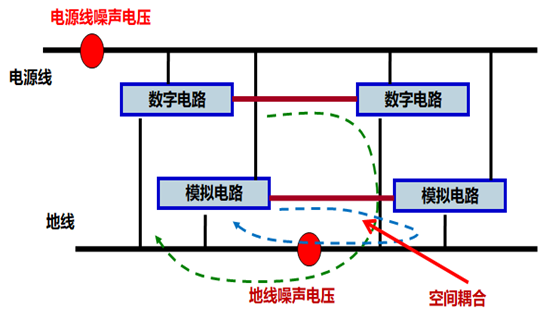

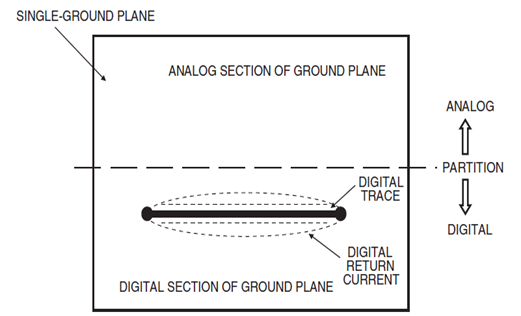

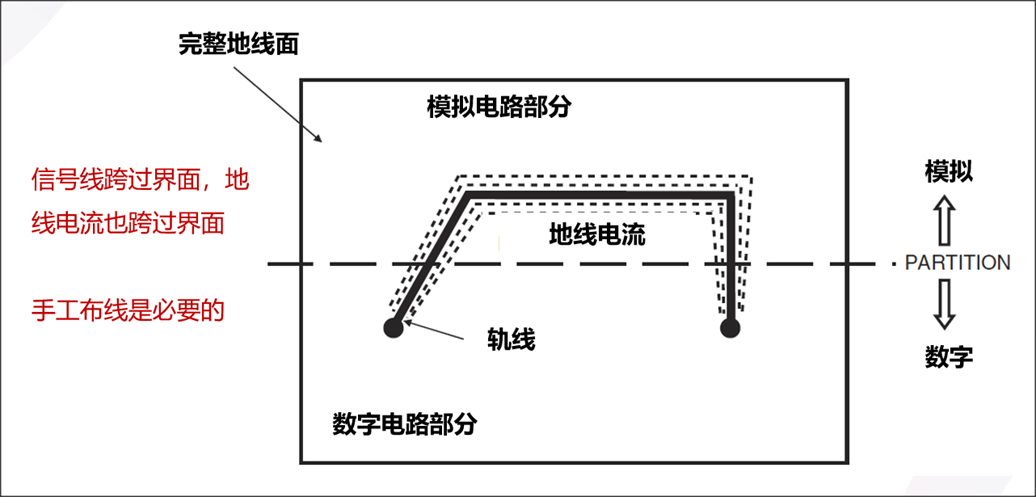

二、对于一些SOC型单片机,封装很小,但同时处理数字和模拟信号分别有数字地、数字电源和模拟地、模拟电源。这时如何做数字和模拟的布局和走线?

答:这时可以不分地处理,但是在PCB走线时候要特别注意,主要避免数字信号可能对模拟信号的影响;主要参考如下图所示的高频信号回流原理,布线严格分区处理,这个知识点我们在PCB环节会重点讲到。

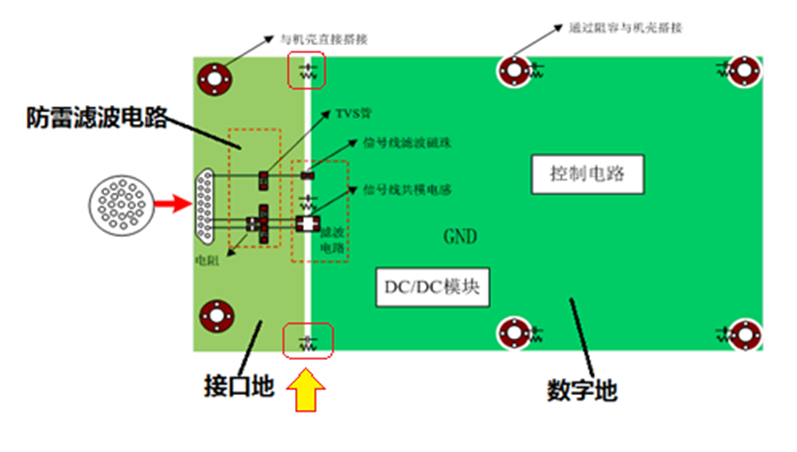

三、产品设计中,接口部分的机壳地与信号地为什么要用1nF电容和1M电阻链接?这样做有什么好处?答:如下图所示,这是我们电磁兼容设计中常用的一种处理方式,主要是针对信号地(GND)是浮地类型的产品。电阻的作用主要是担心GND上在产品长期应用过程中会有静电积累,如果没有泄放通路可能会在薄弱区域形成瞬态击穿,对电路造成损伤,所以采用大电阻的接地方式,既可以满足产品的绝缘设计要求,又能避免ESD的积累损坏效应;电容的功能主要从EMI角度考虑,电容的使用,可以在高频段实现信号地的接地连接,降低信号地与机壳地之间的高频电势差(这个电势差常常是很多辐射问题的共模激励源(天线知识中的单极子天线模型)),从而从PCB整体上降低电路的对外辐射值(特别是接口电路区域)。

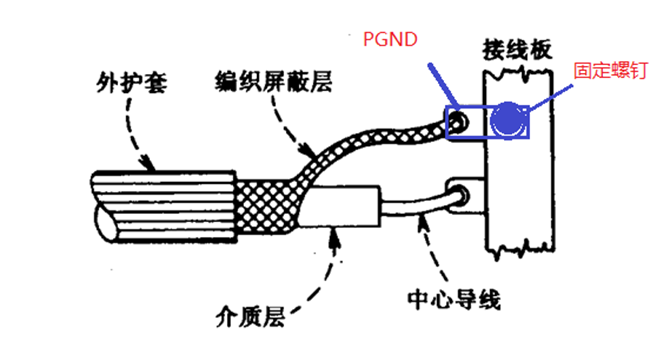

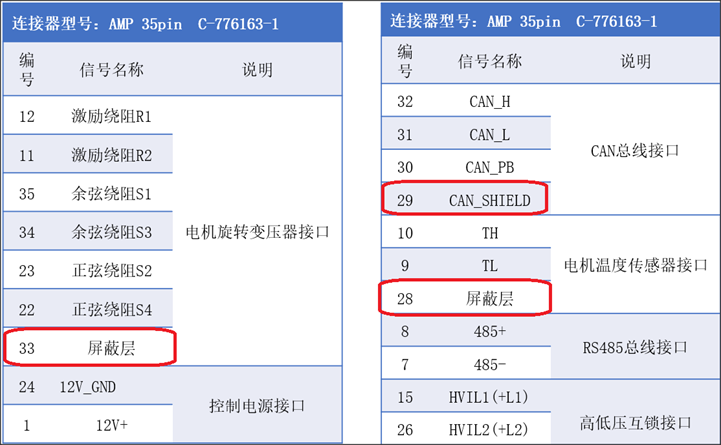

四、如果PCB地和结构地没有进行滤波隔离,是一个地,这时候还需要将屏蔽层的地和信号地分开,分别接到结构上和PCB上吗?

答:从EMC设计角度最好还是分开,因为即使是一个地,因为连接阻抗的原因,PCB上的GND和实际的结构体上的噪声电平还是有差异的,如果屏蔽线连接到GND上,就如同很多资料中提到的猪尾巴效应;当然在一些实际产品的工程设计中,屏蔽层在工艺上很难实现单独接结构件,那么就折中通过板内来实现接地,如汽车电子产品中常见的CAN。

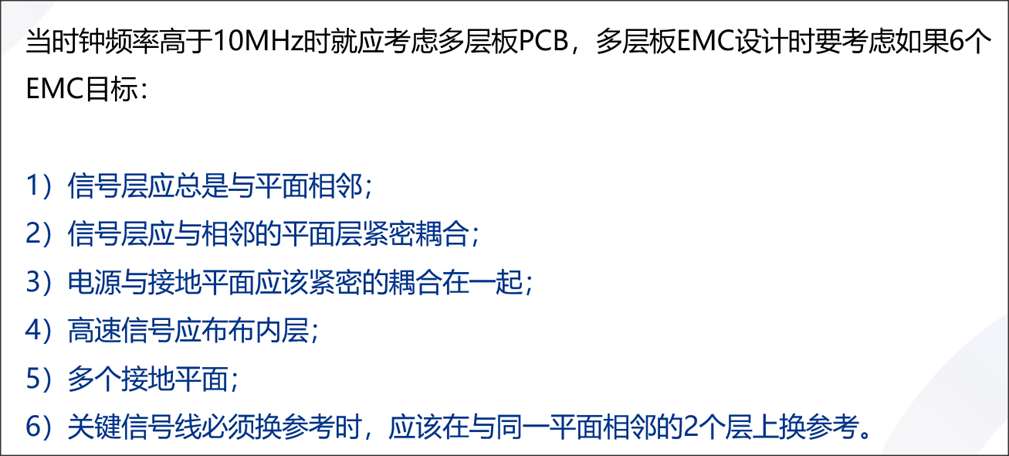

五、设计评估时,PCB层数多肯定好,但增加成本,请教一下从EMC角度,PCB板层数如何选择,以到达最佳性价比?答:这个知识点在后续的PCB课程中会有详细讲解,如果单纯从EMC角度看层叠,下面六条设计原则都能满足基本就是最佳的层叠设计方案了。

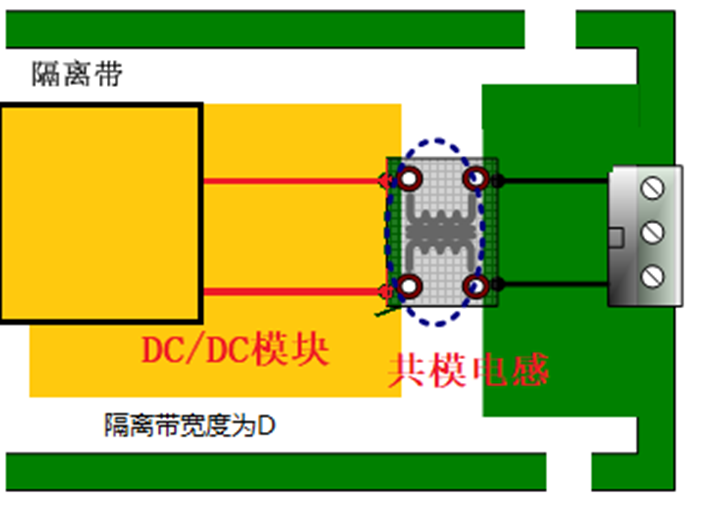

六、共模电感PCB布局时需要把共模电感周边挖空,以四层板为例,只需要挖空第一层的?还是第二层,第三层,第四层全部挖空???另外如果没有隔离带,一般共模电感周边挖空区域多少距离合适?

答:共模电感PCB设计主要是挖电感正下方区域,全部投影层挖空。目的是物理上减小地平面噪声通过地与电感初次级(前后级)分布电容,使得干扰耦合,使得共模电感滤波效果打折。

七、能否解释下共模电感的漏感为什么会对滤波效果有帮助?原理是什么?答:

共模电感是由两个方向相反匝数相同的线圈按照一定规则绕制而成的特殊电感器,它的作用是滤除电路当中的共模电磁干扰信号,那么在实际当中为什么共模电感也能够抑制差模信号?

漏感的产生

了解漏感之前先看一下共模电感的结构。共模电感有两个绕组,而且两个绕组被设计成使它们所流过的电流沿线圈芯传导时方向相反,理论上彼此的磁场相互抵消。但是由于线圈绕制的环形有时候不能绕满一周,或者绕制不够紧密,那么磁就会泄漏出来。因为电感不可能是理想的电感,线圈绕完后,不可能所有磁通都集中在线圈的中心内。

漏感的利用

这种由于漏磁导致产生的电感我们称为"漏感",其实这也就是差模电感。因此,共模电感一般也具有一定的差模干扰衰减能力。虽然产生了差模电感,但是也未必有害,在实际使用当中,有时候还特意设计利用漏感。例如在EMI滤波器中,只安装一个共模电感,利用共模电感的漏感产生适量的差模电感,这样起到对差模电流的抑制作用,相当于有共模电感也有一个小差模电感存在,从而达到更好的滤波效果。

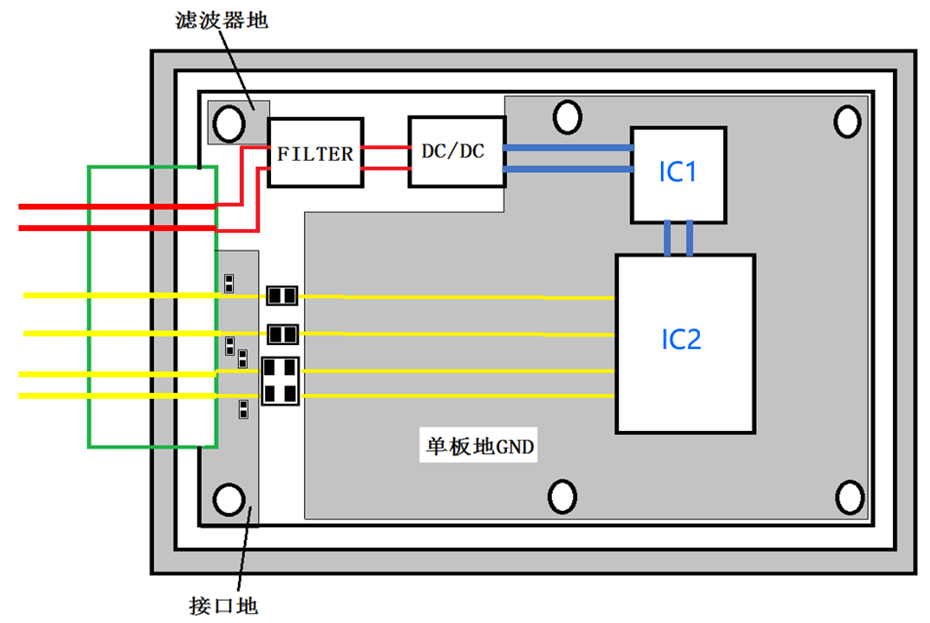

八、个具有金属壳体的产品,其中有dcdc隔离。机壳地、净地、电源地,数字地、模拟地。一般情况应该如何布局?需要注意考虑那些问题。

答:这个关于PCB布局设计后续有专门的PCB和接地设计章节会进行详细描述,因为关于分地设计,接地设计牵涉到很多前提条件。另外还与产品是否是浮地设计、安规绝缘耐压要求等相关。

下图给一个类似的设计示意图给参考:

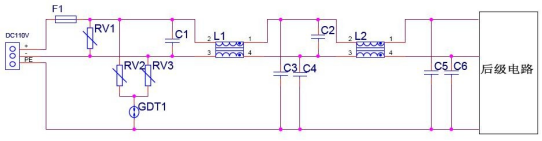

九、课程里讲各种滤波器件都要针对电路可能出现的干扰频率进行选择。那么请问老师对一款 DC DC,根据一般经验,它的干扰频率一般在那些频段?我们一般选择哪些频段对它进行滤波?答:首先根据产品测试标准要求的频段范围,DC/DC 正常测试 CE,测试频段范围为 150KHz-30MHz(汽车电子产品到 108MHz),滤波器和防护设计是一个器件组合实现的过程!

一般电源类产品详细滤波和防护设计在后续的滤波设计和防护设计专题中还会有详细的讲解,比如常规电源电路设计方案如下:

电路 EMC 设计说明:

- 电路滤波设计要点 L1、C1、C3、C4 组成第一级滤波电路。C1 为差模滤波电容,主要滤除差模干扰, 其滤波频段覆盖 150kHz-500kHz。C3、C4 为共模滤波电容,为共模干扰提供低阻抗回路,其滤波频段覆盖10MHz-30MHz。L1 为共模滤波电感,对共模干扰进行抑制,其滤波频段覆盖 10MHz-30MHz;L2、C2、C5、C6 组成第二级滤波电路。C2 为差模滤波电容,主要滤除差模干扰其滤波频段覆盖150kHz-500kHz。C5、C6 为共模滤波电容,为共模干扰提供低阻抗回路,其滤波频段覆盖 10MHz-30MHz。L2 为共模滤波电感,对共模干扰进行抑制,其滤波频段覆盖 10MHz-30MHz;L6、C10、C11 组成第二极滤波电路。C10、C11 为差模滤波电容, L6 为差模电感,主要滤除差模干扰;C9、C8 组成输出端滤波电路。C9 为 4.7uF的电解电容,主要针对低频噪声的滤波,其值可根据测试情况进行调整;C8 为 1000pF的小电容,主要针对高频噪声的滤波,其值可根据测试情况进行调整;保护地与输出端负极通过 1000pF 的电容 C16连接,主要为输出端干扰提供泄流路径;

- 电路防护设计要点 RV1、RV2、RV3、GDT1 组成第一级防护电路,其中RV1 进行差模防护、RV2、RV3、GDT1 进行共模防护。RV2、RV3、GDT1 防护器件会导致绝缘耐压试验不能通过,当接口需要考虑绝缘耐压试验时建议去掉 RV2、RV3、GDT1 三个元器件。

- 特殊要求 电路中所有的电容要符合安规的要求,差模电容选取耐压值AC275V,共模电容选取 Y电容;保险丝 F1 位置要靠近接口放置。因压敏电阻失效模式为短路,可能会造成大电流,因此需要增加保险丝。

- 器件选型要点 电路中Y 电容(C3、C4和 C5、C6)容值选取范围为 100pF~4700pF,典型值选取 2200pF;电路中 X 电容容值取值范围为 0.1μF ~10μF,C1 典型值为 0.22μF;C10 和 C11 典型值选取 0.68μF ;L1 为共模电感,感值取值范围为100μH~30mH,典型值选取 15mH;L6 为差模电感,感值取值范围为10μH~1mH,典型取值选取 47μH;RV1、RV2、RV3 压敏电阻选择压敏电压范围466V~616V,典型值选取550V,压敏电阻 RV1 的通流量(10 次冲击)选择大于等于 167A,压敏电阻RV2、RV3 的通流量(10次冲击) 选择大于等于 167A;GDT1 气体放电管选择直流击穿电压为466V~616V,典型值选取 550V,通流量选择大于等于 167A。以上元器件的取值后续可以根据实际的测试情况进行调整。

十、在案例讲解中,老师凭借工程实践经验直接锁定了干扰源头;那对于没有很丰富的工程实践经验的人来说,该怎么排查干扰源呢?一般排查感染源头有什么方法呢?(非经验方式的排查干扰源方法)答:建议1:借助频谱仪定位源头,另外有特征的超标频点;2:可以计算基频,从而对应单板上的时钟等周期信号;3:对于多系统组成,可以采取断电方式排除分析出干扰源;

感谢大家的查阅,想学习更多EMC工程知识,可参加赛盛技术精心打造的EMC线上实战特训营课程,课程从器件选型-防护设计-滤波设计-电源设计-PCB设计-接地设计详细讲解EMC设计规则与问题解决方法。

- 相关推荐

- 热点推荐

- emc

-

常见以太网馈问题解答2008-10-24 472

-

VxWorks常见问题解答2009-03-28 619

-

CCS问题解答2009-08-03 1041

-

PC 音质常见问题解答2010-08-02 661

-

新手-iPhone/touch常见问题解答2010-02-02 613

-

晶闸管实用技术问题解答2017-09-12 1123

-

静电试验 FAQ 集,emc-ESD的常见问题解答2021-01-18 4207

-

AN-1291:数字电位计:常见问题解答2021-03-19 1242

-

CAN总线常见问题解答2021-12-27 2889

-

EMC工程问题解答(二)2022-08-26 2131

-

EMC工程问题解答(三)2022-09-01 2002

-

EMC工程问题解答(八)2023-08-05 1453

-

CLOCK常见问题解答2023-11-23 726

-

TFPxxx常见问题解答2024-09-29 491

-

Keystone NDK常见问题解答2024-10-11 567

全部0条评论

快来发表一下你的评论吧 !