晶振的输出波形:TTL、CMOS、LVPECL、LVDS和正弦波

描述

晶振(XO)输出波形(Output Type)是与封装尺寸一样重要的一个技术指标,这些输出波形可简单归为两种:正弦波、方波。

在示波器上观察振荡器波形,虽然很多时候看到的还是不太好的正弦波,那是由于示波器的带宽不够。例如:有源晶振20MHz,如果用40MHz或60MHz的示波器测量,显示的是正弦波,这是由于方波的傅里叶分解为基频和奇次谐波的叠加,带宽不够的话,就只剩下基频20MHz和60MHz的谐波,所以显示正弦波。要完美再现方波需要至少10倍的带宽,5倍的带宽只能算是勉强,需要至少100M的示波器。

相较而言,方波输出功率大,驱动能力强,但谐波分量多,正弦波输出功率不如方波,但其谐波分量小很多。同时,两种波形还有各种不同的表现形式,分别适合不同的应用。

1.方波输出模式

数字通信系统中,一般采用方波输出模式的晶体振荡器,以匹配系统中驱动的负载。这些方波的通用输出类型有TTL和CMOS,还有LVPECL和LVDS,主要指标有输出电平、占空比、上升/下降时间、驱动能力等。

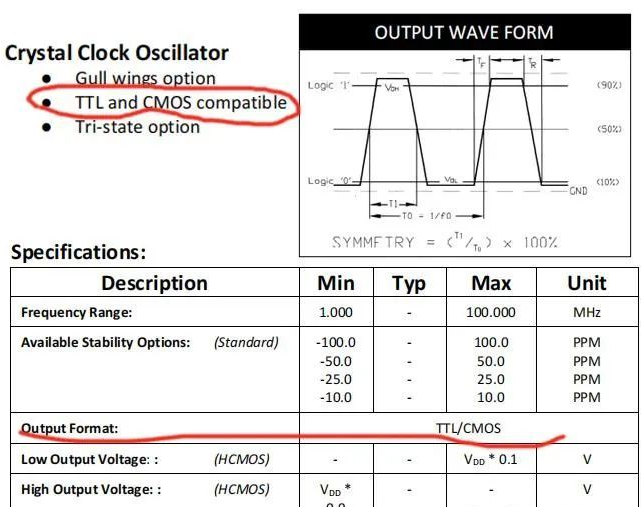

(1)TTL输出

TTL是晶体管-晶体管逻辑(Transistor-Transistor Logic)电路,传输延迟时间快、功耗高,属于电流控制器件。

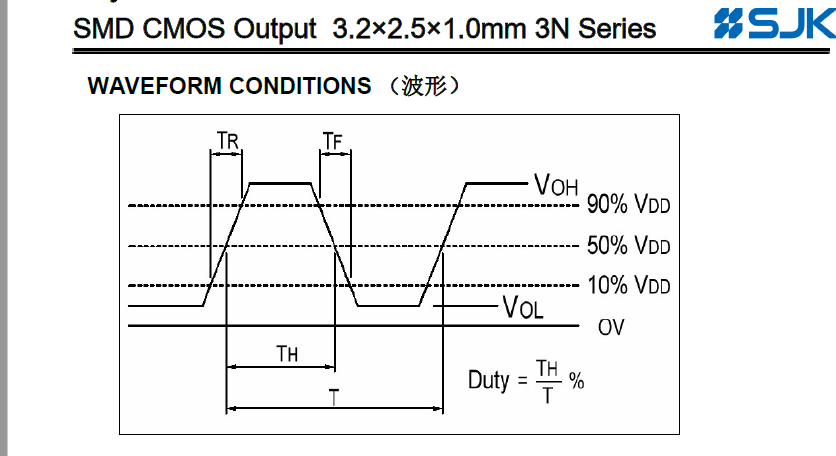

(2)CMOS输出

CMOS输出是最常见一种,属于属于电压控制形式,用来驱动逻辑电平输入。

晶振的CMOS输出波形

晶振的CMOS输出波形

CMOS输出的传输延迟时间慢、功耗低,相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。HCMOS采用全静态设计、高速互补金属氧化物半导体工艺,CMOS采用互补金属氧化物半导体。

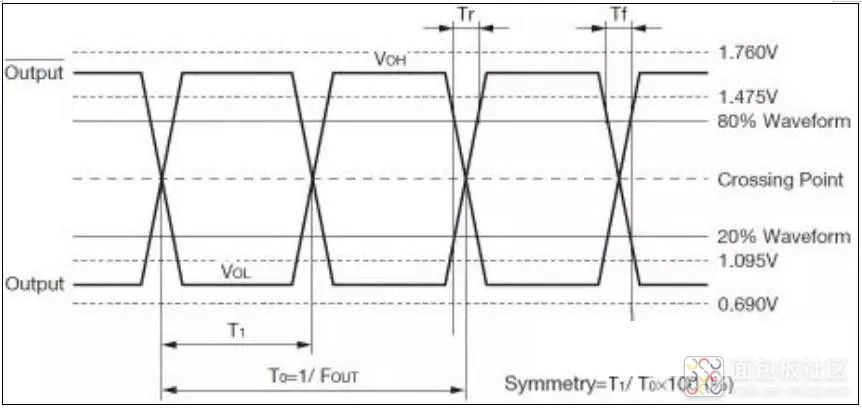

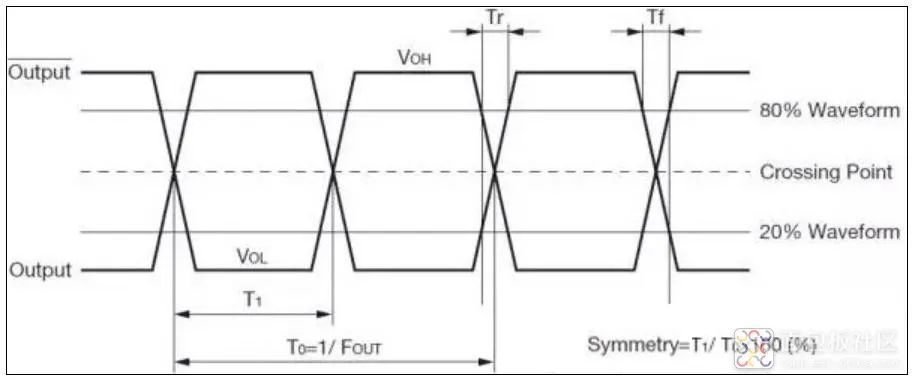

(3)LVPECL输出

LVPECL是低压正发射极耦合逻辑(Low-Voltage Positive Emitter-Couple Logic)。ECL电路速度快,驱动能力强,噪声小,很容易达到几百MHz的应用,但是功耗大,需要负电源。为简化电源,出现了PECL(ECL结构,改用正电压供电)和LVPECL的输出模式。

晶振的LVPECL输出波形

晶振的LVPECL输出波形

LVPECL由ECL和PECL发展而来,其典型输出为一对差分信号,射极通过一个交流源接地。ECL、PECL、LVPECL使用时应注意:不同电平不能直接驱动,中间可用交流耦合、电阻网络或专用芯片进行转换。

这三种结构必须有电阻拉到一个直流偏置电压。例如,用于时钟的LVPECL直流匹配时用130欧上拉,同时用82欧下拉;交流匹配时用82欧上拉,同时用130欧下拉,但两种方式工作后直流电平都在1.95V左右。

(4)LVDS输出

LVDS是低电压差分信号(Low-Voltage Differential Signaling),为差分对输入输出,内部有一个3.5-4mA恒流源,在差分线上改变方向和电平来表示“1”和“0”。

通过外部的100欧匹配电阻(并接在差分线上靠近接收端)转换为±350mV的差分电平。LVDS使用注意:可以达到600MHz以上,PCB要求较高,差分线要求严格等长,差最好不超过10mil(0.25mm);100欧电阻离接收端距离不能超过500mil,最好控制在300mil以内。

晶振的LVDS输出波形

晶振的LVDS输出波形

LVDS的应用模式可以有三种形式:

(1)单向点对点和双向点对点,能通过一对双绞线实现双向的半双工通信。

(2)多分支形式,即一个驱动器连接多个接收器(当有相同的数据要传给多个负载时,可以采用这种应用形式)。

(3)多点结构,此时多点总线支持多个驱动器,也可以采用BLVDS驱动器,它可以提供双向的半双工通信,但是在任一时刻,只能有一个驱动器工作,因而发送的优先权和总线的仲裁协议都需要依据不同的应用场合,选用不同的软件协议和硬件方案。

2. 正弦波输出模式

正弦波(Sine Wave)主要用于对EMI、频率干扰有特殊要求的电路,例如驱动RF组件、混频器或其它具有50Ω输入阻抗的器件。这时,振荡器产生的输出功率通常在0dBm到+13dBm(1mW到20mW)之间,尽管如果需要可以输出更高功率。

还有一种特殊的削顶正弦波(Clipped Sine Wave),相比方波的谐波分量少很多,但驱动能力较弱,在负载10K//10PF时Vp-p为0.8Vmin。SMD 7050、SMD5032、SMD3225等封装的表贴温补晶振通常使用这种形式的输出波形。

正弦波输出模式通常有谐波、噪声和输出功率等指标要求。这种电路要求输出的高次谐波成分很小,后面有模拟电路选用正弦波也是比较好的选择。

在厂商提供的晶振规格书里,除了输出模式或输出格式这个指标外,通常还附带相应的波形样式、输出负载和测试电路,有的晶振还兼容TTL、CMOS两者格式,应用灵活多样。

-

有源晶振的波形2024-11-23 2228

-

正弦波和方波晶振能否互相替代?2024-01-31 2652

-

晶振选择哪种输出波形比较适合?2024-01-24 3632

-

差分晶振的输出波形解析:三种类型要知道2023-11-09 1577

-

有源晶振的电气参数:波形上升下降时间2023-08-25 3031

-

有源晶振的波形释义?有源晶振的波形?如何测量有源晶振的波形呢?2023-08-18 4070

-

有源晶振的波形是正弦波吗?怎么测量?2023-04-17 4175

-

温补振荡器(TCXO)及其产生的削波正弦波2022-11-02 3324

-

差分晶振有LVCMOS输出模式吗2022-07-07 3241

-

方波晶振为什么测出形似正弦波2022-05-17 3452

-

晶振输出波形之正弦波和方波2022-05-16 17815

-

晶振输出用于驱动的几种电路形式2018-06-13 15056

-

【转帖】如何用示波器测试有源晶振波形2018-05-25 3848

-

300MHz晶振怎么搭建正弦波输出电路?晶振是6管脚的2017-08-07 4089

全部0条评论

快来发表一下你的评论吧 !