东芝开发出面向基带处理用途的动态可重构技术

电子技术

描述

动态可重构技术自亮相之初起,不仅在图像处理用途上,而且在软件无线电(Software Defined Radio:SDR)领域的应用上也一直备受期待。在基带处理中使用该技术,可在不同的无线通信方式间进行切换,或者同时运行多种方式。

东芝开发的就是面向基带处理用途的动态可重构技术。2008年9月东芝从比利时IMEC获得了动态可重构技术“ADRES(Architecture Fordynamically Reconfigurable Embedded Systems)”的研发授权,之后与IMEC共同就SDR用途进行了改进。

以往上述用途大多采用DSP,但是随着LTE、移动WiMAX、无线LAN(IEEE802.11n)等各种无线通信的处理内容日趋复杂,运算量增加,与DSP相比,动态可重构技术在电路面积及耗电量方面的优势逐渐凸显出来。就像LTE一样,现在的无线通信方式已变得非常复杂,往往是多种模式被归并到单一规格内。因此,“即使是导入单一方式,采用硬连线的话电路面积也容易增大。而以动态可重构技术来切换模式及方式的话,在面积效率上会变得更为有利”(东芝半导体公司半导体研究开发中心尖端无线模拟技术开发部部长亩川康夫)。另外,利用多个天线传输路径来提高传输速度的MIMO技术也被导入各种规格,运算量由此增大,使用DSP的话往往性能不足。

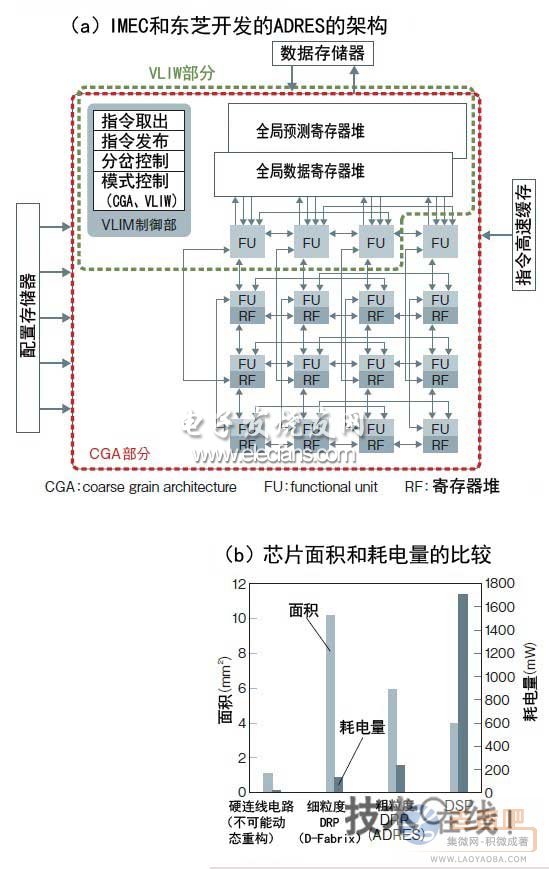

ADRES采用将运算器阵列部分“CGA(Coarse Grain Architecture)”与VLIW处理器密切结合的构成(图A-1)。普通的控制处理由VLIW部来实施,而并行性高的处理则由运算器阵列部来实施。其概念与东京计器的DAPDNA相似,DAPDNA是由运算器演阵列“DNA”与控制用CPU内核“DAP”构成的。

图A-1:在基带处理电路中应用IMEC的ADRES

东芝在无线通信的基带处理电路中应用IMEC的“ADRES”(a)。与DSP以及细粒度的动态可重构技术相比,在芯片面积及耗电量方面取得了平衡(b)。(b)为IEEE802.11a发送处理时的数值。(图片源自东芝)

运算器阵列部分的运算器数量是根据处理负荷在设计LSI时决定的,而现在为4×4(16个)。各运算器的bit宽度为64bit,寄存器为4个。分割使用寄存器,支持16bit×4路的SIMD型运算。“在无线通信领域,A-D转换器的bit宽度大多为10bit左右。有16bit的话足可供大量运算来使用(东芝的亩川)。另外,VLIW部分为3路,与运算器阵列相互独占运行。

在ADRES中,运算器阵列部的指令及布线数据保存于配置存储器。只要该存储器内有数据,便可以8个时钟动态切换电路构成。切换电路构成时,需要一次性完成向VLIW模式的状态转换,该转换要使用4个时钟。如果在VLIW模式下不执行任何处理的话,则变为合计8个时钟。

电路面积在使用90nm工艺的CMOS技术时约为6mm2。与IEEE802.11a(发送时)那样在硬连线电路中导入无MIMO的简单通信方式时相比,该面积约为其6倍,但在导入较复杂的无线方式时,这一面积差值可缩小至1~3倍以内(图A-1(b))。

-

基于xilinx ISE的动态可重构2014-03-10 2540

-

基于PAD的接收机动态可重构结构应用2019-07-10 1014

-

东芝新一代图像识别人工智能处理器ViscontiTM5的DNN硬件IP2019-07-25 3336

-

怎么设计PAD在接收机动态可重构结构中的应用?2019-08-13 1104

-

基于部分动态可重构技术的信号解调系统该怎么设计?2019-09-19 1843

-

可重构体系结构分为哪几种?动态可重构系统有哪些应用实例?2021-04-28 2017

-

怎么实现基于FPGA的动态可重构系统设计?2021-05-10 3033

-

动态可重构系统的通信结构分析2009-03-29 1419

-

PAD在接收机动态可重构结构中的应用设计2009-12-28 1064

-

东芝开发出无线LAN基带处理LSI2011-04-27 1138

-

一种面向流应用加速的可重构协处理器_曹姗2017-01-07 655

-

可重构技术分析及动态可重构系统设计2017-11-25 14683

-

英飞凌科联合Schweizer开发出面向轻度混合动力汽车新技术2019-05-14 1793

-

FPGA动态可重构技术是什么,局部动态可重构的时序问题解决方案2021-07-05 4606

-

关于FPGA可重构技术分析2022-11-03 1442

全部0条评论

快来发表一下你的评论吧 !