CW32L083系列MCU系统时钟详解

描述

时钟是单片机运行的基础,是同步单片机各个模块工作时序的最小时间单位。时钟的速度取决于外部晶振或内部RC振荡电路。单片机拥有丰富的外设,但实际使用的时候只会用到有限的外设,且有的外设需要高速时钟提升性能,有的外设需要低速时钟降低功耗或提高抗干扰能力,因此单片机采用多种时钟源来解决此问题。

下面将详细介绍如何配置CW32L083产品的系统时钟。

CW32L083一共有5个系统时钟来源LSI,LSE,HSI,HSE,PLL;可以按照时钟频率分为高速时钟源和低速时钟源,也可根据来源分为内部时钟源和外部时钟源。

• 外部高速时钟(HSE)

• 外部低速时钟(LSE)

• 内部高速时钟(HSI)

• 内部低速时钟(LSI)

• 锁相环时钟(PLL)

锁相环时钟由HSE时钟或HSI时钟经锁相环PLL倍频(2~12 倍)产生。

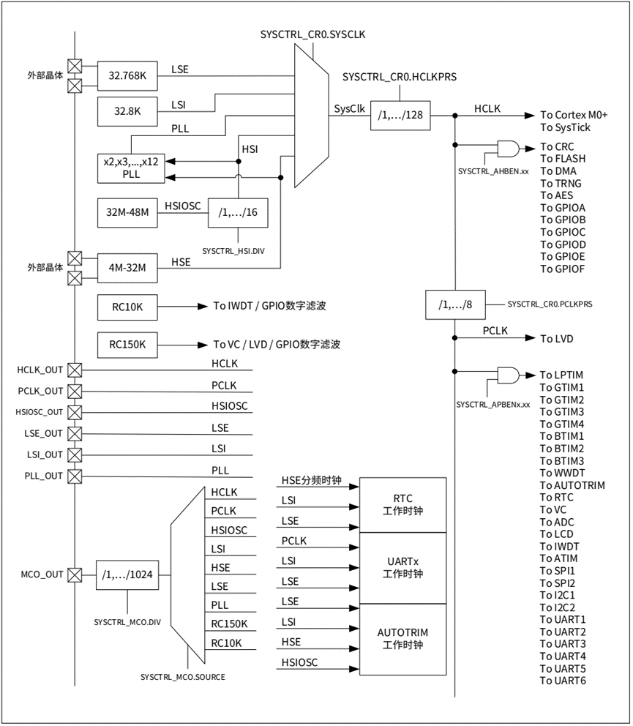

下图为CW32L083的系统内部时钟树,由图可以看到HSI时钟是由内部高速RC振荡器HSIOSC经过分频后产生的,分频系数是通过内置高频时钟控制寄存器SYSCTRL_HSI的DIV位域进行设置,有效分频系数为1,2,4,6,8,10,12,14,16。系统时钟SysClk可选的5个时钟源如上文所示。

图:CW32L083的系统内部时钟树

SysClk分频可以产生高级高性能总线时钟HCLK,作为M0+内核,SysTick,DMA,FLASH,CRC,GPIO等模块的配置时钟及工作时钟,分频系数是通过系统控制寄存器SYSCTRL_CR0的HCLKPRS位域设置,有效分频系数为2^n(n = 0~7)。而外设时钟PCLK,是由HCLK经过分频产生,通过配置系统控制器SYSCTRL_CR0的PCLKPRS位域设置,有效的分频系数为2^n(n= 0~3),可作为GTIM,BTIM,ATIM等定时器以及SPI,I2C,UART等外设的配置时钟和工作时钟。CW32L083还有两个低速时钟源,RC10K的时钟可作为独立看门狗的计数时钟以及GPIO端口中断输入信号的滤波时钟使用,RC150K时钟可以作为LVD和VC数字滤波模块的滤波时钟以及GPIO端口中断输入信号的滤波时钟使用。

CW32L083默认系统时钟为HSIOSC的6分频,即8MHz时钟,下面介绍时钟配置方法,CW32L083有丰富的时钟配置函数,内部FLASH存储器支持最快24MHz频率的操作时钟,当配置HCLK频率大于24MHz时,需要通过FLASH控制寄存器FLASH_CR2的WAIT位域来配置插入等待HCLK周期个数。大于24MHz,小于等于48MHz时,需要插入2个等待周期;大于48MHz时,需要插入3个等待周期。

1.HSI的时钟配置

在HSI小于等于24MHz的时候,可以不用配置FLASH等待周期

RCC_HSI_Enable( RCC_HSIOSC_DIV2 );

//内部高速时钟2分频SysClk=24MHz

RCC_HSI_Enable( RCC_HSIOSC_DIV6 );

//内部高速时钟6分频SysClk=8MHz,当HSI配置大于24MHz的时候,需要配置FLASH等待周期

__RCC_FLASH_CLK_ENABLE();

//使能FLASH配置时钟

FLASH_SetLatency(FLASH_Latency_2);

//频率大于24MHz,小于48MHz需要配置FlashWait=2

RCC_HSI_Enable(RCC_HSIOSC_DIV1);

//内部高速时钟1分频SysClk=48MHz

2.HSE的时钟配置

RCC_HSE_Enable(RCC_HSE_MODE_OSC,16000000,RCC_HSE_DRIVER_NORMAL,RCC_HSE_FLT_CLOSE);

//开启HSE时钟,HSE的频率范围为4MHz-32MHz

RCC_SysClk_Switch( RCC_SYSCLKSRC_HSE );

//切换系统时钟为外部高速时钟

3.LSI的时钟配置

RCC_LSI_Enable();

//开启内部低速时钟LSI

RCC_SysClk_Switch( RCC_SYSCLKSRC_LSI );

//切换系统时钟到LSI

4.LSE的时钟配置

RCC_LSE_Enable(RCC_LSE_MODE_OSC,RCC_LSE_AMP_LARGER,RCC_LSE_DRIVER_LARGER);

//开启外部低速时钟LSE

RCC_SysClk_Switch( RCC_SYSCLKSRC_LSE );

//切换系统时钟到LSE

5.PLL的时钟配置

CW32L083的PLL输入可以是HSI和HSE,下面以HSE为例

RCC_HSE_Enable( RCC_HSE_MODE_OSC, 16000000, RCC_HSE_DRIVER_NORMAL, RCC_HSE_FLT_CLOSE );

//开启外部高速时钟HSE,频率需要根据实际晶体频率进行填写

RCC_AHBPeriphClk_Enable(RCC_AHB_PERIPH_FLASH,ENABLE); RCC_PLL_Enable(RCC_PLLSOURCE_HSEOSC,16000000,RCC_PLL_MUL_2);

//开启PLL,PLL输入为HSE

FLASH_SetLatency(FLASH_Latency_2);

//频率大于24MHz,小于等于48MHz需要配置FlashWait=2

RCC_SysClk_Switch( RCC_SYSCLKSRC_PLL );

//切换系统时钟到PLL

上面所描述的是用库函数来配置CW32L083的系统时钟,接下来举例用寄存器来配置64MHz的系统时钟,思路是先将HSIOSC六分频得到8MHz的HSI,然后通过PLL倍频至64MHz。

//开启HSI时钟

CW_SYSCTRL->HSI=(5HSI&SYSCTRL_HSI_STABLE_Msk)!=SYSCTRL_HSI_STABLE_Msk)

//Wait stable

{

;

}

//设置PLL参数

CW_SYSCTRL->PLL = (RCC_PLL_WAITCYCLE_16384 | \

((uint32_t)(0x07 << SYSCTRL_PLL_FREQOUT_Pos)) | \

((uint32_t)(0x08 << SYSCTRL_PLL_MUL_Pos)) | \

((uint32_t)(0x01 << SYSCTRL_PLL_FREQIN_Pos)) | \

((uint32_t)(0x03 << SYSCTRL_PLL_SOURCE_Pos)));

// SYSCTRL_PLL_FREQOUT_Pos是PLL输出时钟频率范围配置因为是输出64MHz,需要设置为1xx

// SYSCTRL_PLL_MUL_Pos是PLL倍频系数配置位域,因为本例需倍频8倍,设置为0x08

// SYSCTRL_PLL_FREQIN_Pos是PLL输入时钟频率范围配置,本例HSI经分频之后为8MHz,设置为01

// SYSCTRL_PLL_SOURCE_Pos是PLL输入时钟来源选择,HSI时钟,设置为11

//使能PLL

CW_SYSCTRL->CR1 |= SYSCTRL_BYPASS | SYSCTRL_CR1_PLLEN_Msk;

//Enable PLL

//等待PLL时钟稳定

while((CW_SYSCTRL->PLL&SYSCTRL_PLL_STABLE_Msk)!=SYSCTRL_PLL_STABLE_Msk)

{

;

}

CW_SYSCTRL->AHBEN_f.FLASH = 1;

CW_FLASH->CR2 = 0x5A5A0000 | ((uint32_t)0x00000002);

//频率为64MHz,配置3个等待周期。

//转换时钟

CW_SYSCTRL->CR0 = ((((CW_SYSCTRL->CR0 & (~SYSCTRL_BYPASS_MASK)) | SYSCTRL_BYPASS) & (~SYSCTRL_CR0_SYSCLK_Msk)) | ((0x00000002U)));

RCC_SystemCoreClockUpdate(RCC_Sysctrl_GetHClkFreq());

配置完成之后,可以通过RCC_PLL_OUT(),看到输出频率。除了上述功能,CW32L083还可以通过配置GPIO口直接输出时钟端口,方便用户进行测试。

RCC_HCLK_OUT() //PA04输出HCLK时钟

RCC_PCLK_OUT() //PA03输出PCLK时钟

RCC_HSE_OUT() //PC15输出HSE时钟

RCC_HSI_OUT() //PB00输出HSI时钟

RCC_LSE_OUT() //PB12输出LSE时钟

RCC_LSI_OUT() //PD05输出LSI时钟

RCC_PLL_OUT() //PC13输出PLL时钟

以上是CW32L083时钟部分的介绍,CW32其他型号亦可参考此篇文档。

-

请问CW32L083如何实现AUTOTRIM时钟校准?2025-12-16 169

-

CW32L083系列微控制器的时钟配置有哪些选项?2025-12-15 129

-

CW32L083有哪些应用场景?2025-11-24 190

-

CW32L083如何实现AUTOTRIM时钟校准?2023-11-07 1541

-

移植RT-Thread nano到CW32L0832023-07-03 23850

-

基于CW32L083的线控器方案设计2023-06-25 487672

-

CW32L083 RTC初始化设置2023-06-24 3236

-

CW32L083实现SHT30驱动2023-06-22 5125

-

基于CW32L083的空调遥控器方案设计2023-06-21 2608

-

CW32L083系列MCU中断系统介绍2022-12-01 1173

-

CW32L083系列MCU系统时钟详解2022-10-25 1676

-

武汉芯源CW32L083系列MCU在空气净化器的应用介绍2022-10-13 1263

-

武汉芯源Cortex-M0+ 32位低功耗MCU CW32L083系列产品介绍2022-08-24 1844

全部0条评论

快来发表一下你的评论吧 !