学技术 | 基于 Semidrive X9H 主平台的 转接板 LVDS 计算阻抗匹配介绍

描述

1 前言

Semidrive X9H 主平台的转接板 PCB 布线时,涉及了 LVDS 高速差分线,不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗直接影响信号带宽、信号抖动和信号线上的干扰电压,如果不进行控制,信号质量会严重下降。所以在制版时需要计算差分信号的阻抗匹配,从而完成制版。

本文旨在通过SI9000 软件来计算转接板 LVDS 阻抗匹配做一个简单的介绍。

2 Polar Si9000 特性阻抗计算

2.1 Polar Si9000 软件安装

解压并运行exe启动安装进程。

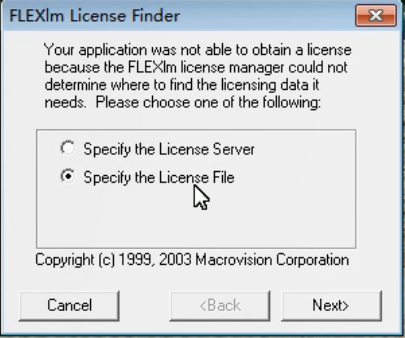

exe 完成后桌面会生成 Shortcut to Si9000 快捷键,双击快捷键会弹出如下窗口,选择第二个“Specify the License File”进入下一步。

图2-1 SI9000 指定 License 文件

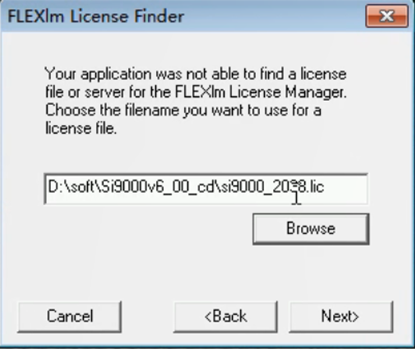

点击“Browse”选择安装文件里的“lic”文件,点击 NEXT 。

图2-2 SI9000 添加 “si9000_2038.lic”文件

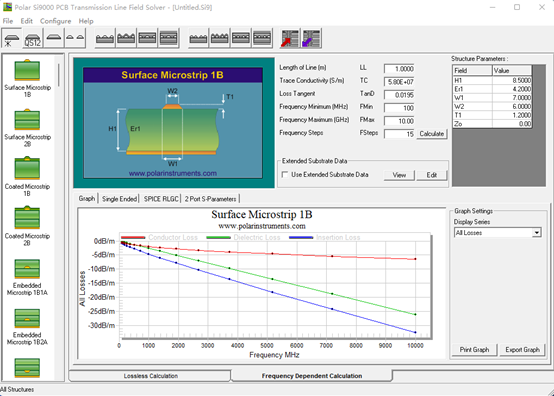

Polar SI9000 软件安装成功,启动并显示主界面

图2-3 SI9000 添加 “si9000_2038.lic”文件

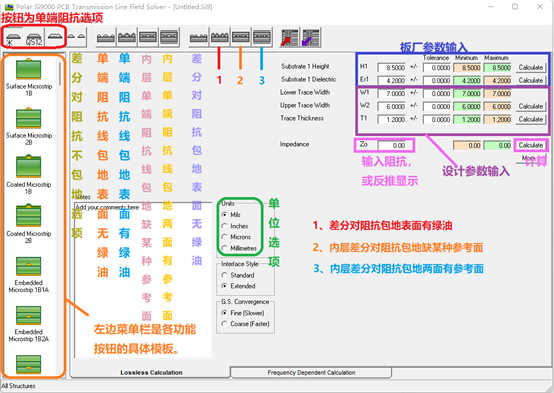

2.2 了解 Polar Si9000 软件界面

首先对 Si9000 界面有一个初步的了解,熟悉常用的几个模板的使用,学会了模板,也就基本了解了阻抗匹配。

图2-4 Si9000 软件主界面介绍

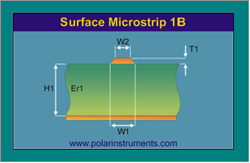

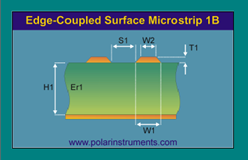

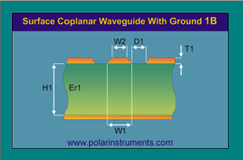

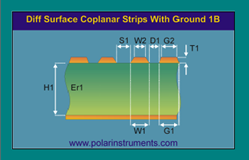

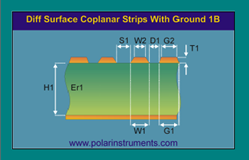

Si9000 软件设计参数:

H1 ---- 外层到次外层之间的介质厚度。(PP 片或者板材,不包括铜厚)。

Er1 ---- 这里是PP的介电常数。(例如:板材4.5,P 片4.2)。

W1 ---- 阻抗线下线宽。成品线宽,也就是我们的画图设计走线宽度。

W2 ---- 阻抗线上线宽。走线顶端宽度,表示侧蚀的意思,外层成品1oz的铜厚一般按1mil的侧蚀量计算。

S1 ---- 阻抗线间距。

T1 ---- 阻抗线铜厚或成品铜厚=基板铜厚+电镀铜厚。

C1 ---- 基材阻焊厚度。走线间的基材上的阻焊厚度,注意走线间隙一般比较小,容易产生沟壑效果,这里的阻焊厚度稍微厚一点。

C2 ---- 线面阻焊厚度(后加工)。

C3 ---- 基板上面的绿油厚度

CEr1 ---- 阻焊介电常数。

Zo ---- 需要的阻抗值。

2.3 Polar Si9000 常见的阻抗模型

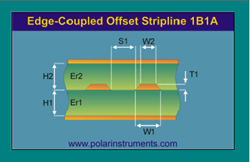

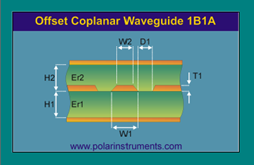

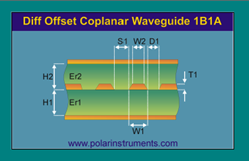

在中低端的线路板中涉及的一般少一些,主要是双面板、四层板、以及以上的层数的多层板。多层板的一般居多。阻抗一般分为6种:单端阻抗线、差分阻抗线、单端共面地阻线、差分共面地阻抗线、层间差分阻抗线、共模阻抗。

外层单端阻抗

外层差分阻抗

外层单端共面地阻抗

外层差分共面地阻抗

内层单端阻抗 <两面屏蔽>

内层单端阻抗 <两面屏蔽>

内层单端共面地阻抗 <两面屏蔽>

内层差分共面地阻抗 <两面屏蔽>

图 2-5 常见的阻抗模型

3 X9H 主平台计算 LVDS 阻抗匹配介绍

3.1 确定差分线的阻抗以及 PCB 板材参数

首先,查询到 LVDS 差分线的特征阻抗是100Ω。在设计PCB时,需要按特定的参数布线,使得阻抗匹配到 100Ω 左右,否则会有信号反射,造成信号质量下降。

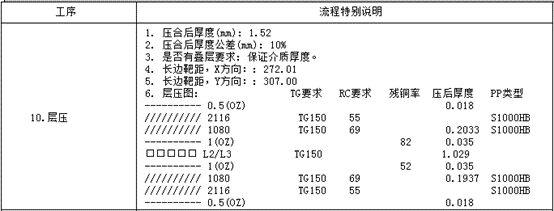

其次,X9H 主平台转接板 LVDS 制版说明中定义了:板材 FR-4,TG150;板厚 1.6mm;铜箔厚度:内层1 oz,外层0.5 + Plating oz;最小线宽8 mil;最小线距6 mil;最小孔径10 mil。

四层板1.6mm厚度的 PCB 层叠参数如下:

图3-1 四层板1.6mm厚度的 PCB 层叠参数

从上图中可以看出,我们转接板 LVDS 是四层板,2116+1080叠层结构,板材的介电常数为4.2,顶层/底层和相邻的中间层间距是0.1mm(约4mil),顶层铜厚度为0.035mm(约1.4mil),另外还有一些阻焊的参数,有了这些参数,就可以在 SI9000中计算布线的参数了。

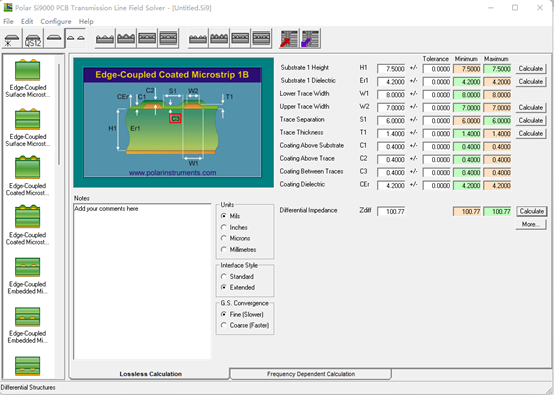

3.2 LVDS 差分阻抗匹配参数计算

LVDS 差分阻抗匹配打开 SI9000 后,选择差分对的微带线模型,这个模板含义是信号线与 GND 层相邻,并且信号上盖有绿油。

图3-2差分对的微带线模型选择

图3-3阻抗匹配计算步骤

在计算阻抗前,我们先要了解清楚几个参数,叠层参数,及板厂的板材,介电常数,绿油,PP 片厚度等参数。

首先常用的 PP 有:106=0.05MM=1.96mil,1080=0.07MM=2.75mil,2116=0.12MM=4.72mil,7628=0.19MM=7.4mil。根据板厂提供的板材确定介质厚度。

其次常用 FR4 芯板厚度有:2.4MIL,4mil,6mil,6.5mil,5.12mil,9.1mil,10mil,10.43mil,13miil,14.37mil等等厚度。不同的FR4芯板的介质也是不同的,常见的有4.2,4.4,4.5,这些差数只能通过板厂得知。

图3-4 转接板 LVDS 阻抗计算

3.3 特性阻抗的关键和方法:

在高速电路中,如 USB、HDMI、DDR、LVDS 设计中往往要注意阻抗匹配问题,高频信号在传输线中传播时所遇到的阻力称为特性阻抗,包括容抗,感抗,阻抗。为了保证信号在传输过程中不发生反射现象,信号尽量保持完整,降低传输损耗,要对印刷电路板进行阻抗匹配。阻抗匹配的目的主要在于传输线上所有高频微波信号都能达到负载点,不会有信号反射回源头。其中通常情况下,USB/DDR 的阻抗值保持在90Ω±10%。HDMI/LVDS 保持在100Ω±10%。

影响阻抗的关键因素主要有:线宽(W),线距(S),线厚(T),介质常数(Dk/Er),介质厚度(H),那么阻抗和线宽(W),线距(S),线厚(T),介质常数(Dk/Er)成反比,和介质厚度(H)成正比。

阻抗匹配的方法:1.凭经验值;2.交给PCB厂商;3.结合SI9000进行系统的理论计算。

-

阻抗匹配2007-12-10 1507

-

什么是阻抗匹配2006-09-25 4518

-

阻抗匹配总结2009-04-15 1344

-

阻抗匹配的详细介绍2009-10-20 1896

-

PCB阻抗匹配计算工具(附教程)2012-11-02 11089

-

Matching阻抗匹配计算软件(dos)2014-06-12 764

-

什么是阻抗匹配以及为什么要阻抗匹配2015-10-28 1141

-

PCB阻抗匹配计算工具与教程2017-01-04 1478

-

怎样理解阻抗匹配_pcb阻抗匹配如何计算2018-05-02 42736

-

阻抗匹配是什么意思_阻抗匹配原理详解2018-05-03 50748

-

阻抗匹配是什么阻抗匹配的介绍和计算的详细资料概述2020-01-17 2067

-

阻抗匹配的原理及应用2022-08-22 3539

-

找方案 | 基于 SemiDrive X9H 的 Core Board 之 e-Cockpit 方案2022-11-30 1343

-

请教关于LVDS阻抗匹配的问题 LVDS输出阻抗偏大会出现什么情况?2023-10-18 1752

-

使用LP875230C-Q1 和 LP87565V-Q1 的 Semidrive X9H 电源设计2024-09-12 134

全部0条评论

快来发表一下你的评论吧 !