RISC-V给我们带来了什么?

描述

来源:内容由半导体行业观察(ID:icbank)编译自semiwiki

通常,我们更喜欢把台式机/笔记本电脑的复杂指令集叫做CISC,把智能手机的精简指令集叫做RISC。戴尔和苹果等 OEM 一直在其笔记本电脑中使用 x86 CISC 处理器。让我在这里解释笔记本电脑的设计方法。主板以多核CISC处理器为主要部件,连接GPU、RAM、存储内存等子系统和I/O接口。操作系统在多核处理器上并行运行多个应用程序,管理内存分配和 I/O 操作。

这就是我们使用处理器实现任何电子系统的方式。然而,我们更喜欢使用 RISC 处理器的智能手机系统级芯片,因为它有助于我们减小主板的尺寸和功耗。几乎整个具有多核 RISC CPU、GPU、DSP、无线和接口子系统、SRAM、闪存和 IP 的系统都在 SoC 上实现。OEM Apple 正在遵循这款智能手机的 SoC 设计方法,甚至将他们的 MAC 笔记本作为 OEM 潮流引领者。所有最新的 MAC 书籍都使用他们的 M 系列 SoC,这些 SoC 使用 ARM 的 RISC 处理器。

因此,很明显,英特尔的 x86 或 ARM 的 RISC 处理器的专有 ISA 一直是 Apple、戴尔、三星等 OEM 的选择,但现在为什么我们需要像 RISC-V 这样的开放 ISA,而不是所有这些经过充分验证的ISA。

在今天的情况下,每个人都将 SoC 用于他们的笔记本电脑和智能手机。这种复杂的 SoC 需要通用处理器和专用处理器。为了实现像 Apple 的 M 系列 SoC 这样的芯片,我们需要不同种类的处理器,如 RISC CPU、GPU、DSP、安全处理器、图像处理器、机器学习加速器、安全和神经引擎,基于来自多个 IP 的各种通用和专用 ISA供应商。

在这种情况下,主要挑战是:

1.选择并与多家 IP 供应商合作

2.不同的 IP 供应商可能有不同的 IP 许可方案,工程师将无法自由地定制 ISA 和设计,因为他们更愿意满足他们的设计目标。

3.所有专门的 ISA 都不会持续/生存很长时间,从而影响长期产品支持计划和路线图。

4.此外,涉及多个 ISA 和工具链的软件/应用程序开发和更新将具有挑战性。

RISC-V 是一种具有多种扩展功能的通用免许可开放式 ISA。它是一个 ISA,分为一个小的基本整数 ISA,可用作定制加速器和可选标准扩展的基础,以支持通用软件开发。您可以添加自己的扩展来实现您的专用处理器,或者根据需要自定义基本 ISA,因为它是开放的。没有许可证限制。因此,在未来,我们可以仅使用一个 RISC-V ISA 创建所有通用和专用处理器,并实现任何复杂的 SoC。

什么是 RISC-V,它与其他 ISA 有何不同?

RISC-V 是加州大学伯克利分校的第五个主要 ISA 设计。它是由非营利组织 RISC-V International维护的开放式 ISA,涉及所有利益相关者社区以实施和维护 ISA 规范、黄金参考模型和合规性测试套件。

RISC-V 不是 CPU 实现。它是通用处理器和专用处理器的开放式 ISA。一个完全开放的 ISA,可供学术界和工业界免费使用。

RISC-V ISA 被分成一个小的基本整数 ISA,可单独用作定制加速器或教育目的的基础,以及支持通用软件开发的可选标准扩展

RISC-V 支持应用程序、操作系统内核和硬件实现的 32 位和 64 位地址空间变体。因此,它适用于所有计算系统,从嵌入式微控制器到云服务器,如下所述。简单的嵌入式微控制器、保护运行 RTOS 的嵌入式系统、运行操作系统的台式机/笔记本电脑/智能手机以及运行多个操作系统的云服务器。

二、RISC-V 基础 ISA

RISC-V 是一个相关 ISA 家族:RV32I、RV32E、RV64I、RV128I。

RV32I/ RV32E/ RV64I/RV128I 是什么意思:

RV——RISC-V

32/64/128 – 定义寄存器宽度 [XLEN] 和地址空间

I – 整数基 ISA

32 个用于所有基本 ISA 的寄存器

E – 嵌入式:只有 16 个寄存器的基本 ISA

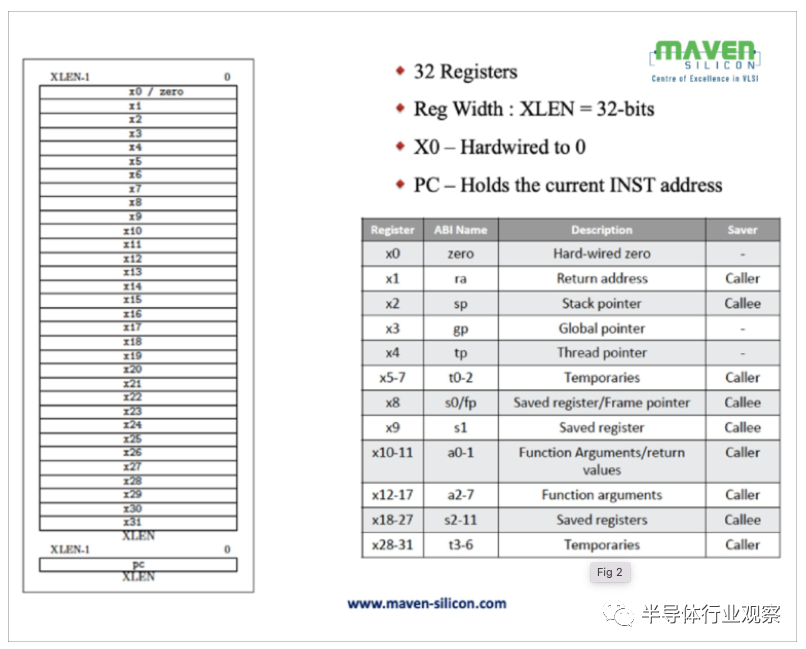

(1)RISC-V 寄存器:

所有基本 ISA 都有 32 个寄存器,如图 2 所示,除了 RV32E。只有RV32E base ISA对于简单的嵌入式微控制器只有16个寄存器,但寄存器宽度仍然是32位。寄存器 X0 硬接线为零。称为程序计数器的特殊寄存器保存要从内存中获取的当前指令的地址。如图 2 所示,RISC-V 应用程序二进制接口,ABI 定义了寄存器的标准功能。为了简单和一致,软件开发工具通常使用 ABI 名称。根据 ABI,额外的寄存器专用于 X0 到 X15 范围内的保存寄存器、函数参数和临时变量,主要用于 RV32E 基础 ISA,它只需要前 16 个寄存器来实现简单的嵌入式微控制器。但是 RV32I 基础 ISA 将拥有所有 32 个寄存器 X0 到 X31。

图 2:RISC-V 寄存器和 ABI 名称参考:RISC-V 规范

(2)RISC-V内存:

RISC-V hart [硬件线程/核心] 具有用于所有内存访问的 2^XLEN 字节的单字节可寻址地址空间。XLEN 表示整数寄存器的位宽度:32/64/128。内存字定义为 32 位(4 字节)。相应地,半字为16位(2字节),双字为64位(8字节),四字为128位(16字节)。内存地址空间是循环的,因此地址 2^XLEN -1 处的字节与地址零处的字节相邻。因此,由硬件完成的内存地址计算忽略溢出,而是环绕模 2^XLEN。RISC-V 基础 ISA 具有小端或大端存储系统,特权架构进一步定义了大端操作。指令作为 16 位小尾数法包的序列存储在内存中,而不管内存系统的字节顺序如何。

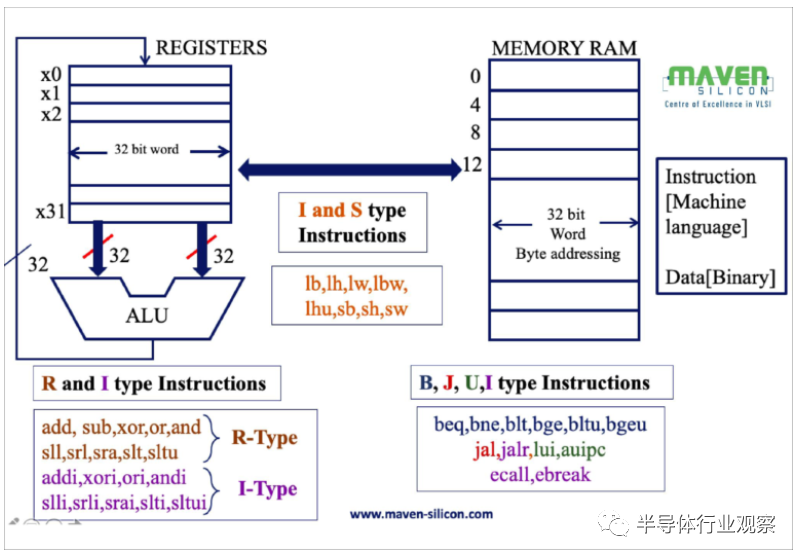

(3)RISC-V 加载存储架构

您可以可视化基于 RISC-V 寄存器和内存的 RISC-V 加载存储架构,如下图 3 所示。

RISC-V处理器根据PC中的地址从主存中取/载指令,译码32位指令,然后ALU进行算术/逻辑/内存读写操作。ALU 的结果将存储回其寄存器或内存中。

图 3:RISC-V 加载存储架构

(4)RISC-V RV32 I 基础 ISA

RV32I base ISA 只有 40 条 Unique Instructions,但简单的硬件实现只需要 38 条指令。RV32I指令可分为:

R-Type:注册到注册说明

I-Type:立即注册、加载、JLR、Ecall 和 Ebreak

S型:商店

B型:分支

J型:跳跃和链接

U 型:立即加载/添加上层

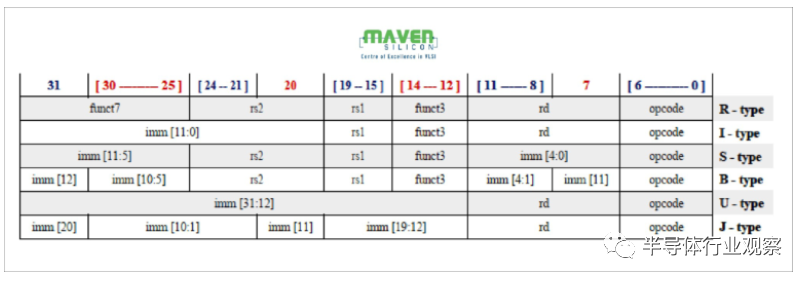

图 4:RV32I 基本 ISA 指令格式

(5)用于优化 RTL 设计的 RISC-V ISA

在这里,我想解释一下 RISC-V ISA 如何使我们能够实现优化的寄存器传输级设计,以满足低功耗和高性能的目标。如图 4 所示,RISC-V ISA 在所有格式中将源(rs1 和 rs2)和目标(rd)寄存器保持在相同位置以简化解码。

立即数总是经过符号扩展,并且通常被打包到指令中最左边的可用位,并且已被分配以降低硬件复杂性。尤其是,

所有立即数的符号位总是在指令的第 31 位以加速符号扩展电路。符号扩展是对立即数最关键的操作之一(特别是对于 XLEN>32),在 RISC-V 中,所有立即数的符号位始终保存在指令的第 31 位中,以允许符号扩展与指令解码并行进行。为了加快解码速度,基础 RISC-V ISA 将最重要的字段放在每条指令的同一位置。正如您在指令格式表中所见,

主要操作码总是在位 0-6 中。

目标寄存器(如果存在)始终位于位 7-11 中。

第一个源寄存器(如果存在)始终位于第 15-19 位。

第二个源寄存器(如果存在)始终位于第 20-24 位。

但是为什么立即位会被打乱呢?想想解码直接场的物理电路。由于它是硬件实现,因此这些位将被并行解码;输出立即数中的每一位都有一个多路复用器来选择它来自哪个输入位。多路复用器越大,成本越高,速度也越慢。

值得注意的是,只需要主要操作码(位 0-6)就可以知道如何解码立即数,因此立即数解码可以与指令其余部分的解码并行完成。

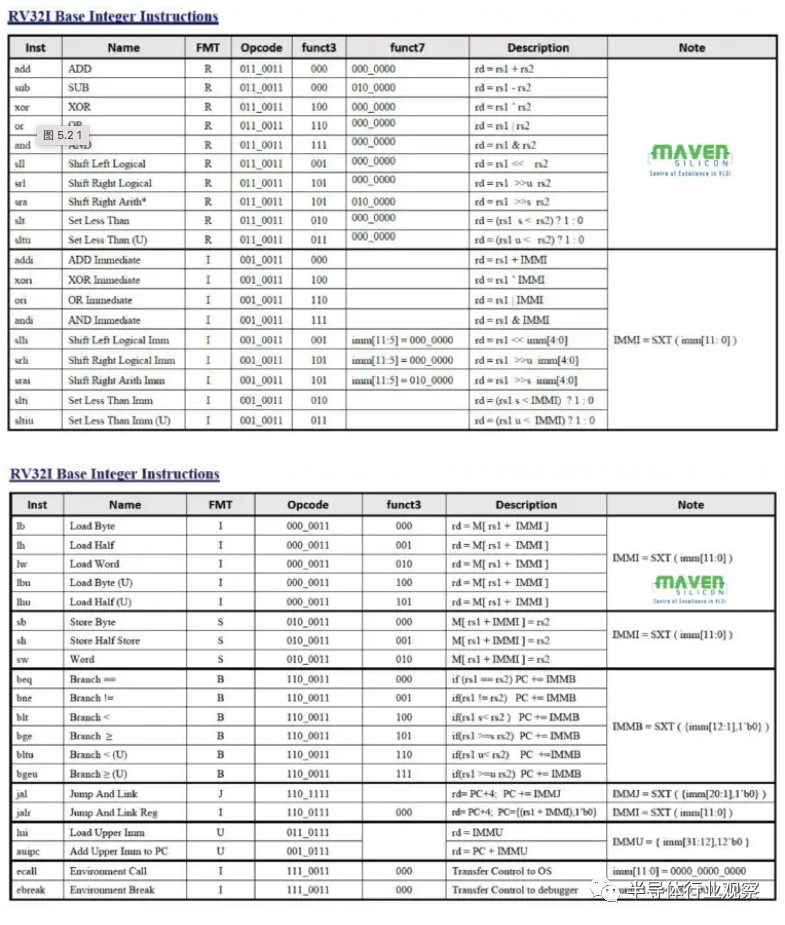

(6)RV32I 基本 ISA 指令

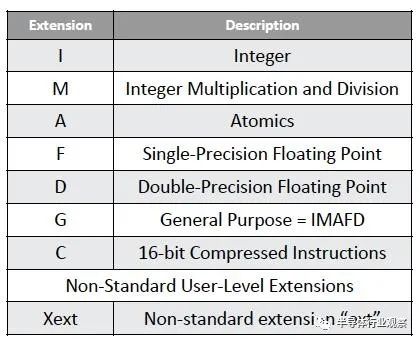

RISC-V ISA 扩展

此处列出了所有 RISC-V ISA 扩展:

图 5:RISC-V ISA 扩展

我们遵循 RISC-V 处理器的命名约定,如下所述:RISC-V 处理器:RV32I、RV32IMAC、RV64GCRV32I:整数基础 ISA 实现RV32IMAC:整数基础 ISA + 扩展:[乘法 + 原子 + 压缩]RV64GC:64 位 IMAFDC [G-通用:IMAFD]

整数 64 位基本 ISA + 扩展:[乘法 + 原子 + SP 浮动 + DP 浮动 + 压缩]

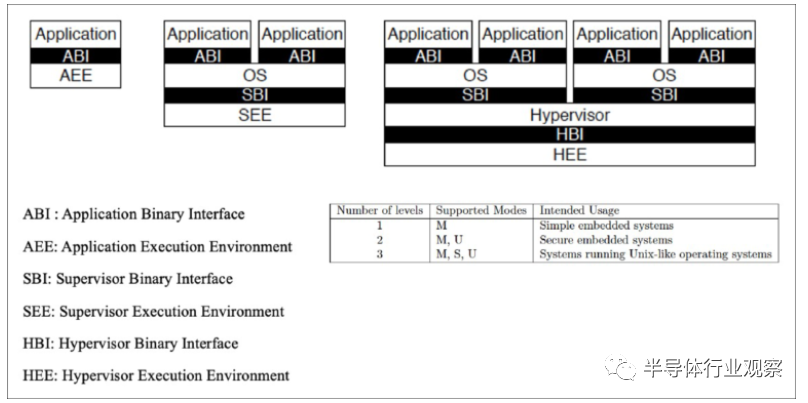

RISC-V 特权架构

RISC-V 特权架构涵盖了 RISCV 系统的所有方面,超出了我到目前为止所解释的非特权 ISA。特权架构包括特权指令以及运行操作系统和连接外部设备所需的附加功能。

根据 RISC-V 特权规范,我们可以实现从简单的嵌入式控制器到复杂的云服务器的不同类型的系统,如下所述。应用程序执行环境 – AEE:“裸机”硬件平台,其中 harts 直接由物理处理器线程实现,指令可以完全访问物理地址空间。硬件平台定义了一个从上电复位开始的执行环境。示例:简单且安全的嵌入式微控制器主管执行环境——参见:RISC-V 操作系统,通过将用户级 harts 多路复用到可用的物理处理器线程并通过虚拟内存控制对内存的访问来提供多个用户级执行环境。

示例:运行类 Unix 操作系统的桌面等系统

Hypervisor Execution Environment – HEE:RISC-V hypervisor,为来宾操作系统提供多个管理级执行环境。

示例:运行多个guest操作系统的云服务器

图 6:RISC-V 特权软件堆栈参考:RISC-V 规范

此外,RISC-V 特权规范定义了各种控制和状态寄存器 [CSR],以实现各种功能,如任何系统的中断、调试和内存管理设施。您可能需要参考规范以探索更多信息。

如本文所述,我们可以使用通用的开放式 RISC-V ISA 高效地实现任何系统,从简单的物联网设备到复杂的智能手机和云服务器。由于单片半导体缩放失败,专业化是提高计算性能的唯一途径。开放式 RISC-V ISA 是模块化的,支持自定义指令,使其成为创建各种专用处理器和加速器的理想选择。

随着 IEEE 标准通用验证方法论的出现,我们在芯片验证方面取得了巨大成功,开放的 RISC-V ISA 也将继承各种专有 ISA 的所有优点,成为行业标准 ISA,引领我们走向未来开放的计算时代。您准备好使用 RISC-V 专业知识迎接这个美好的未来了吗?

-

直播预约 | RISC-V大使谈RISC-V软硬件生态最新进展和未来趋势张国斌2024-11-12 1091

-

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !2024-09-10 1536

-

走进RISC-V:芯片界的新革命2024-07-12 1730

-

RISC-V芯粒,终于来了2023-09-15 1716

-

RISC-V设计支持工具,支持RISC-V技术的基础2023-07-14 831

-

RISC-V给我们带来了什么?2022-12-13 1097

-

什么是模型呢?模型给我们带来了什么?2021-07-02 2492

-

CAN究竟给我们带来了什么电子技术呢?2021-05-12 1522

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 4389

-

对于RISC-V,我们对它有些误解?2020-08-02 4319

-

为什么选择RISC-V?2020-07-27 5006

-

RISC-V给FPGA带来了什么机遇2020-06-09 4287

-

科技进步究竟给我们带来了什么?2019-07-23 13813

-

RISC阵营便动作频频,为加速RISC-V的生态发展和相关技术成熟2019-02-19 5271

全部0条评论

快来发表一下你的评论吧 !