AT32讲堂040 | AT32F435/437 EDMA基本功能讲解和案列解析

描述

EDMA简介

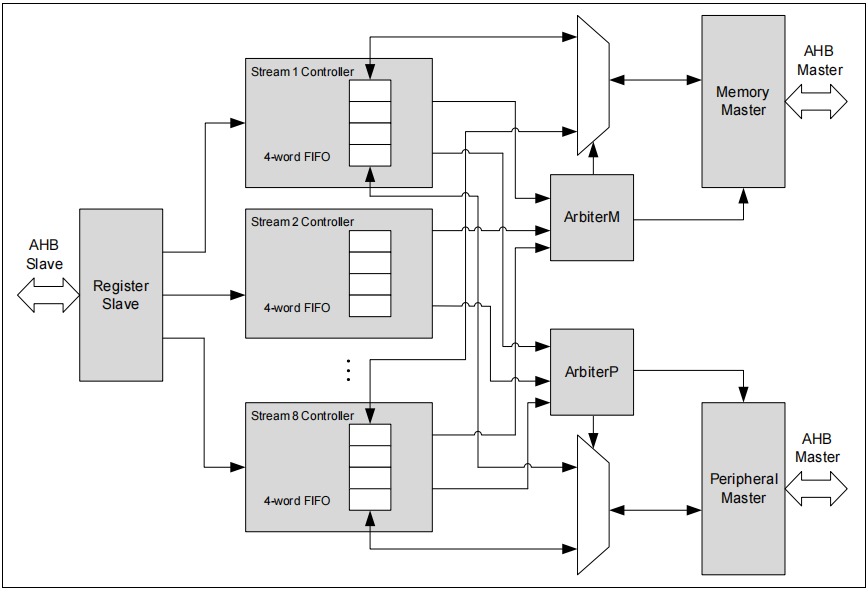

EDMA控制器的作用不仅在增强系统性能并减少处理器的中断生成,而且还针对32位MCU应用程序专门优化设计。EDMA控制器为存储器到存储器,存储器到外设和外设到存储器的传输提供了八个数据流通道。每个通道都支持外设的DMA请求映射到任意数据流上、数据的打包与拆包、FIFO开启与关闭、burst数据传输模式、存储器端的双buffer模式、可配置数据链传输、二维传输功能。基于复杂的总线矩阵架构,将功能强大的双AHB总线架构与独立的FIFO结合在一起,优化了系统的带宽。图1. EDMA控制器架构

DMAMUX简介

对于如何将外设的DMA请求映射到任意的数据流通道上,就需要使用到DMAMUX。DMAMUX针对每个外设都设计了独有的ID号,使用者只需要将此ID号写入对应的寄存器中并打开DMAMUX功能即可。DMAMUX的引入,使得EDMA相较于传统DMA控制器变得更加灵活,使用者可以随意的分配8个数据流通道的使用情况,不必再纠结与某个IP的DMA请求只能固定使用在某个或某几个通道上。

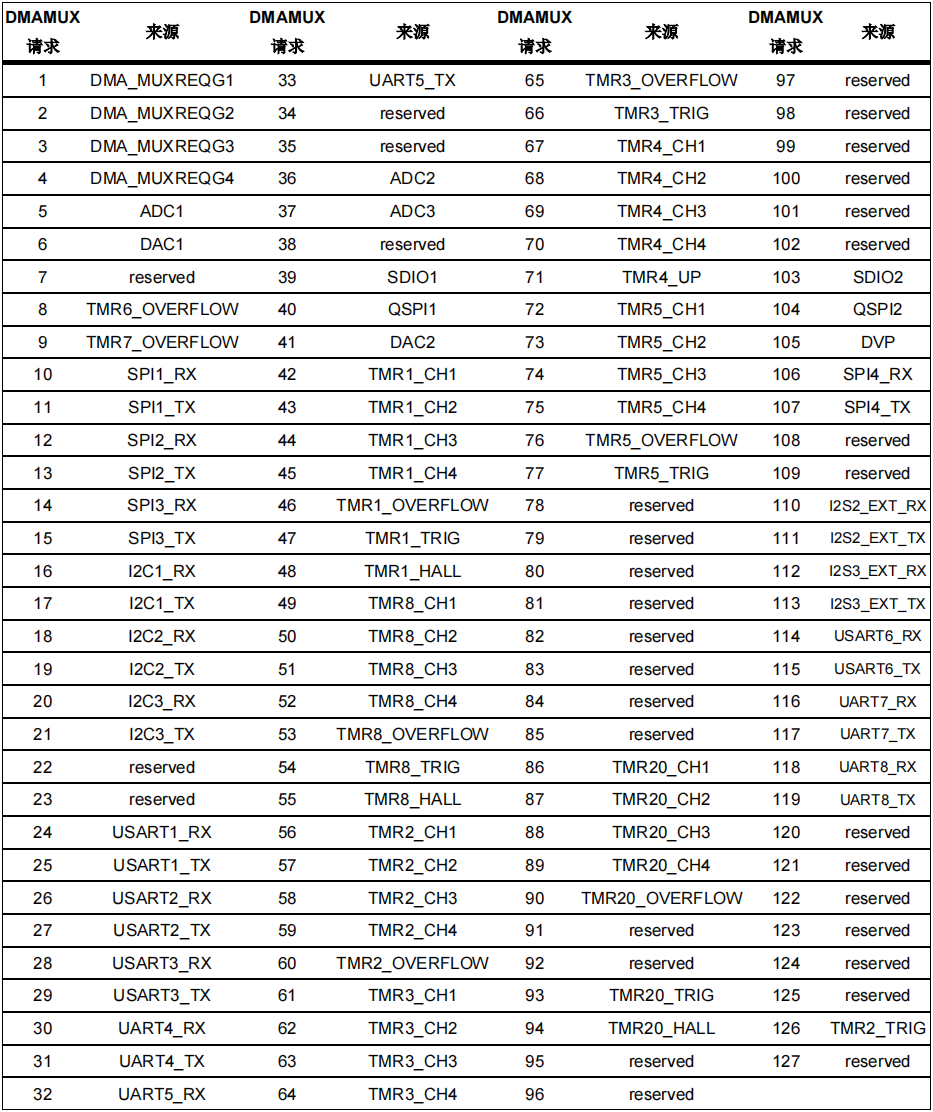

各IP对应ID号如下表:

表1. 各IP对应ID号列表 注:表格中“DMAMUX请求”为ID号;“来源”为各IP的DMA请求。

注:表格中“DMAMUX请求”为ID号;“来源”为各IP的DMA请求。

EDMA功能解析

基本配置

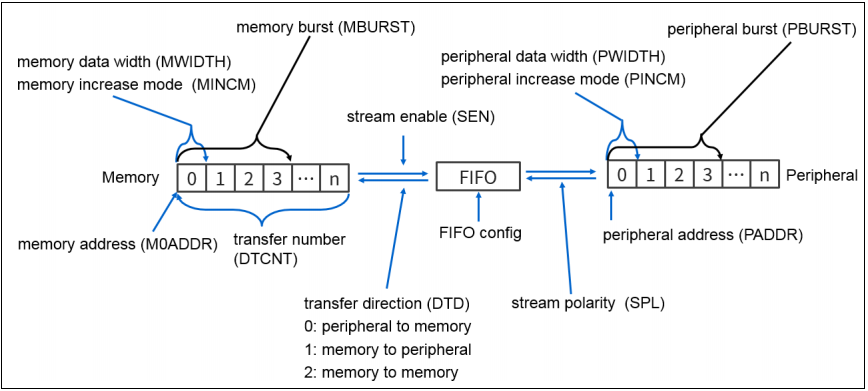

图2. EDMA基本参数配置 EDMA传输所需要的基本参数配置如上图所示,列举如下内存端口― 地址(M0ADDR)― 数据宽度(MWIDTH):8位、16位、32位― 地址地址模式(MINCM):固定、递增― 突发传输(MBURST):单次(1)、4、8、16节拍外设端口― 地址(PADDR)― 数据宽度(PWIDTH):8位、16位、32位― 地址地址模式(PINCM):固定、递增― 突发传输(PBURST):单次(1)、4、8、16节拍其他― 传输方向(DTD):外设到内存、内存到外设、内存到内存― 通道优先级(SPL):低、中、高、非常高― 数据传输个数(DTCNT):范围1~65535― FIFO配置― 流使能(SEN)

EDMA传输所需要的基本参数配置如上图所示,列举如下内存端口― 地址(M0ADDR)― 数据宽度(MWIDTH):8位、16位、32位― 地址地址模式(MINCM):固定、递增― 突发传输(MBURST):单次(1)、4、8、16节拍外设端口― 地址(PADDR)― 数据宽度(PWIDTH):8位、16位、32位― 地址地址模式(PINCM):固定、递增― 突发传输(PBURST):单次(1)、4、8、16节拍其他― 传输方向(DTD):外设到内存、内存到外设、内存到内存― 通道优先级(SPL):低、中、高、非常高― 数据传输个数(DTCNT):范围1~65535― FIFO配置― 流使能(SEN)

FIFO功能

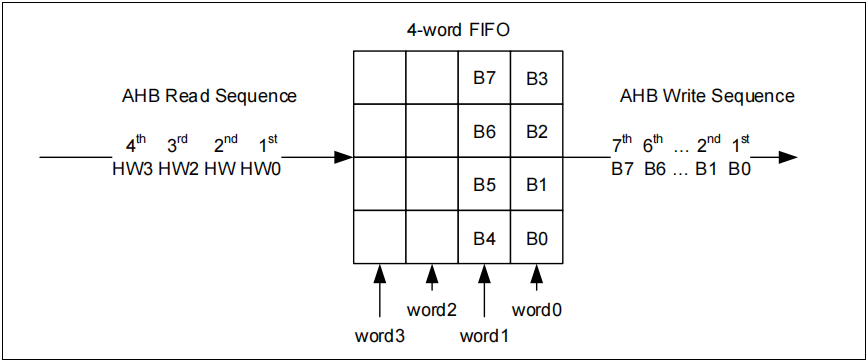

1、功能介绍EDMA控制器每个数据流都拥有独立的4 word fifo,这使得EDMA传输变得更加灵活,所传输的数据在FIFO内可进行打包与拆包操作,不再限制源与目标的数据总线宽度必须相等。在FIFO模式下,源和目标数据宽度可以通过SxCTRL寄存器PWIDTH与MWIDTH位配置(byte,halfword,word),且允许PWIDTH与MWIDTH不同。

当PWIDTH与MWIDTH不同时:

- EDMA要传输的数据宽度等于PWIDTH,例如PWIDTH=halfword,则需传输的数据量为SxDTCNT*2。

- EDMA控制器仅按照小字节序寻址源和目标。

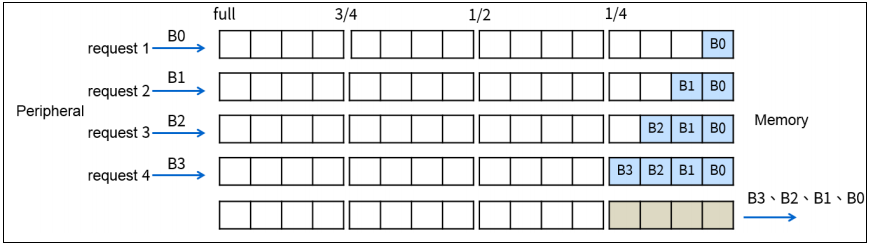

FIFO模式下外设到内存传输逻辑

图3. FIFO模式外设到内存传输 如上图所示,例如FIFO阈值设置成1/4,外设和内存端数据都为字节。刚开始FIFO状态为空,外设传输4笔数据后,FIFO状态为1/4,此时达到FIFO阈值,一次传输4个字节到内存。

如上图所示,例如FIFO阈值设置成1/4,外设和内存端数据都为字节。刚开始FIFO状态为空,外设传输4笔数据后,FIFO状态为1/4,此时达到FIFO阈值,一次传输4个字节到内存。

FIFO模式下内存到外设传输逻辑

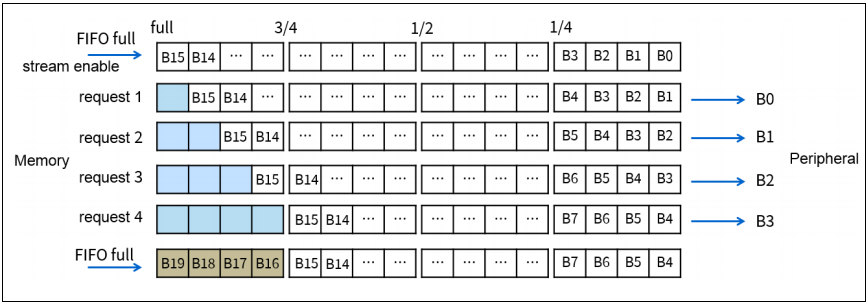

图4. FIFO模式内存到外设传输 如上图所示,例如FIFO阈值设置成1/4,外设和内存端数据都为字节。刚开始FIFO状态为空,当使能数据流后,立即从内存传输16个字节到FIFO,此时FIFO状态为满,然后外设传输4笔数据后,FIFO状态为3/4,此时达到FIFO阈值,一次从内存传输4个字节到FIFO,再次填满FIFO。

如上图所示,例如FIFO阈值设置成1/4,外设和内存端数据都为字节。刚开始FIFO状态为空,当使能数据流后,立即从内存传输16个字节到FIFO,此时FIFO状态为满,然后外设传输4笔数据后,FIFO状态为3/4,此时达到FIFO阈值,一次从内存传输4个字节到FIFO,再次填满FIFO。

FIFO模式下内存到内存传输逻辑

当使能数据流后,开始从源内存传输数据到FIFO,当达到FIFO阈值时,FIFO里的数据将被全部传输到目标内存,然后重复此步骤直到传输完成。在直接模式下(SxFCTRL内FEN=0),不可进行数据的打包与拆包。这种情况下,不允许源与目标的数据宽度不相等。数据宽度由PWIDTH定义,MWIDTH的设定无效。

直接模式下外设到内存传输逻辑

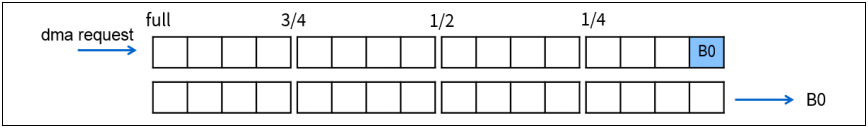

图5. 直接模式外设到内存传输 当产生DMA请求后,数据从外设传输到FIFO,然后FIFO内的数据将会立即传输到内存。

当产生DMA请求后,数据从外设传输到FIFO,然后FIFO内的数据将会立即传输到内存。

直接模式下内存到外设传输逻辑

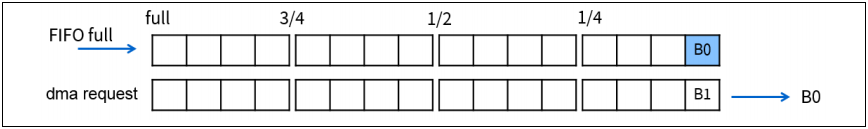

图6. 直接模式内存到外设传输 当使能数据流后,立即从内存传输一个数据到FIFO(数据大小由PWIDTH决定),当产生 DMA请求后,立即将数据从FIFO传输到外设,然后再次从内存传输一个数据到FIFO。

当使能数据流后,立即从内存传输一个数据到FIFO(数据大小由PWIDTH决定),当产生 DMA请求后,立即将数据从FIFO传输到外设,然后再次从内存传输一个数据到FIFO。

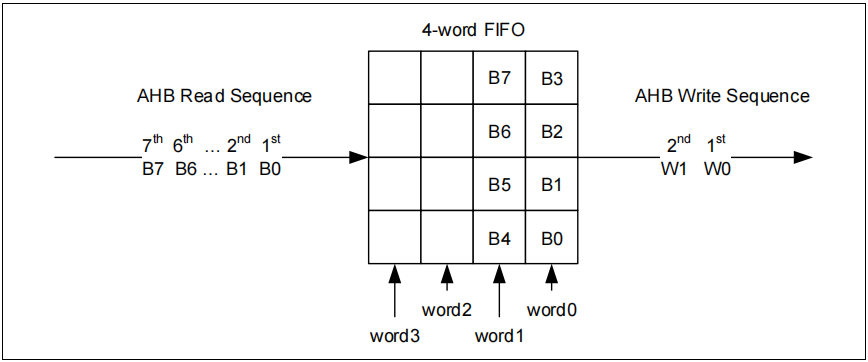

数据打包与拆包示意图如下:

图7. EDMA数据打包示意图 图8. EDMA数据拆包示意图

图8. EDMA数据拆包示意图

外设端口可以是源或者目标(在Memory to memory模式下,也可以是存储器源),在使用FIFO时,一定要合理配置PWIDTH、MWIDTH和SxDTCNT,已确保数据传输的完整性,在PWIDTH小于MWIDTH时,需要按照如下条件配置:

表2. PWIDTH和MWIDTH与SxDTCNT的限制条件

FIFO可配置阈值级别,软件可配置为1/4、1/2、3/4、满这四种状态(通过SxFCTRL寄存器FTHSEL配置),并且可通过SxFCTRL寄存器的FSTS位观察FIFO当前状态。

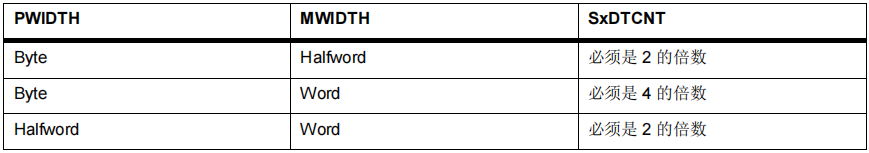

2、软件接口设置FIFO的软件接口包含在EDMA配置结构体内,以结构体成员的方式呈现,如下:

第一项为配置FIFO是否使能,当为TURE时,表示FIFO使能;当为FALSE时,表示FIFO禁止第二项为FIFO阈值设定,其选项可以是1/4、1/2、3/4和满这四种状态。

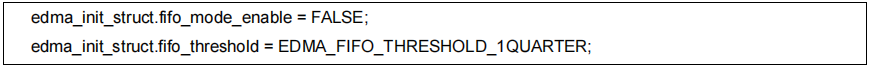

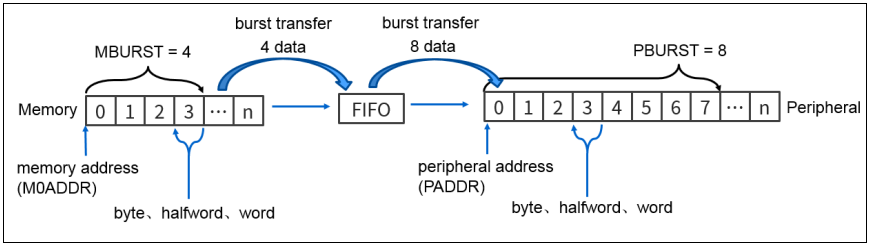

突发传输功能

功能介绍图9. 突发传输示意图 EDMA控制器可产生单次传输或4个、8个、16个节拍的突发传输。突发传输数量通过SxCTRL寄存器的PBURST与MBURST位设定。如上图所示,传输方向为内存到外设,内存端MBURST=4,每一次数据传输,DMA都会从内存连续传输4个数据到FIFO(数据可以为字节、半字、字)。外设端PBURST=8,每一次数据传输,DMA都会从FIFO连续传输8个数据到外设(数据可以为字节、半字、字)。突发传输数量是按照节拍数来计算的,并非按照字节数计数,例如PBURST=4,PWIDTH=halfword,则一次突发传输的数据量为4*2bytes。突发传输只能在FIFO模式下才可使用;在直接模式下,数据流只能生成单次传输,而MBURST和PBURST位由硬件强制配置。

EDMA控制器可产生单次传输或4个、8个、16个节拍的突发传输。突发传输数量通过SxCTRL寄存器的PBURST与MBURST位设定。如上图所示,传输方向为内存到外设,内存端MBURST=4,每一次数据传输,DMA都会从内存连续传输4个数据到FIFO(数据可以为字节、半字、字)。外设端PBURST=8,每一次数据传输,DMA都会从FIFO连续传输8个数据到外设(数据可以为字节、半字、字)。突发传输数量是按照节拍数来计算的,并非按照字节数计数,例如PBURST=4,PWIDTH=halfword,则一次突发传输的数据量为4*2bytes。突发传输只能在FIFO模式下才可使用;在直接模式下,数据流只能生成单次传输,而MBURST和PBURST位由硬件强制配置。

根据单次传输或突发传输的配置,每个DMA的请求在AHB外设端口上启动相应配置下的数据量传输:

- 当AHB外设端口配置为单次传输时,根据PWIDTH配置的值,每次DMA请求传输一个byte、halfword或者word。

- 当AHB外设端口配置为突发传输时,根据PWIDTH配置的值,每次DMA请求传输4个、8个、16个byte、halfword或者word。

注:源和目的地址自增模式下,才可使用突发传输。

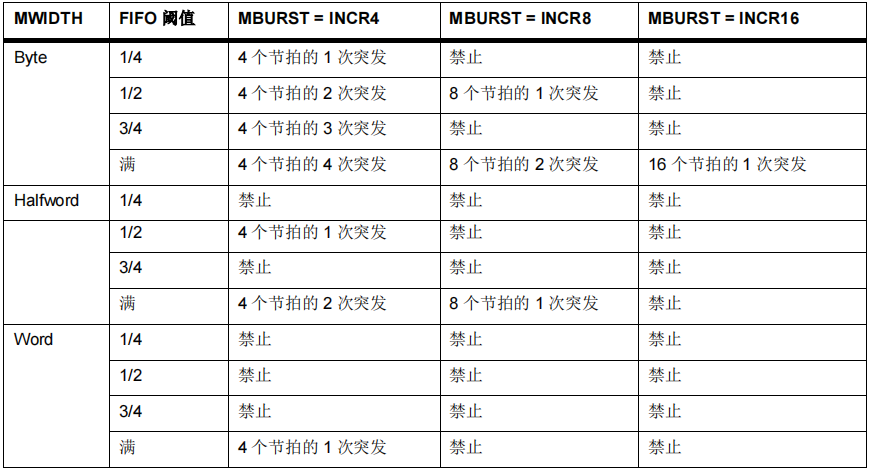

EDMA的FIFO阈值设定与存储器突发传输大小需要满足一定的关系才能正常启动数据流,否则在启动数据流时,就会产生FIFO error,然后将禁止数据流。FIFO阈值设定与存储器突发传输大小关系需满足如下:

表3. MWIDTH与MBURST配置关系

从此表个可以得出结论:突发传输数据量与数据大小乘积不能超过FIFO阈值大小。

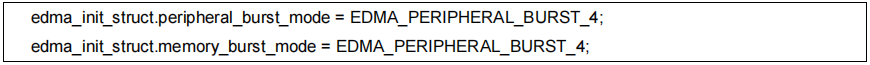

软件接口设置突发传输软件接口与设置FIFO类似,其被包含在EDMA配置结构体内,以结构体成员的方式呈现:

第一项为配置外设端口突发传输量;第二项为配置内存端口突发传输量。

注:在使用突发传输时,必须使能FIFO模式。

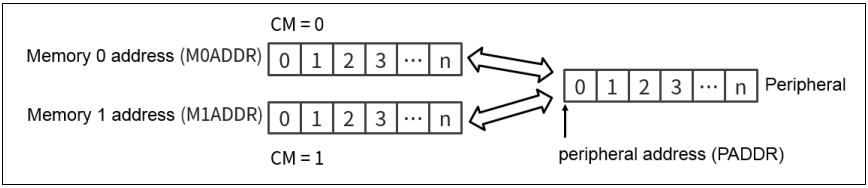

存储器端双缓存区功能

功能介绍图10. 双缓存区示意图 通过设置SxCTRL寄存器的DMM位,即可使能双缓存区功能。与常规(单缓存区)数据流工作模式相比,双缓存区功能拥有两个存储器指针;启动双缓存区功能时,EDMA控制器的相应数据流通道会自动开启循环模式,在每次SxDTCNT减到0时自动交换存储区。

通过设置SxCTRL寄存器的DMM位,即可使能双缓存区功能。与常规(单缓存区)数据流工作模式相比,双缓存区功能拥有两个存储器指针;启动双缓存区功能时,EDMA控制器的相应数据流通道会自动开启循环模式,在每次SxDTCNT减到0时自动交换存储区。

根据SxCTRL寄存器的CM位,可知道数据流当前使用的存储区是memory0/1。当CM=0,表示当前目标是memory0;当CM=1,表示当前目标为memory1。

在使用双缓存区,需要注意以下几点:

- 当硬件正在使用某一块缓存时,当前缓存的基地址不可改变,即寄存器SxM0ADDR和

SxM1ADDR。例如数据流正在将数据填入SxM0ADDR时,那么软件只能改变SxM1ADDR的基地址。可根据CM位的状态,确定数据流当前操作的缓存区。

- 当使用双缓存区功能时,禁止使用存储器到存储器模式。

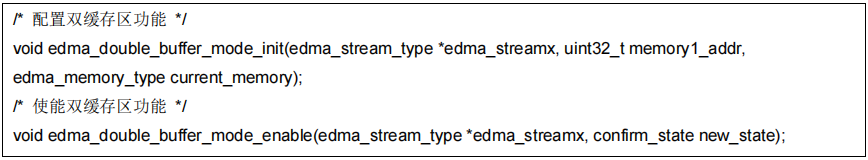

软件接口对于双缓存区功能,软件实现了单独的函数接口,如下:

对于双缓存区功能,第一个缓存区地址会在EDMA初始化结构体中配置,即SxM0ADDR寄存器的配置。

在配置双缓存区功能时,调用edma_double_buffer_mode_init();函数,此函数第一个参数表示当前配置双缓存区的数据流,第二个参数为第二个缓存区的地址,第三个参数为启动后硬件使用的缓存区。以上函数的调用,双缓存区功能就配置好了,现在只需要调用 edma_double_buffer_mode_enable(); 函数开启双缓存区功能即可。

链接列表传输功能

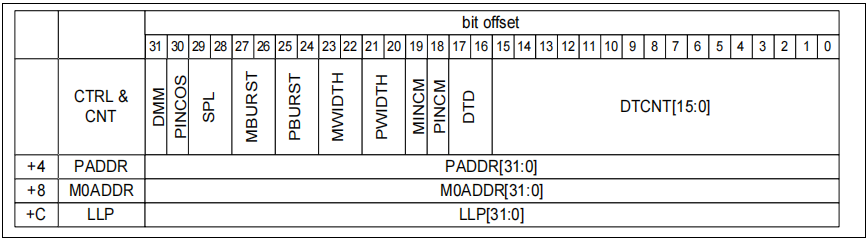

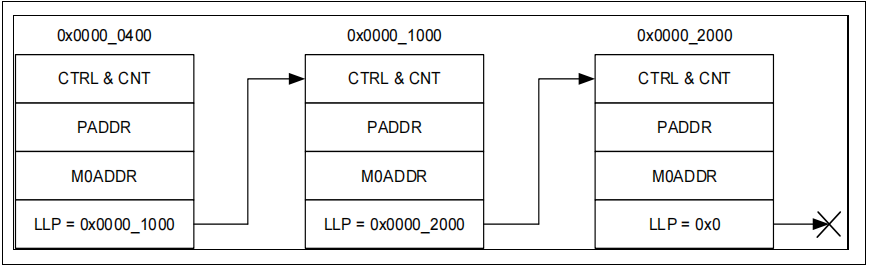

功能介绍链接列表传输可实现将几块不连续的存储区的数据使用同一个数据流按照一定顺序发送出去或者同一数据流接收到数据按照一定顺序存储在几块不连续的存储区内。EDMA控制器如何知道数据存储规则的呢?此规则是由软件按照特定格式给出的,其格式如下图所示:图11. 链接描述符格式

将此格式成为链接描述符,此描述符存储在片上存储器中,当打开数据流时,EDMA 控制器从片上存储器加载此描述符配置数据流,然后开启数据的传输。

描述符分为4项:

- 数据流基础配置和数据传输数量配置

- 外设基地址

- 存储器基地址

- 下一个描述符的首地址

通过描述符的具体实现,最终实现一个单向链表结构,如下:图12. 链接描述符链表结构

注:描述符在片上存储地址必须要4 word对齐,否则不能正常启动数据流。

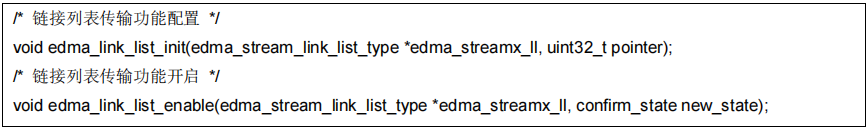

软件接口对于链接列表传输功能,软件单独实现了函数接口,如下:

第一个函数是对链接列表传输功能的一些配置。参数有两个,第一个参数表示所配置的数据流号,第二个参数表示链表描述符的首地址。

经过此函数的配置后,只需调用第二个函数即可开启链表传输功能。

二维处理功能

功能介绍二维数据传输(2D)功能,使用者可以较为方便的对数据块进行一些操作,提高对数据的处理效率,在图像处理方面效果较为明显。

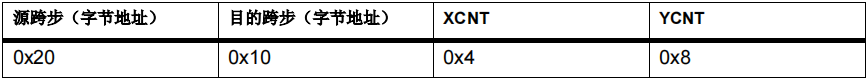

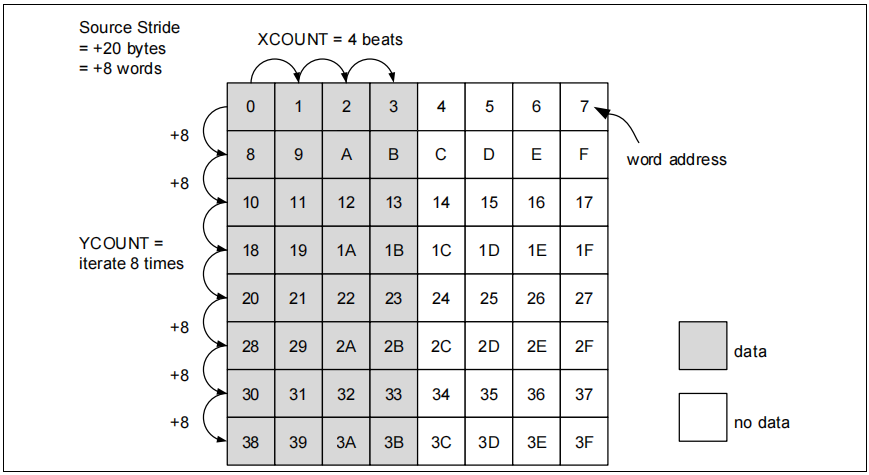

EDMA为二维数据传输(2D)提供了4个可配置的参数值:

- DMA_Sx2DCNT中的XCOUNT:跳转到下一个跨步之前要传输的数据计数;

- DMA_Sx2DCNT中的YCOUTNT:迭代计数;

- DMA_Sx2DSTRIDE中的SRCSTD:源跨步值,该值应在源端迭代之前添加或减去;

- DMA_Sx2DSTRIDE中的DSTSTD:目的跨步值,该值应在目标端迭代之前添加或减

去。

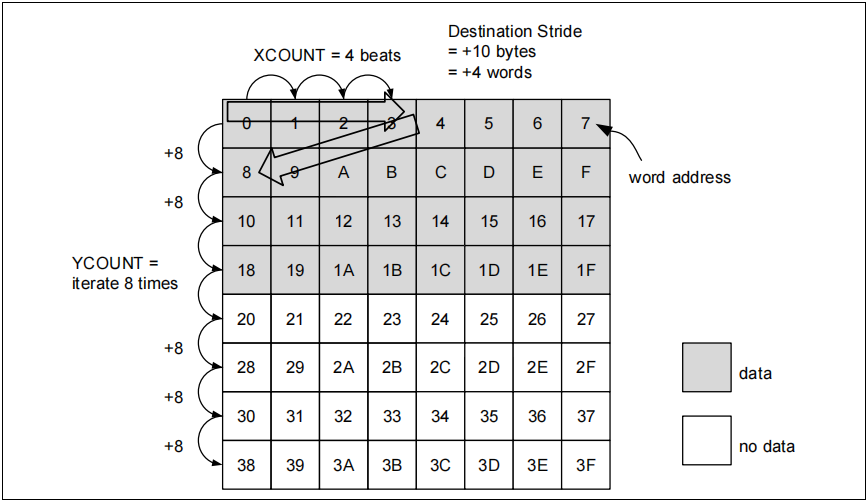

二维数据传输(2D)举例:

表4. 2D传输举例

传输前数据在源存储器中:

图13. 2D传输前数据

传输后数据在目的存储器中:

图14. 2D传输后数据

图4和图5的阴影部分为真实数据。根据图中可以清晰看到将数据看成二维的存储在存储器中,2D传输将此数据块的左边1/2的数据取走并存储在新二维数据块的上1/2处。

在使用二维传输时,有一些限制条件需要注意:

- 仅支持memory to memory传输

- PWIDTH和MISZE需要设置为0x2(字)

- 源和目标跨步值需与字对齐

- 源和目标跨步值均为二补数

- PINCM和MINCM均需设置为1(增量模式)

- PFCTRL需设置为0

- PINCOS需设置为0

- 不支持循环模式、双缓冲模式

- 不支持链接列表传输

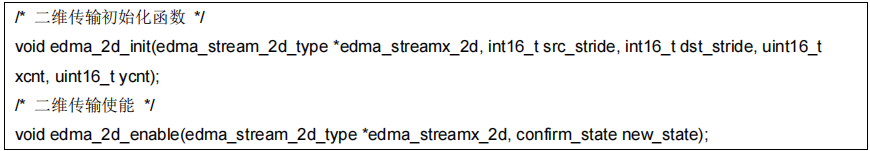

软件接口对于二维数据传输功能,软件单独实现了接口函数,如下:

通过函数edma_2d_init(); 可以配置二维传输的源跨步、目的跨步、XCNT和YCNT,这四个参数的在使能2D传输前就需要配置好;然后调用函数edma_2d_enable(); 即可开启二维传输功能。

EDMA配置解析

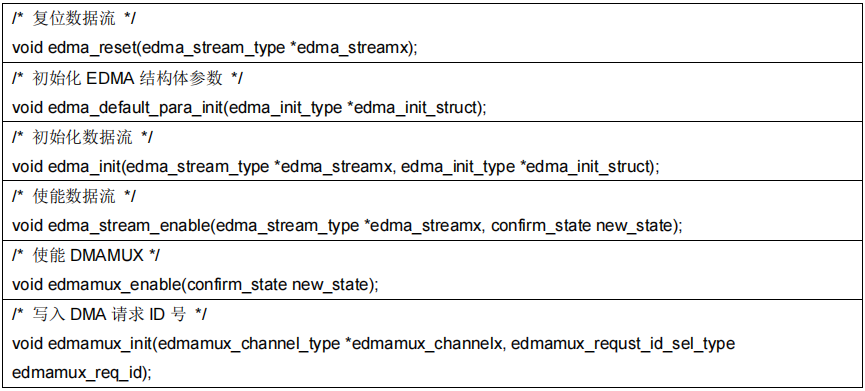

以下对EDMA的配置接口及流程进行说明。

函数接口

表5. 数据流配置函数列表

数据流配置

- 设置外设地址(SxPADDR寄存器)数据传输的初始外设地址,在传输过程中(SEN=1)不可被改变。

- 设置存储器地址(SxM0ADDR寄存器)数据传输的初始内存地址,在传输过程中(SEN=1)不可被改变。

- 数据流配置(SxCTRL寄存器)包含优先级,数据传输方向、模式和宽度,地址增量模式、循环模式、双缓冲模式和传输/半传输/传输错误中断使能位。优先级(SPL)分为4个等级,最高优先级、高优先级、中等优先级和低优先级。若有2个流优先级设定相同,则较低编号的流有较高的优先权。举例,流1优先于流2。数据传输方向(DTD)分为存储器到外设(M2P),外设到存储器(P2M)或存储器到存储器(M2M)传输。在存储器到存储器传输模式下不允许使用循环模式、双缓冲模式和直接模式。数据传输宽度(PWIDTH/MWIDTH)根据实际使用情景,可配置宽度为byte、halfword、word;EDMA内部的打包、拆包机制允许PWIDTH与MWIDTH宽度不一致。地址增量模式(PINCM/MINCM)当流配置设定为增量模式时,下一笔传输的地址将是前一笔传输地址加上传输宽度(PWIDTH/MWIDTH)。数据传输模式(PBURST/MBURST)分为单次传输(SINGLE),或突发传输(BURST)。突发传输,在每个DMA请求到来后,根据配置传输4、8、16拍。在非增量模式下,设置突发传输会将4、8、16拍突发传输转换为4、8或16个单次传输。在直接模式下,PBURST和MBURST位被硬件强制为0(单次传输)外设流控选择(PFCTRL)若选择外设做为流控制(PFCTRL=1),硬件会将DMA_SxDTCNT的值强制为0xFFFF,并由外设的dma_ch_lt信号指示数据传输结束。外设流控制不支持M2M模式和循环模式。循环模式(LM)当流配置设定为循环模式时,在最后一次传输后 SxDTCNT 寄存器的内容会恢复成初始值。双缓存模式(DMM)当流配置设定为双缓冲模式时,硬件会自动启用循环模式。双缓冲区流有两个存储器指针SxM0ADR/SxM1ADR,由CT位標示當前使用之存储器指针,允许软件在DMA填充/使用第二个存储区的同时处理另一个存储区。

- 直接模式与FIFO模式设定(SxFCTRL寄存器)包含FIFO阈值选择,直接模式禁用和FIFO错误中断使能位。FIFO阈值选择(FTHSEL)分为1/4、2/4、3/4和全FIFO阈值;该设定仅在非直接模式下有效。FIFO模式使能(FEN)直接模式(FEN=0)仅可在P2M或M2P模式下使用,且外设/存储器传输宽度需相等(MWIDTH=PWIDTH)并设定为单次传输(PBURST=MBURST=0)。如果选择M2M模式,该位(FEN)被硬件强制为1。

- 使能DMAMUX(MUXSEL寄存器的TBL_SEL位)在非存储器到存储器(M2M)模式下时,需要使能 DMAMUX 功能,才能启动数据流响应外设的DMA请求。

- 写入外设ID号(MUXSxCTRL寄存器的REQSEL)在非存储器到存储器(M2M)模式下时,需要将外设的DMA请求ID号写入,才能启动数据流响应外设的DMA请求。

- 打开数据流(SxCTRL寄存器的SEN位)

配置流程

- 打开EDMA时钟;

- 调用数据流复位函数复位数据流;

- 调用结构体初始化函数初始化数据流结构体;

- 调用初始化函数初始化数据流;

- 调用DMAMUX使能函数以及ID号写入函数配置DMAMUX相关内容;

- 调用数据流使能函数开启数据流。

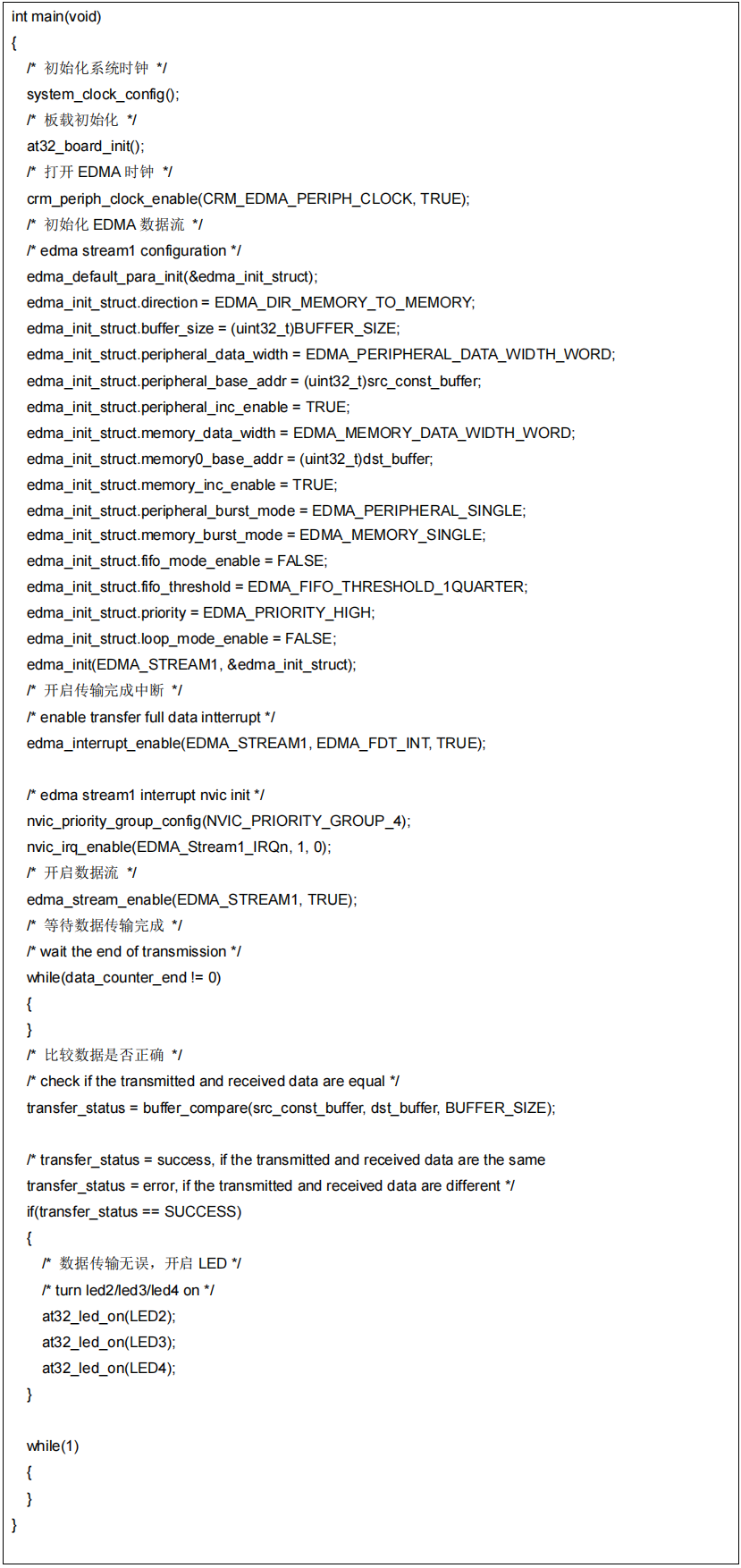

案例 数据从FLASH传输到SRAM

功能简介

实现了使用EDMA将数据从片上FLASH搬运到内部SRAM中。

资源准备

1) 硬件环境:对应产品型号的AT-START BOARD2) 软件环境project\at_start_f4xx\examples\edma\flash_to_sram

软件设计

1) 配置流程

- 开启EDMA外设时钟

- 配置EDMA数据流

- 开启传输完成中断

- 开启数据流

- 等待数据传输完成

- 比较数据传输是否正确

2) 代码介绍

- main函数代码描述

- EDMA_Stream1_IRQHandler中断函数代码描述

实验效果

- 如若数据传输无误,LED2/3/4会点亮。

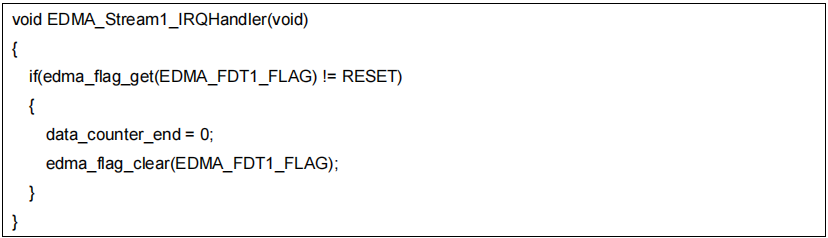

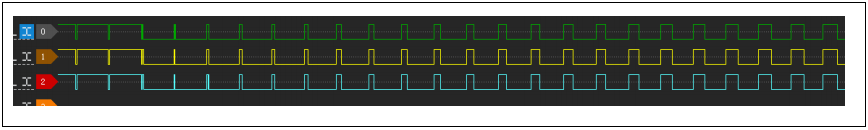

案例 EDMA突发传输

功能简介

EDMA突发传输为EDMA控制器的特有功能。使用EDMA的突发传输将数据从SRAM传输到TMR1的c1dt至c4dt,实现同时改变TMR1四个通道占空比。

资源准备

1) 硬件环境:对应产品型号的AT-START BOARD2) 软件环境project\at_start_f4xx\examples\edma\burst_mode

软件设计

1) 配置流程

- 开启EDMA/TMR1/GPIOA外设时钟

- 配置EDMA数据流

- 配置TMR1的通道1到4输出PWM波形

- 开启传输完成中断

- 开启数据流

- 开启TMR1,使其溢出中断产生DMA请求

2) 代码介绍

- main函数代码描述

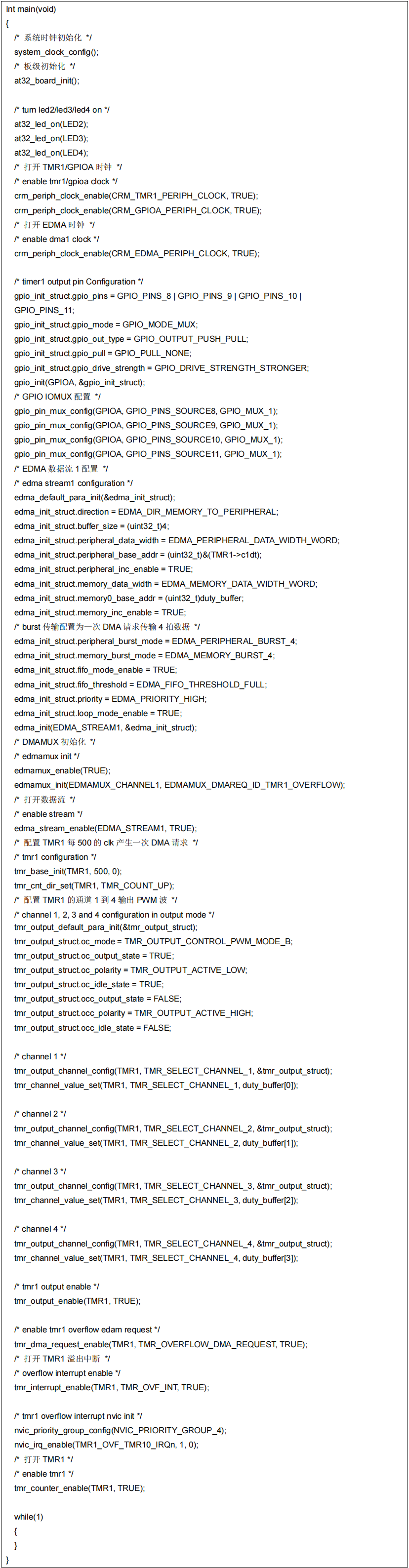

实验效果

- TMR1的通道1到4每个周期会改变一次占空比。

如下为使用逻辑分析仪抓取的几个通道的输出波形,可以看到PWM波形的占空比每个周期都在改变。图15. Burst传输实验结果

案例 EDMA双缓冲区

功能简介

EDMA存储器端双缓存区为EDMA控制器的特有功能。本案例使用EDMA的双缓存区功能将SRAM内部的两块数据通过IIS3传输给IIS2并存储在SRAM内的另外两个数据块中。i2s3_buffer1_tx[32]和i2s3_buffer2_tx[32]为IIS3传输的两块数据,i2s2_buffer1_rx[32]和i2s2_buffer2_rx[32]为IIS2接收到的数据存储区域。

资源准备

1) 硬件环境:对应产品型号的AT-START BOARD使用杜邦线将IIS3与IIS2连接起来,连接关系如下:PD0<------->PA4(ws)PD1<------->PC10(sck)PD4<------->PC12(sd)2) 软件环境project\at_start_f4xx\examples\edma\i2s_halfduplex_edma_doublebuffer

软件设计

1) 配置流程

- 开启EDMA/IIS3/IIS2/GPIO外设时钟

- 配置EDMA数据流,使能双缓存区功能

- 配置IIS3/2

- 开启传输完成中断

- 开启数据流

2) 代码介绍

- 代码描述

实验效果

- LED2/3/4都点亮则表示数据传输正确。

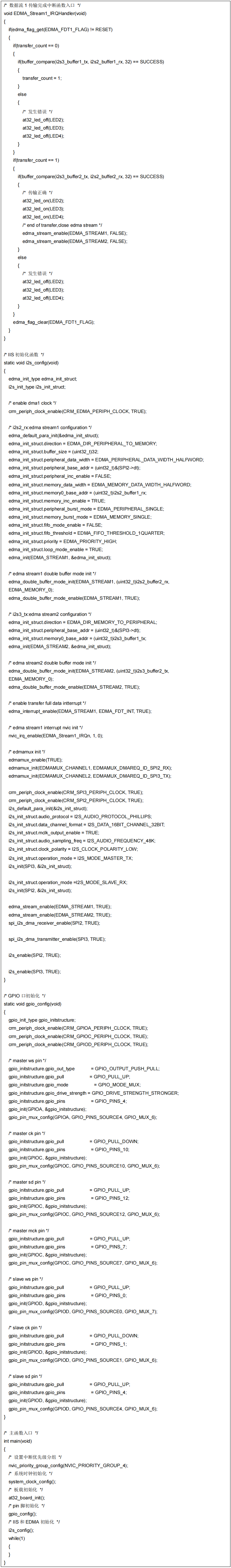

案例 EDMA链接列表传输

功能简介

EDMA链接列表传输为EDMA控制器的特有功能。本案例使用EDMA的链接列表传输功能,将片上存储器的3块区域的数据通过EDMA发送给USART1,USART1在通过自身的TX引脚将数据发送出去。

资源准备

1) 硬件环境:对应产品型号的AT-START BOARD2) 软件环境project\at_start_f4xx\examples\edma\link_list_mode

软件设计

1) 配置流程

- 开启EDMA/USART1/GPIO外设时钟

- 配置EDMA数据流,使能链接列表传输功能

- 开启传输完成中断

- 开启数据流

2) 代码介绍

- 代码描述

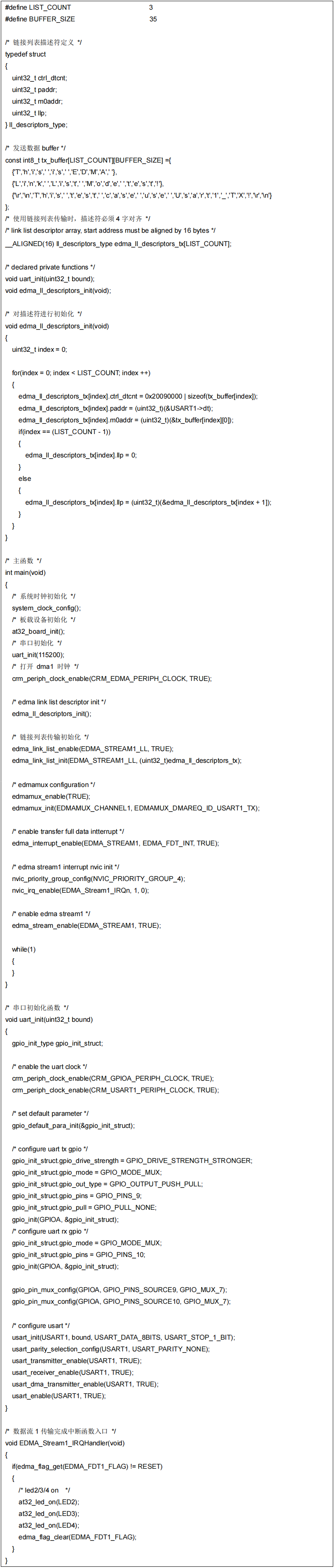

实验效果

- LED2/3/4都点亮则表示数据传输完成,并可通过串口工具查看发送出来的数据。

串口工具接收的数据如下图所示:图16. 链接列表传输实验结果

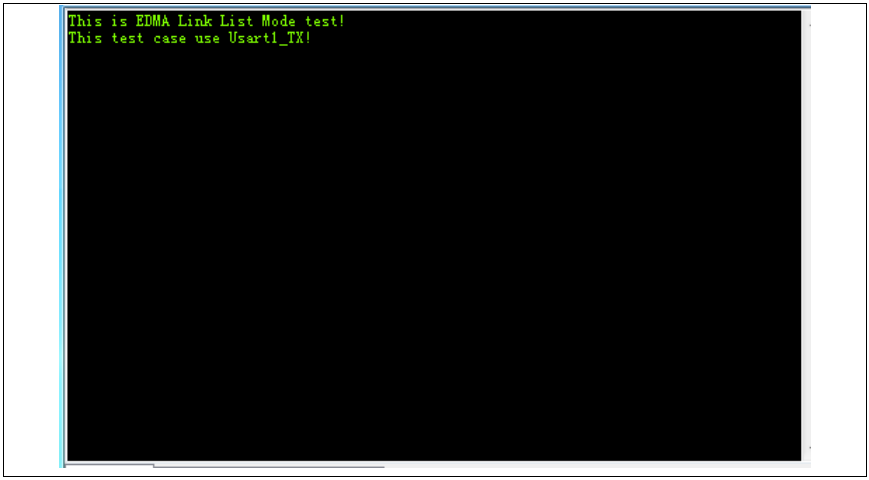

案例 EDMA二维传输

功能简介

EDMA二维传输为EDMA控制器的特有功能。本案例使用EDMA的二维传输功能,将片上存储器的1块区域的数据通过EDMA二维传输功能剪裁出其左边1/2,并通过串口打印出来。

资源准备

1) 硬件环境:对应产品型号的AT-START BOARD2) 软件环境project\at_start_f4xx\examples\edma\two_dimension_mode

软件设计

1) 配置流程

- 开启EDMA/USART1/GPIO外设时钟

- 配置EDMA数据流,使能二维传输功能

- 开启传输完成中断

- 开启数据流

2) 代码介绍

- 代码描述

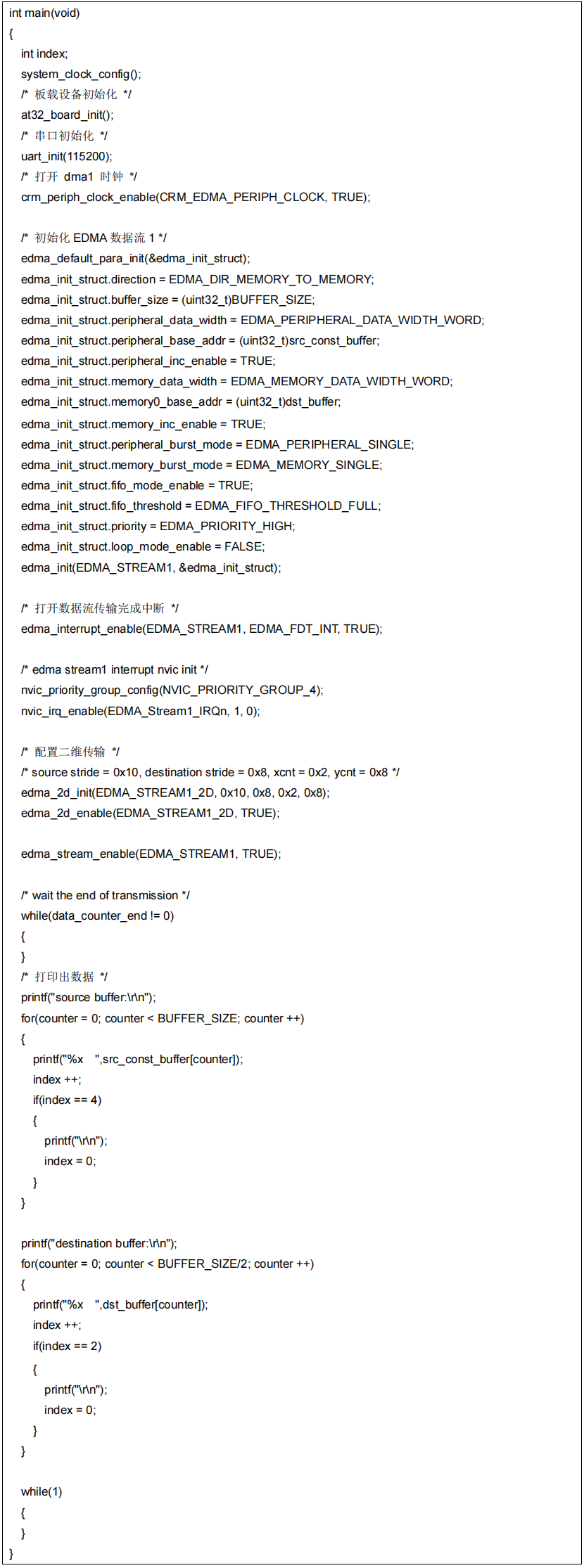

实验效果

- 通过串口工具查看发送出来的数据。

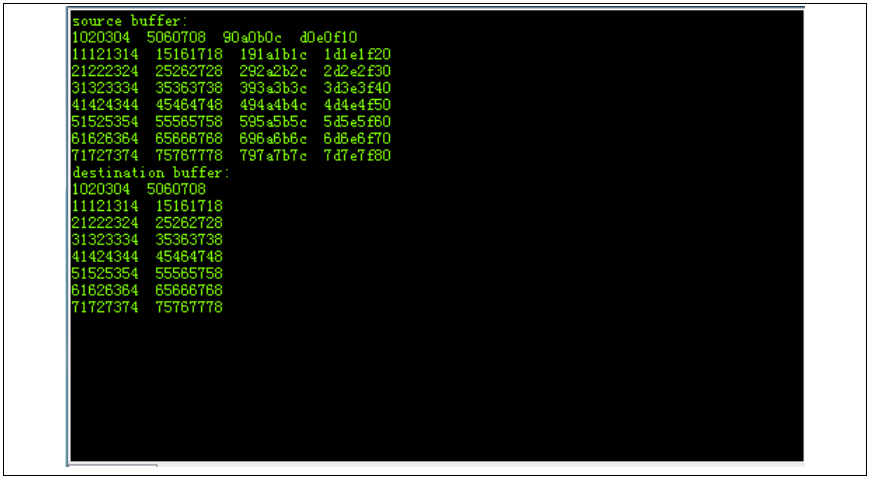

串口工具接收的数据如下图所示:图17. 二维传输实验结果

关于雅特力雅特力科技于2016年成立,是一家致力于推动全球市场32位微控制器(MCU)创新趋势的芯片设计公司,专注于ARM Cortex-M4/M0+的32位微控制器研发与创新,全系列采用55nm先进工艺及ARM Cortex-M4高效能或M0+低功耗内核,缔造M4业界最高主频288MHz运算效能,并支持工业级别芯片工作温度范围(-40°~105°)。雅特力目前已累积相当多元的终端产品成功案例:如微型打印机、扫地机、光流无人机、热成像仪、激光雷达、工业缝纫机、伺服驱控、电竞周边市场、断路器、ADAS、T-BOX、数字电源、电动工具等终端设备应用,广泛地覆盖5G、物联网、消费、商务及工控等领域。

-

AT32F435 & AT32F437入门使用指南2023-12-18 592

-

雅特力AT32F435/F437入门使用指南2023-11-10 9971

-

AT32F435/437时钟配置2023-10-25 647

-

AT32 ERTC入门指南2023-10-24 663

-

AT32讲堂047 | 雅特力AT32F435/437 OTGFS应用笔记2023-03-17 4449

-

雅特力AT32F435/437 OTGFS应用笔记2023-03-08 3590

-

AT32F435/437 EDMA基本功能讲解和案列解析2022-12-19 4134

全部0条评论

快来发表一下你的评论吧 !