启珑微电子全新CLM1543系列模数转换器ADC发布

描述

一、产品概述

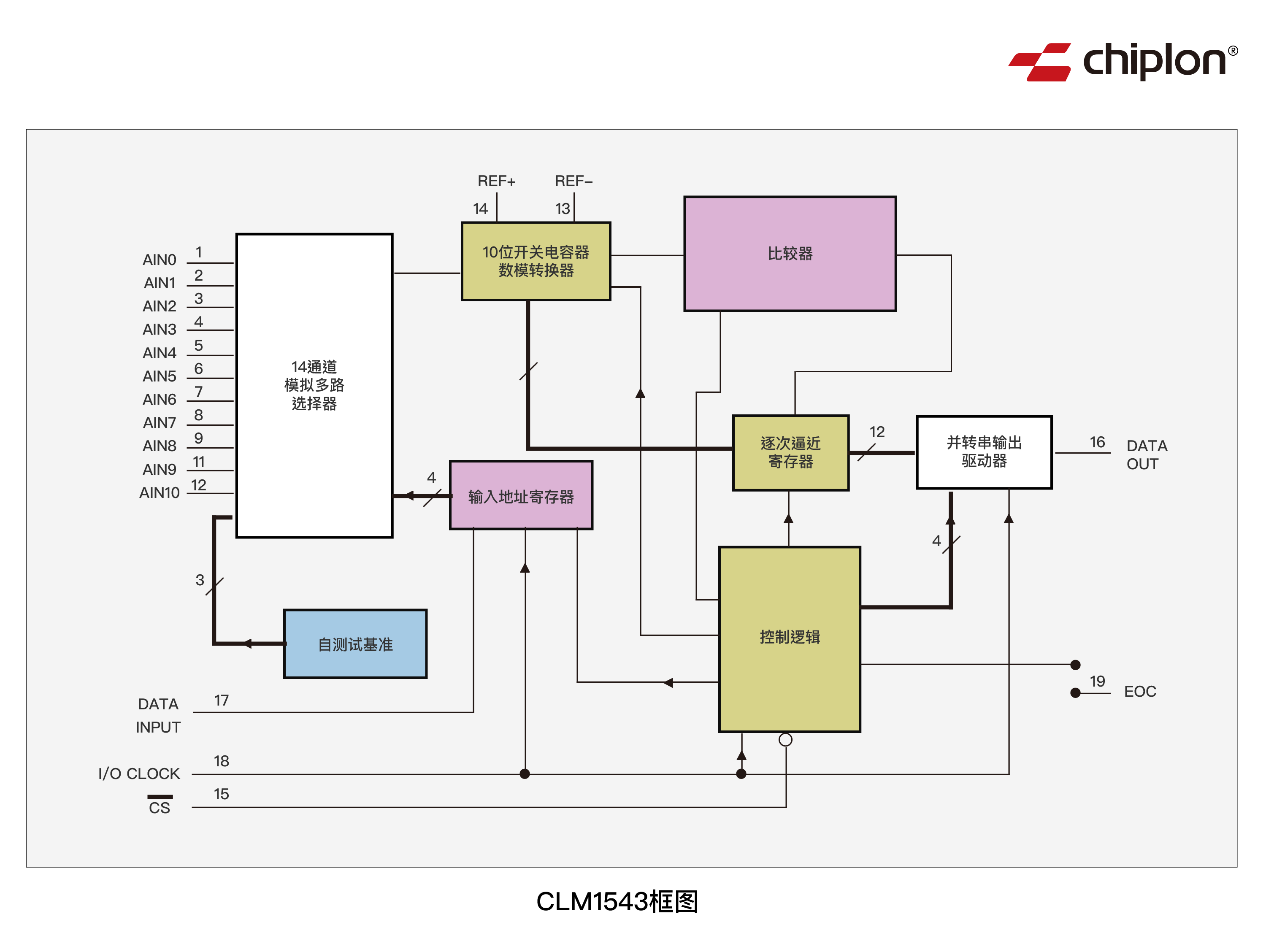

CLM1543是启珑微电子生产的10位、38kSPS ADC,串行输出、片上系统时钟、11 通道模数转换器,采用串行通信接口,具有输入通道多、性价比高、易于和单片机接口的特点,可广泛应用于各种数据采集系统。CLM1543为CMOS 10位开关电容逐次A/D逼近模数转换器。其中A0~A10(1~9、11、12脚)为11个模拟输入端,REF+(14脚,通常为VCC)和REF-(13脚,通常为地)为基准电压正负端,CS(15脚)为片选端,在CS端的一个下降沿变化将复位内部计数器并控制和使能ADDRESS、I/O CLOCK(18脚)和DATA OUT(16脚)。ADDRESS(17脚)为串行数据输入端,是一个4位的串行地址用来选择下一个即将被转换的模拟输入或测试电压。DATA OUT 为A/D转换结束3态串行输出端,它与微处理器或外围的串行口通信,可对数据长度和格式灵活编程。I/O CLOCK为数据输入/输出提供同步时钟,系统时钟由片内产生。芯片内部有一个14通道多路选择器,可选择11个模拟输入通道或3个内部自测电压中的任意一个进行测试。片内设有采样-保持电路,在转换结束时,EOC(19脚)输出端变高表明转换完成。内部转换器具有高速(10μS转换时间),高精度(10位分辨率,最大±1LSB不可调整误差)和低噪声的特点。

二、工作时序

CLM1543的工作过程分为两个周期:访问周期和采样周期。工作状态由CS使能或禁止,工作时CS必须置低电平。CS为高电平时,I/O CLOCK、ADDRESS被禁止,同时DATA OUT为高阻状态。当CPU使CS变低时,CLM1543开始数据转换,I/O CLOCK、ADDRESS使能,DATA OUT脱离高阻状态。随后,CPU向ADDRESS端提供4位通道地址,控制14个模拟通道选择器从11个外部模拟输入和3个内部自测电压中选通1路送到采样保持电路。同时,I/O CLOCK端输入时钟时序,CPU从DATA OUT 端接收前一次A/D转换结果。I/O CLOCK从CPU 接受10个时钟长度的时钟序列。前4个时钟用4位地址从ADDRESS端装载地址寄存器,选择所需的模拟通道,后6个时钟对模拟输入的采样提供控制时序。模拟输入的采样起始于第4个 I/O CLOCK的下降沿,而采样一直持续6个I/O CLOCK周期,并一直保持到第10个 I/O CLOCK的下降沿。转换过程中,CS的下降沿使DATA OUT引脚脱离高阻状态并起动一次I/O CLOCK的工作过程。CS的上升沿终止这个过程并在规定的延迟时间内使DATA OUT引脚返回到高阻状态,经过两个系统时钟周期后禁止I/OCLOCK和ADDRESS端。

三、软硬件设计要点

CLM1543的三个控制输入端CS、I/O CLOCK、ADDRESS和一个数据输出端DATA OUT遵循串行外设接口SPI协议,要求微处理器具有SPI接口。但大多数单片机均未内置SPI接口(如目前国内广泛采用的MCS51和PIC系列单片机),需通过软件模拟SPI协议以便和CLM1543接口。CLM1543芯片的三个输入端和一个输出端与51系列单片机的I/O口可直接连接。软件设计中,应注意区分CLM1543的11个模拟输入通道和3个内部测试电压地址。

四、产品特性

- 10位分辨率A/D转换器

- 11个模拟输入通道

- 三种内置自检模式

- 固有采样和保持功能

- 未调整总误差:最大±1LSB

- 片上系统时钟

- 转换结束(EOC)输出

- CMOS工艺

五、应用

- 智能电网

- 新能源发电

- 电力系统

- 电气化铁轨

- 城市轨道交通

- 电动车充电站

- 智慧楼宇

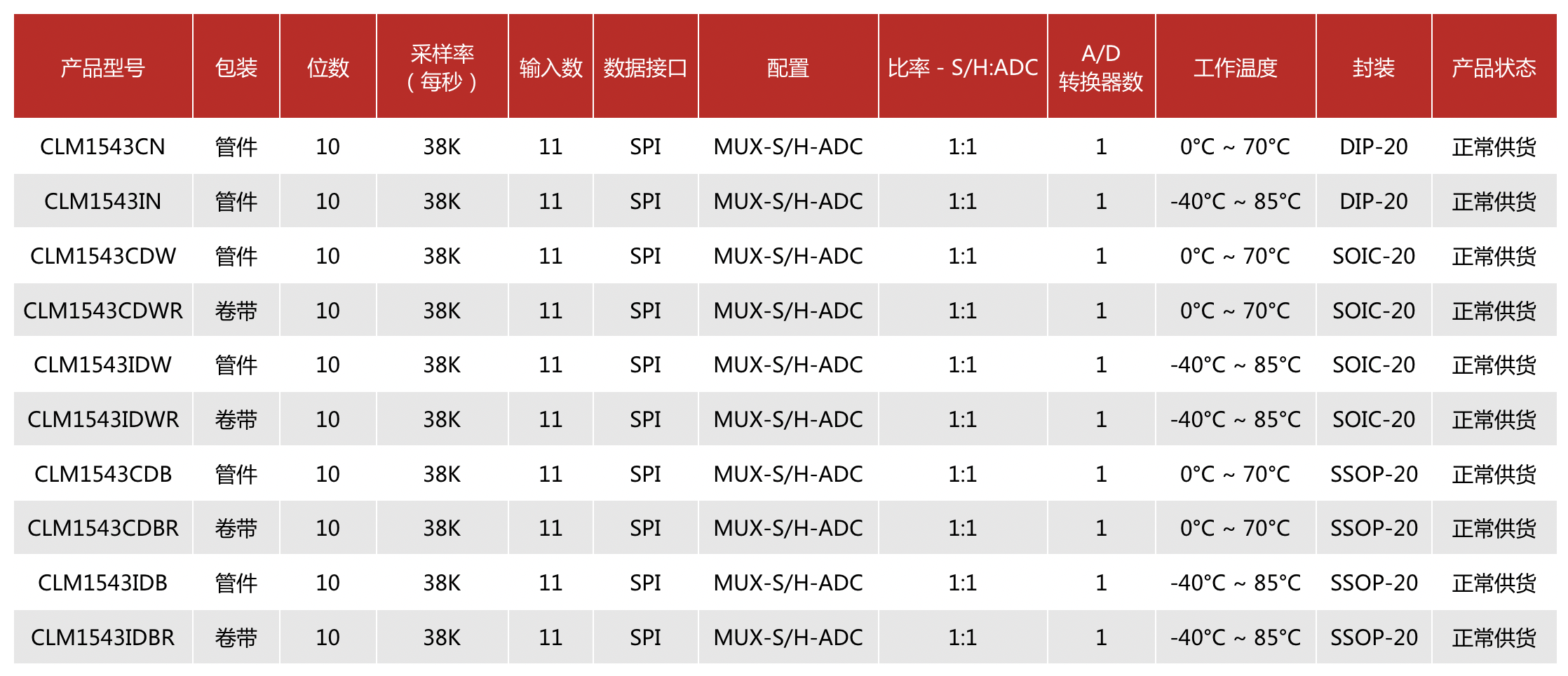

六、选型表

七、应用框图

-

TLC1542-EP和TLC1543-EP模数转换器数据表2024-07-18 501

-

TLV1543C、TLV1543I和TLV1543M模数转换器数据表2024-07-16 483

-

浅谈CW32系列模数转换器(ADC)2023-10-25 2967

-

STM32模数转换器 (ADC)介绍2023-07-22 5418

-

启珑微电子全新CLM2543系列模数转换器ADC发布2023-04-03 1729

-

为什么我们需要模数转换器?哪个ADC转换器更好?2023-02-15 1841

-

模数转换器ADC简介2022-02-17 1828

-

STM32之ADC模数转换器介绍2021-11-08 3314

-

模数转换器(ADC)的基本原理是什么?2021-09-28 2995

-

ADC模数转换器2021-08-06 2100

-

模数转换器(ADC)的配置有哪些流程?2021-07-14 3182

-

5962-9581501HXA高端AD模数转换器2020-07-15 2213

-

电流积分模数转换器(ADC),什么是电流积分模数转换器(AD2010-03-24 3674

-

数模和模数转换器2009-09-16 7967

全部0条评论

快来发表一下你的评论吧 !