M31谈12 FFC多端口缓存器数组

描述

多埠暂存器阵列

多埠暂存器堆,简单来说是处理器中多个暂存器所组成的阵列,故又称多埠暂存器阵列,是处理器(如中央处理器、内嵌式处理器或神经网络处理器)中常见的记忆体,用于暂存指令、数据和位址。暂存器阵列的存贮容量十分有限,但却有读写速度快的优点,因此在处理器架构裡,暂存器阵列被用来储存运算单元计算的中间结果,利用快速存取资料来支援运算单元并改善处理器运算效能。

多埠暂存器阵列的实现方式有两种,其一,藉由逻辑合成的方式,使用标准原件库中的闩锁器或正反器构成;而另一种方式,是使用客製化的多埠静态随机读写存储单元,实现客製化的暂存器阵列,这种多埠存储单元具有专门的读埠与写埠,可以支援多路同时存储。两者相较,第一种能快速地完成的暂存器阵列的设计与实现,而第二种方式则可以提供较佳的面积与效能。

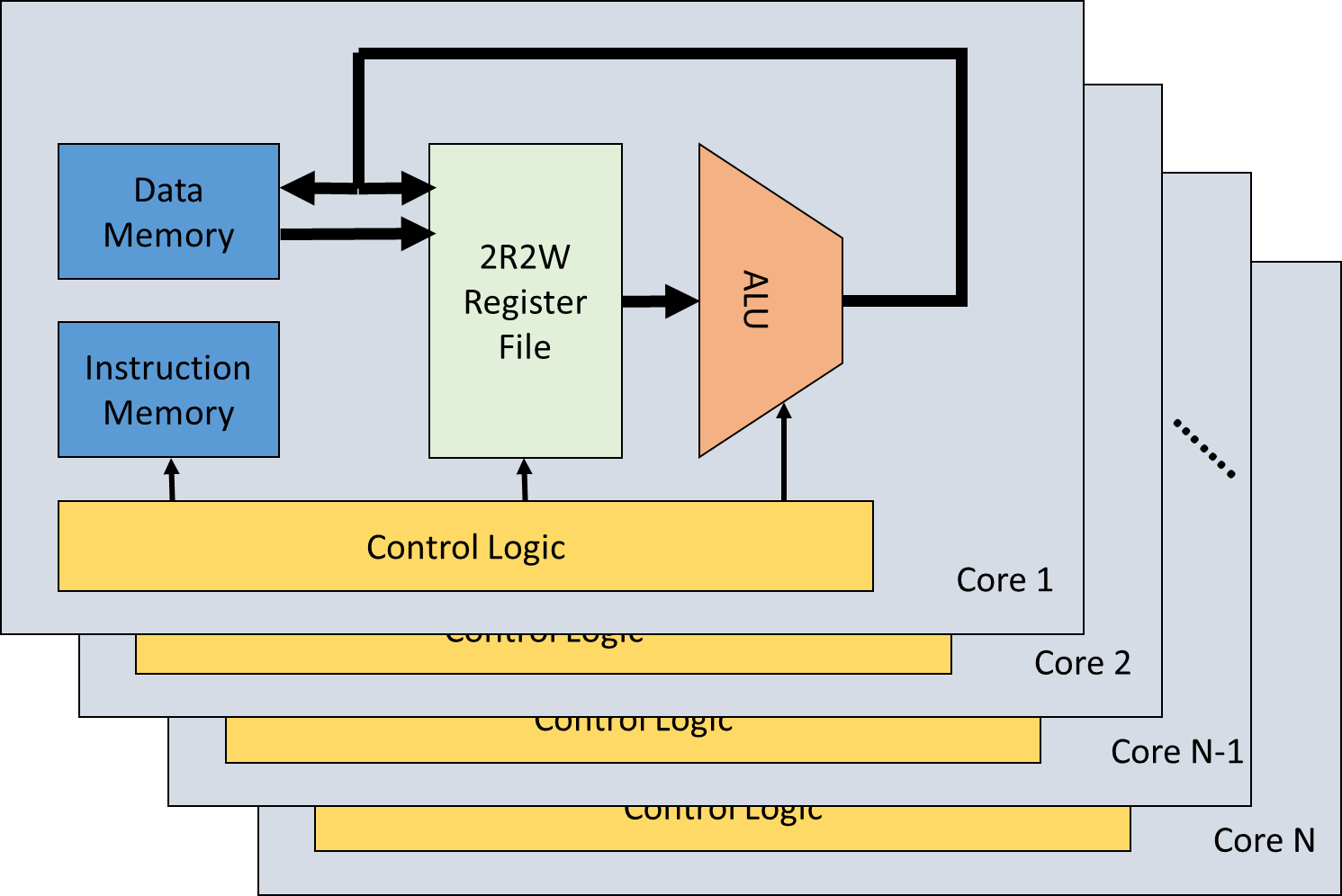

图: 2R2W Register File in Multi-core Computing Structure

图: 2R2W Register File in Multi-core Computing Structure

分时多工的创新技术

针对客製化实现多埠暂存器阵列,M31提出分时多工的创新技术,优化暂存器阵列的控制单元,有效提高记忆体单元的储存与读取频宽,可使用晶圆厂提供的标准静态随机读写存储单元(如单埠记忆体单元、双埠记忆体单元)完成多埠暂存器阵列设计与实现。此一创新技术,不但可以缩短设计时间、缩短交货流程,更可以提供最佳优化面积与效能的多埠暂存器阵列,协助客户完成更具有竞争力的处理器设计。

客製化记忆体模组区块

M31 提供完善的设计解决方案,採用TSMC 12奈米先进製程,针对市场的超高速操作需求,提供2R2W的4埠静态随机读写暂存器(SRAM),各埠皆有独立的操作模式,且不能互相干扰,此外,M31记忆体团队使用读写的屏蔽技术,确保操作时资料读写的稳定性,并同时兼顾CPU/NPU对于平行处理资料运算读写的需求;而针对晶圆厂的SRAM bit cell架构,M31所客製化记忆体模组区块,可大幅减少由传统闩锁器或正反器组成所消耗的面积与功耗,并且,M31开发出boosted amplifier架构,克服bit cell自身读取速度的极限,能进一步满足处理器内部大于兆频以上的超高频需求。

-

多端口SDRAM控制器的设计与实现2009-08-27 505

-

M31 BCK USB 2.0取得USB-IF协会认证2012-09-04 2176

-

三星Galaxy M31跑分曝光,三星M系列有望2020年推出2019-12-30 5643

-

三星Galaxy M31正式发布 起售价约合人民币1456元2020-02-26 3426

-

有关三星Galaxy M31的所有信息2020-02-28 3441

-

三星Galaxy M31最近在印度推出2020-03-08 2637

-

M31谈高速PCIe与SSD的发展与挑战2022-12-09 3748

-

M31谈MIPI物理层的规格与发展2023-07-24 4531

-

M31谈MIPI在车用电子的需求与挑战2023-12-18 1884

-

M31在首届Intel Foundry Direct Connect 展示先进SoC开发与创新2024-02-23 1754

-

M31亮相北美设计自动化会议 展示先进制程IP解决方案2024-06-28 1887

-

M31携手高塔半导体,成功研发65纳米低功耗存储器解决方案2024-08-06 1401

-

M31 12纳米GPIO IP获国芯科技采用,点亮先进制程车用电子芯片创新2025-01-18 1123

-

M31与国芯科技携手,12纳米GPIO IP点亮车用电子芯片创新2025-01-13 1281

-

M31 深耕中国大陆IP市场 赋能汽车电子与 AI 应用新突破2025-02-20 1179

全部0条评论

快来发表一下你的评论吧 !