GD25Qxx芯片解读

描述

NOR Flash是一种非易失闪存技术,是Intel在1988年创建。NOR和NAND是现在市场上两种主要的非易失闪存技术。大多数情况下闪存只是用来存储少量的代码,这时NOR闪存更适合一些,而NAND则是高数据存储密度的理想解决方案。

NOR的特点是芯片内执行(XIP, eXecuteIn Place),这样应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。NOR的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。应用NAND的困难在于flash的管理需要特殊的系统接口。目前全球90%市场在前5大NOR FLASH公司,他们是:美光、旺宏、华邦、CYPRESS(已收购台湾宜扬科技)、兆易创新。其它百分之十的市场被国内的XMC(武汉新芯)、PUYA(普冉)、BOYA(博雅)、YICHU(易储)、XTX(芯天下)和其他品牌等占有。NOR FLASH目前的晶圆厂有:台积电、华润上华、联华电子、和舰科技、华虹NEC、华力微电子、武汉新芯、中芯国际等,前几大封装测试厂有:日月光、安靠封测、矽品科技、京隆科技、南通富士通、华润安盛、天水华天等。1,一般描述

先记住下面的参数:

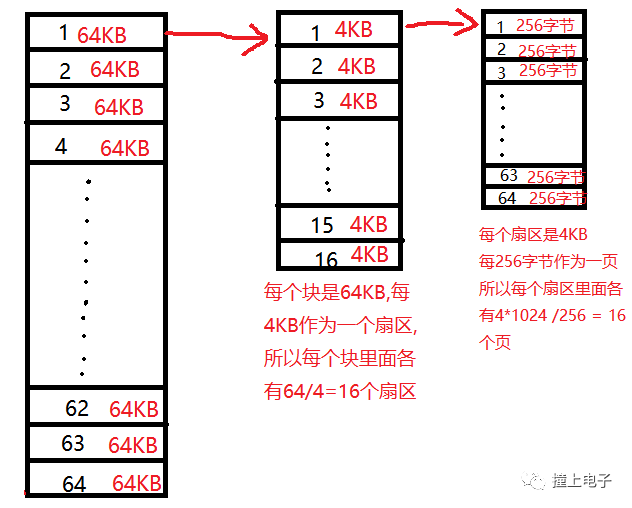

•Page:256 Bytes•Sector:16 Pages(4KB)•Block:16 Sector(64KB)

GD25Q80•8M-bit(1024K Bytes)•4096个Page•256个Sector•16个Block

GD25Q16•16M-bit(2048K Bytes)•8192个Page•512个Sector•32个Block

数据写入的时候只能按照Page来写入,最多一次只能写256个字节,也就是一个页的空间。每次写入都要先擦除。数据擦除只能按扇区擦除或按块擦除。可以按 16 页一组(4KB 扇区擦除)、128 页一组(32KB 块擦除)、256 页一组(64KB 块擦除)或者整片擦除(chip erase)。支持标准的 SPI(Serial Peripheral Interface),也支持高性能的 Dual/Quad I/O SPI。支持的 SPI 时钟频率高达 120MHz,以及当使用快速读 Dual/Quad I/O 指令时,Dual I/O 模式的等效时钟频率 240MHz(120MHz * 2)和 Quad I/O 模式的 480MHz(120MHz * 2)。这样的传输速率超过标准的异步 8 位和 16 位的并行 Flash 存储器。Hold 管脚和 Write Protect 管脚提供了更进一步的控制灵活性。此外,设备支持 128 位唯一UID号。数据保存时间20年,而EEPROM的数据保存时间有100年。

2,管脚描述

写保护(Write Protect)管脚用于预防状态寄存器被写,该功能需要结合状态寄存器的块保护(Block Protect)位(CMP,SEC,TB,BP2,BP1 和 BP0)以及状态寄存器的保护位(SRP0)一起使用。小至 4KB 的扇区,大致整个存储阵列都能被硬件保护。/WP 管脚低电平有效,如果状态寄存器2 的 QE 位被置为 Quad I/O,/WP 管脚的功能不再是写保护,而是 IO2。

HOLD(/HOLD)

/HOLD 管脚允许设备被选中后能够暂停,当 /HOLD 管脚被拉低且 /CS 为低电平时,DO 管脚将变成高阻抗,而 DI 和 CLK 管脚将会被忽略。当 /HOLD 被拉高,设备操作恢复。在多个设备共享同一个 SPI 信号时,/HOLD 功能就很有用了。/HOLD 管脚低电平有效,当状态寄存器2 的 QE 位被置为 Quad I/O 时,/HOLD 管脚功能失效,而变成 IO3。Serial Clock(CLK)SPI 串行时钟输入管脚为串行输入和输出操作提供时序。双倍SPI指令使用”Fast Read Dual Output and Dual I/O(3B和BBhex)”指令支持双倍速SPI操作。这些指令允许数据以正常速度的两到三倍的在设备间传输。双倍读指令适用于 上电时快速加载代码到RAM 或者 直接从SPI总线上执行代码(XIP) 的情形。当使用双倍速SPI指令时,DI和DO引脚将充当 IO 0和IO 1.四倍速SPI指令使用”Fast Read Quad Output”、” Fast Read Quad I/O” 、”Word Read Quad I/O” 和 “Octal Word Quad I/O”指令(6B、EB、E7、E3)支持四倍速SPI操作。这些指令允许数据以正常速度的四到六倍的在设备间传输。四倍读指令显著提升连续和随机访问传输速度,这速度满足将代码快速加载到RAM或者直接在SPI总线上执行(XIP)。使用四倍速SPI指令时,DI和DO引脚将充当 IO 0和IO 1 ,WP和HOLD充当IO2 和IO 3。四倍速SPI指令要求状态寄存器2中的QE功能位打开。3,内存区分类GD25Q32的容量是32Mbit,也就是32/8=4MB字节=4*1024=4096KB字节。GD25Q32规定每64KB字节作为一个块,所以该芯片总共分成了 4096K/64K=64个块。GD25Q32还规定每4KB字节作为一个扇区,所以每一块总共分成了 64K/4K=16个扇区。GD25Q32还规定每456字节作为一页,所以每一扇区总共分成了4*1024/256/4K=16个扇区。

-

请问谁有qspi w25qxx系列的历程吗?2018-11-14 3892

-

请问调用W25QXX_Write出现RAM不够怎么办?2020-03-24 2261

-

回收GD25Q64CSIGR 收购GD25Q64CSIGR2021-04-27 763

-

标准SPI接线方式驱动W25QXX2021-08-10 1321

-

如何实现STM32H750_QSPI_W25QXX_XIP的仿真?2021-11-23 1955

-

简单说一下W25Qxx芯片2021-12-13 2705

-

如何用串口给W25Qxx刷字库放图片?2021-12-16 2097

-

W25QXX系列驱动相关资料下载2022-01-10 2032

-

请问CH549有关于HID+模拟U盘(w25qxx)的例程吗?2022-07-04 934

-

请问W25Qxx的FLASH可以硬件做成只读的吗?2023-11-08 473

-

GD25LQ32C数据手册2016-12-17 1611

-

闪存芯片GD25Q64E数据手册下载2021-05-31 3157

-

W25Q128JVSIM与GD25Q128ESIGR引脚兼容分析2025-10-13 1542

全部0条评论

快来发表一下你的评论吧 !