玩转先楫HPM6000系列双核(下)

描述

在《玩转MCU双核(上)》文章里,我们给大家介绍了先楫HPM6000系列双核的特性、使用方法以及工程编译与调试。本文紧接上篇内容,给大家详细阐述双核的通信方式、资源分配以及双核应用eRPC架构。如果大家在练手过程中,有其他的建议和想法,欢迎给我们留言互动。

双核的通信方式

Communication

HPM双核通信方式有那些?这里列举如下:

A. 通信外设通信

如enet/uart/spi/can/i2c/gpio等等。Core0和Core1可通过通信外设相互之间发送消息来通信。

( 注意:此方案会浪费对应的通讯外设,且需要硬件上支持。)

B. 共享内存RAM通信

Core0和Core1通过访问同一片内存RAM来达到通信。如:一个核写,另一个和读。

共享RAM要点

1. 双核下的共享RAM区域地址及大小必须相同。

2. 为防止CPU cache的影响,共享的RAM区域在双核下均要设置为nocache区域或者在访问前后强制刷新cache。

注意:如果设置为nocache区域,core0和core1中均要调用初始化PMP。

例如:

HPM-SDK双核例程下,双核linker文件中,均已分配了SHARE_RAM区域。

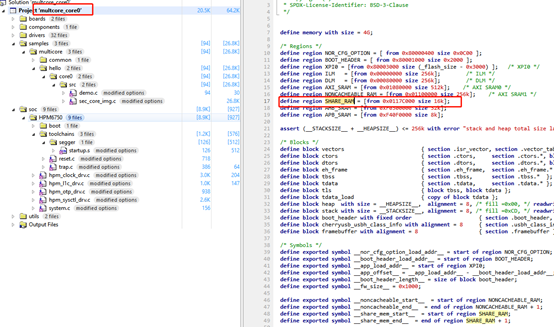

Core0 linker文件中的SHARE_RAM区域分配:

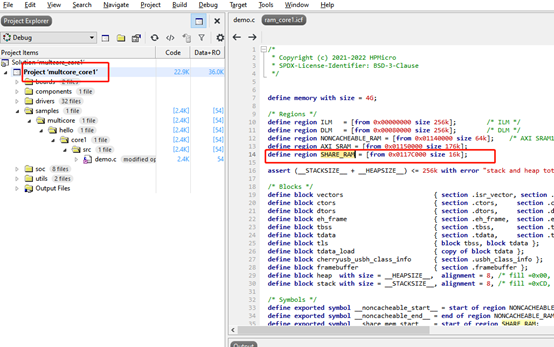

Core1 linker文件中的SHARE_RAM区域分配:

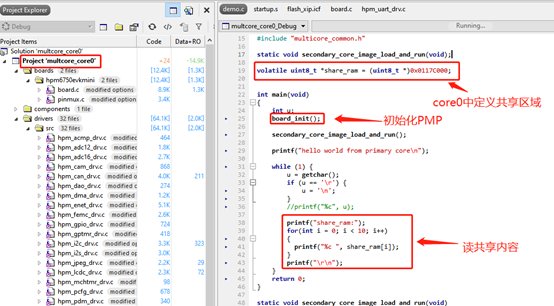

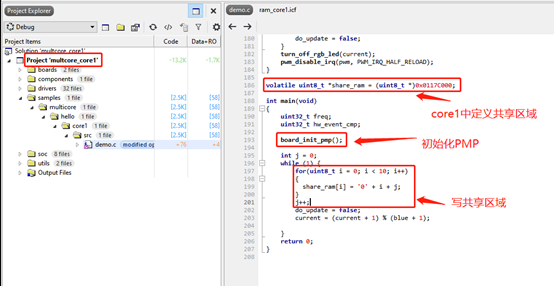

工程中定义共享RAM区域,并访问读写。

Core0工程下设定nocache区域,并初始化PMP。

Core1工程下同样设定为nocache区域,并初始化PMP。

如下:

Core0工程

Core1工程

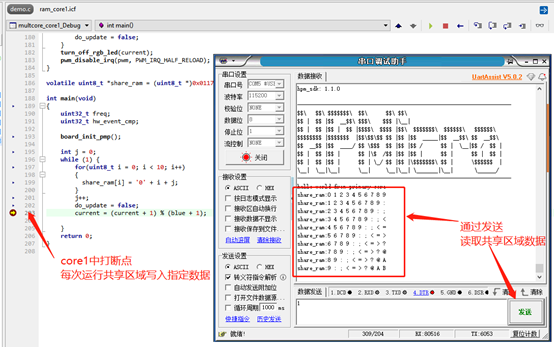

通过debug调试,在core1中打断点,core1中写共享区域。

通过串口发送数据,在core0中读取共享区域。

运行结果如下:

从运行结果看,core1中写入的共享区域的数据和core0中读取的共享区域的数据是一致的。

C. 通信信箱MBX通信

HPM支持独有的通信信箱MBX来进行处理器核间通信。主要特性如下:

● 支持 2 个寄存器访问接口

● 每个接口支持 TX FIFO 和 RX FIFO

● 支持标志位反映 TX FIFO 和 RX FIFO 状态

● 支持生成中断

双核MBX通信,参考HPM-SDK例程drivers/mbx。

(注意:当然也支持读写Flash来通信,考虑到并发读写Flash带来的异常,此通信方案不推荐使用。)

在这里,推荐大家结合B和C方案,通过MBX做双核间的消息传递,通过共享RAM的方式来达到大数据的通信。

当然通过双核通信来实现双核间的同步和互斥。例如:通过MBX通信,实现类似OS互斥锁和信号量的功能。

双核的资源分配

Resources

HPM双核资源,除了以下资源是Core0和Core1各自私有的,其余资源均需要合理分配。

● CPU 自身的指令/数据本地存储器 ILM / DLM 为私有

● FGPIO 为私有

● 平台中断控制器 PLIC 为私有

● 软件中断控制器 PLICSW 为私有

● 机器定时器 MCHTMR 为私有

A:双核Flash 资源分配要点

防止Core0和Core1并发同时访问同一个flash。例如:结合MBX通信,实现互斥锁来避免并发访问。并且考虑到flash_xip(非xip的除外) 片上运行,同时应在访问flash前后,禁止和使能全局中断。

B:双核RAM 资源分配要点

1. 除了共享ram区域和各自私有的ILM/DLM区域。其余sram和sdram在core0和core1的分配中不可重叠,避免出现未知数据错误。

2. Core0和Core1共享RAM区域的分配,地址及大小必须相同。

C:双核访问同一外设要点

通常应该避免双核访问同一个外设。如果有需求要同时访问同一外设,需要注意以下几点:

1. 禁止双核均初始化同一外设。如:Core0已经初始化相关外设,Core1无需再次初始化。

2. 防止Core0和Core1并发操作同一外设。例如:结合MBX通信,实现双核互斥锁来防止并发操作。

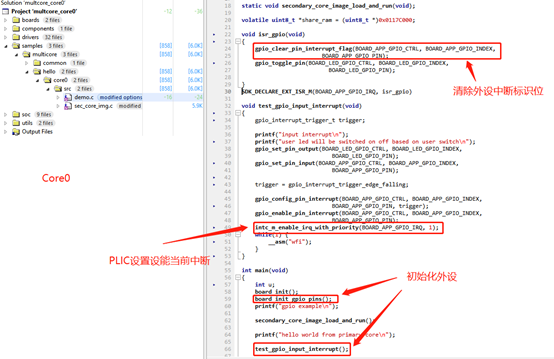

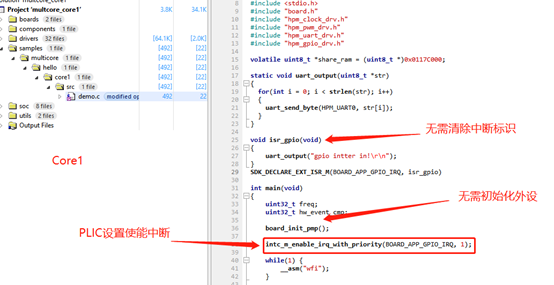

D:双核使能同一外设中断要点

由于双核Core0/Core1各自的PLIC平台中断控制器是私有的,如果双核均使能了同一个外设中断,需注意以下几点:

1. 禁止双核均初始化同一外设。如:Core0已经初始化相关外设,Core1无需再次初始化。

2. 双核各自的私有PLIC中均要使能当前中断。如:Core0的PLIC中使能了IRQn_GPIO0_Z中断,Core1的PLIC中同样也要使能IRQn_GPIO0_Z中断。

3. 禁止双核外设中断处理接口中均清除中断标识位。如:Core0中清除了当前外设中断标识位,Core1中无需再次清除。如下:

E:双核异常要点

由于HPM双核是两个独立的CPU,是主从架构。

当双核出现异常情况,需要注意以下几点:

1. 其中一个核出现异常(crash)但未重启,另一个核仍能正常运行,不受影响。

2. Core0异常重启,Core1也会随之重启。

主从架构,Core0为主,Core1为从。当复位发生时,系统总是由Core0启动,而Core1处于待机状态,需要Core0装载启动Core1。

3. Core1异常重启,Core0仍正常运行,不受影响。

推荐结合看门狗WDG来合理处理双核异常情况。

双核应用eRPC架构

eRPC Structure

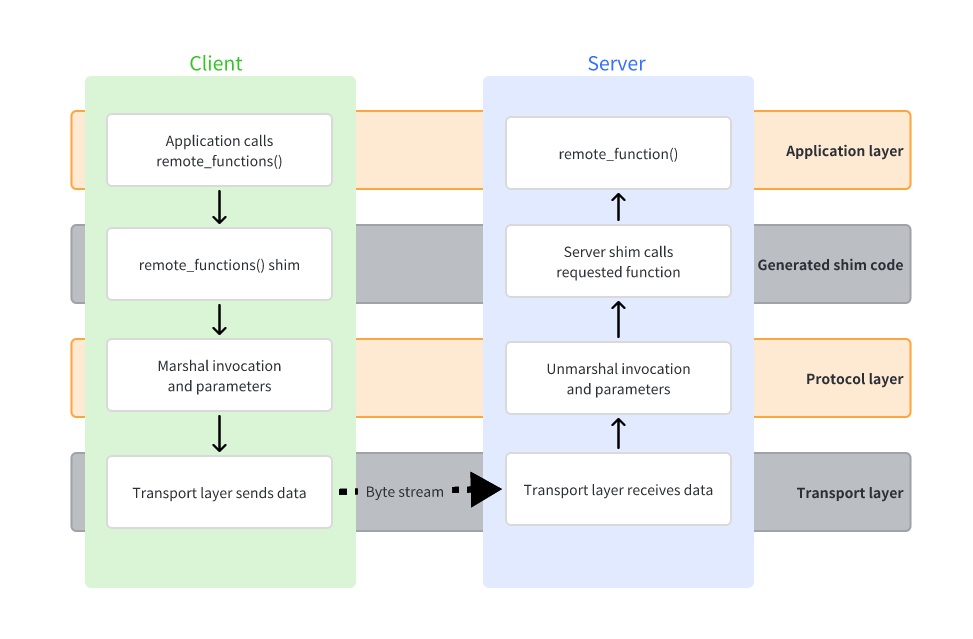

eRPC(Embeded Remote Procedure Call) 是一个简单的、易用的、高效的远程调用框架。

RPC是一种机制,Client端通过简单的本地函数调用,就能使用Server端提供的服务。对于Client端而言,使用远程服务就像调用应用程序中内置的库函数一样。

当Client端调用远程函数时,该函数的标识(identifier)和函数的参数(parameters)将被序列化到字节流中,此字节流通过传输层的通信通道(IPC、TCP/IP、UART、SPI等)传至Server端。Server端收到字节流数据后,解析函数参数并根据标识选择调用的服务函数。若函数有返回值,则Server端将返回值序列化并发送回Client端。

以下是RPC架构框图(此图仅显示一个传输方向,省略了来自Server端的回复)。

对应多核(MultiCore)应用,通过RPMsg-Lite是作为传输层;对于多芯片(MultiProcessor)应用,通过UART、SPI、TCP/IP等作为传输层信号通道。

HPM6000系列双核应用,将使用RPmsg-Lite作为传输层。

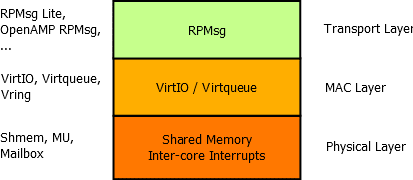

RPMsg-Lite(Remote Processor Messaging Lite)是ePRC的传输层,RPMsg协议定义了一个标准化的二进制接口,用于在多核系统中内核之间的通信。

RPMsg协议的分层模型如下:

它是实现eRPC的关键部分,采用的数据通讯方式为共享内存和消息通知。

详细介绍参考GitHub官方网站:

https://github.com/EmbeddedRPC/erpc

https://github.com/nxp-mcuxpresso/rpmsg-lite

HPM-SDK已完成了eRPC的移植,采用RPmsg-Lite作为数据传输层,采用MBX作为事件通知。

例程:hpm_sdk\samples\multicore\erpc

-

HPM6000系列芯片内部模拟地和数字地2023-07-10 3428

-

请问HPM6000系列MCU如何使用硬件DSP单元?2023-05-26 895

-

先楫HPM6000系列MCU双核的通信方式和资源分配2023-05-14 5633

-

玩转MCU双核(上) 先楫HPM6000系列双核怎么玩?答案超乎你想象!2023-05-12 4846

-

先楫HPM6000系列双核MCU怎么玩?2023-05-10 2864

-

先楫半导体 HPM6000 系列常见的两种二级Bootloader 方案介绍2023-04-02 3425

-

先楫半导体HPM6700系列正式合入OpenHarmony社区主干2022-11-11 1243

-

应用贴士 | HPM6000系列 Security Flash介绍2022-09-29 2171

-

应用分享| HPM6000系列片上SRAM揭秘2022-09-19 3331

-

如何使用Segger Embedded Studio开发先楫HPM6750?2022-07-26 4770

-

HPM6000系列 ADC 相关硬件设计教程2022-07-22 2636

-

HPM6000系列微控制器 CMSIS DAP调试器使用指南2022-06-19 5956

-

先楫半导体重磅推出HPM6300系列—— 高性能,低功耗,高性价比2022-05-07 6248

-

先楫半导体HPM6750EVKMINI评估板免费试用2022-04-12 2408

全部0条评论

快来发表一下你的评论吧 !