行业资讯 I 当芯片变身 3D 系统,3D 异构集成面临哪些挑战

描述

在去年的IEEE 电子设计流程研讨会(IEEE Electronic Design Process Symposium,即EDPS)上,Cadence 资深半导体封装管理总监 John Park 先生进行了一场关于 3DHI(即 3D 异构集成)挑战的演讲。Cadence 大多数人的从业背景都是 IC 设计或 PCB 设计,而 John 则有着丰厚的封装背景。在过去的几年里,这一直是一个相对较小的领域,但却在几乎一夜之间成为了半导体业界最受关注的话题之一。

此次 IEEE 电子设计流程研讨会持续了一周时间,期间涵盖各项会议讨论,包括 Samsung Foundry Forum、Samsung SAFE 和 PCB West 等。

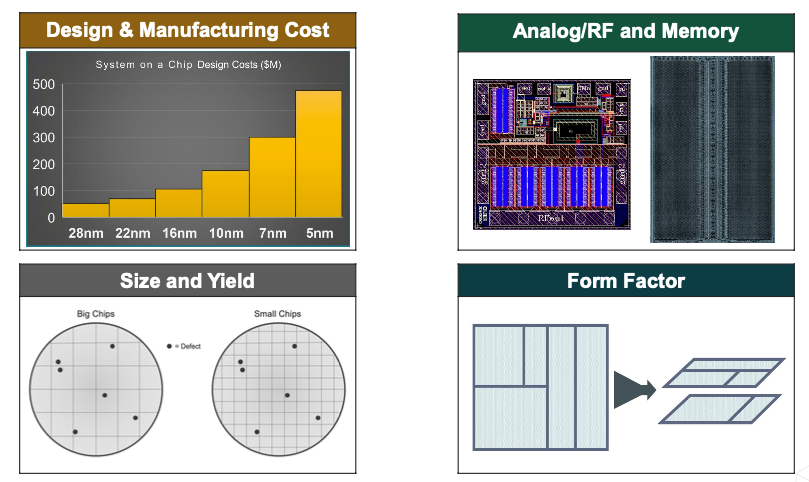

上述所有会议讨论的最大驱动因素是经济考虑,但要展开全面的分析需要大量的价格信息;这些信息并不容易获得,而且一直在不断变化。最明显的是某个特定尺寸的裸片在特定工艺下的成本,还有不同的多裸片封装技术的成本。在过去的几年里,3D 封装技术已经足够普及,成本似乎已经降到足够低,可以得到更广泛地使用。晶圆成本随着每个工艺节点的增加而上升,这意味着设计一个大型系统级芯片与把多个裸片放入一个封装之间的权衡因素已经改变,并将继续改变。

John Park 在演讲一开始就总结了目前的形势:

无论是技术上还是成本上,遵循摩尔定律已不再是最佳选择。

成本的主要驱动因素之一是良率,而大裸片的良率要低于总面积相同的两个(或更多)小裸片。这是因为,大裸片更难避免晶圆上的各个缺陷。另一个重要的驱动因素是通过采用不同的工艺制作不同的裸片(如模拟和射频)来优化设计的能力,只用最先进的工艺节点制作价值最高的数字逻辑部分。还有一个挑战则是如何将足够多的电子元件装入外形尺寸非常小的设备,如智能手表。举例来说,此类设备可能在垂直方向有空间摆放元件,但在水平方向没有足够空间。

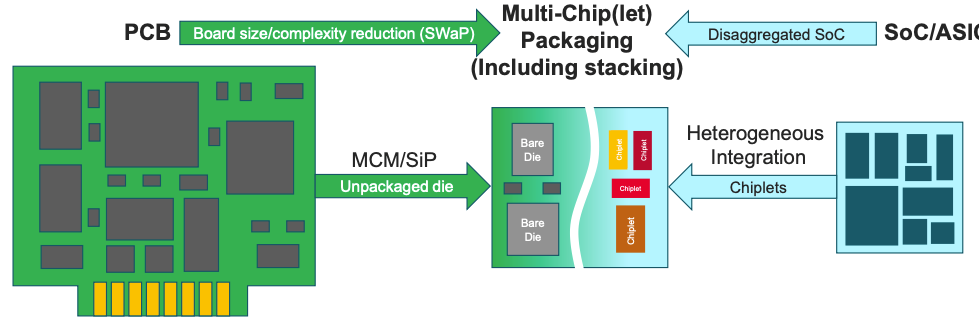

从系统级芯片到异构集成的过渡实际上是在两个方向进行的。一个方向是避免在 PCB 上放置大量封装,而是将这些封装中的裸片置于一个单一的多芯粒设计中。这种方法的优点是面积尺寸更小,构造更简单,带宽 I/O 更高,并且功耗更低。

另一个方向是将一个大型系统级芯片分解成独立的裸片,分别进行制造,然后再将其集成到一个单一的封装中。这种方法的 NRE 成本较低,能够加快产品上市,可以突破光刻极限,实现尺寸更大的设计,并且 IP 使用模式更加灵活。

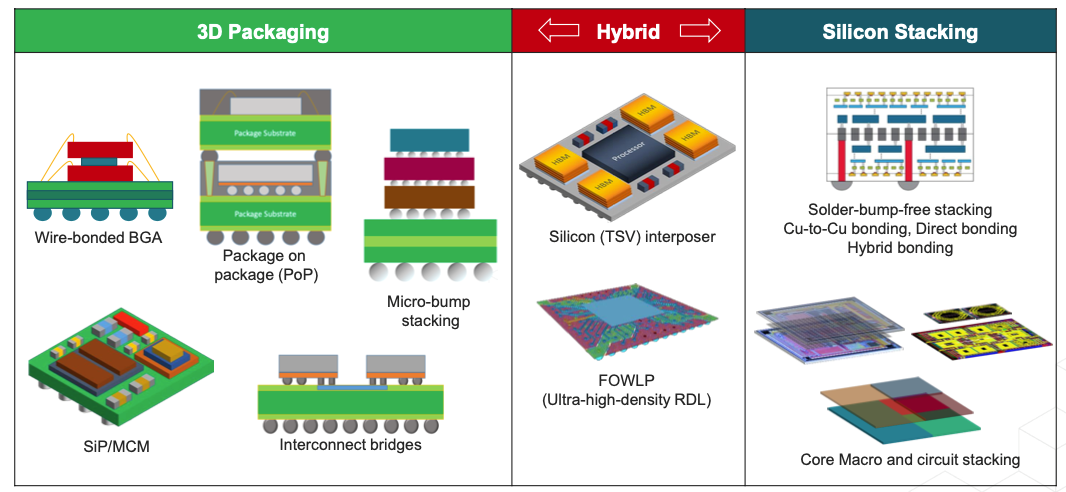

当然,这并不是什么新鲜事。30 多年来,我们一直拥有各种形式的多芯片模块 (MCM)。但它们非常昂贵,而且通常只用于搭建雷达等专门用途。现在有了更丰富的技术组合(见下图)——

上图左边是可用于“常规”裸片的封装技术,即没有任何硅通孔 (TSV) 的裸片;右边是硅堆叠技术,使用没有任何 bump 的铜-铜直接键合;中间是在 2.5D 中介层上的裸片混合结构,或称为扇出型晶圆级封装 (FOWLP) 的超高密度封装。对于左边和右边的技术,各自需要进行的设计有很大的不同。

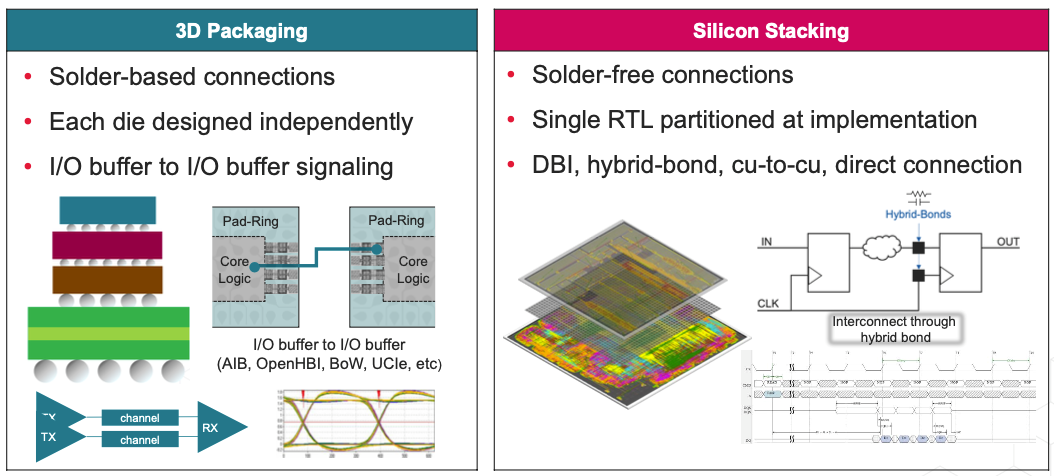

3D 封装(与硅堆叠不同)使用基于焊点的连接 (bump),每个裸片都是独立设计的,信号传递通过 I/O 缓冲器完成,与 PCB 上的封装技术类似。而硅堆叠的连接则不通过焊点,设计是一个单一的 RTL,在物理互连过程中进行切割分划。

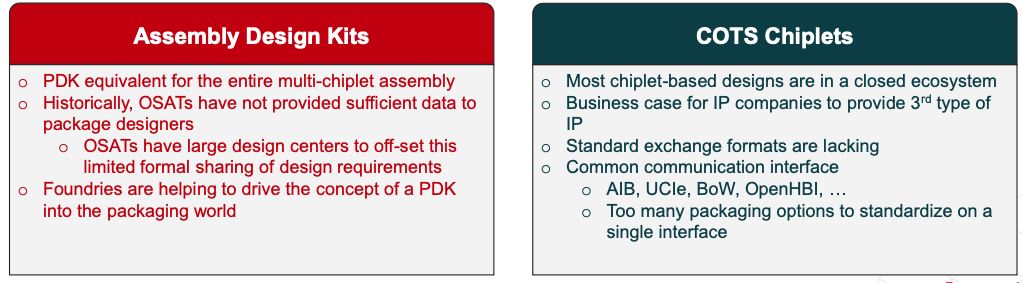

在演讲中,John 一直在强调的一点是需要使用组装设计套件 (Assembly Design Kits,即ADK)。这相当于我们所熟悉的用于集成电路设计的 PDK。一直以来,封测代工厂 (OSAT) 要么没有,要么不愿意披露封装设计师需要的所有数据。但是代工厂多年来一直存在这个问题——他们需要提供 PDK,但许多原始数据是保密的。

如果有一天出现了芯粒的“零售”市场,我们就需要落实更多的标准化程序(如 UCIe 或 OpenHBI)。如今,除了使用 HBM(高带宽存储器)外,多芯粒设计是由一家公司设计完成的,所有芯粒在同一个设计中一起工作,或者,允许芯粒在一些不同的设计中进行配置,这些设计分别具有不同的特征(如性能、价格等)。

更多ADK信息,请阅读《封装组装设计套件 ADK 及其优势》。

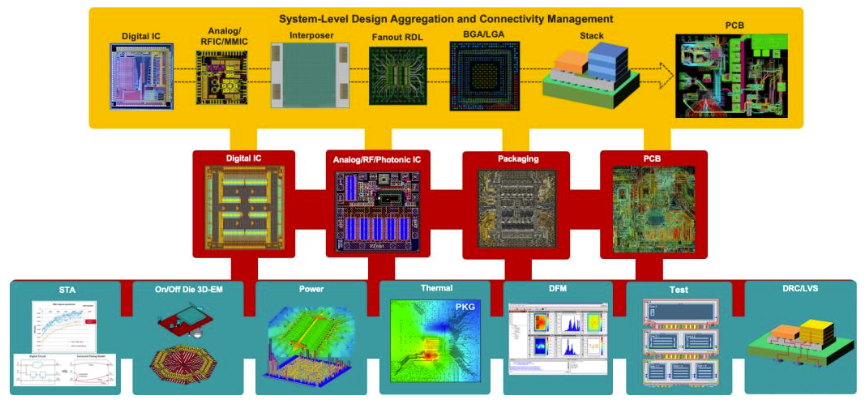

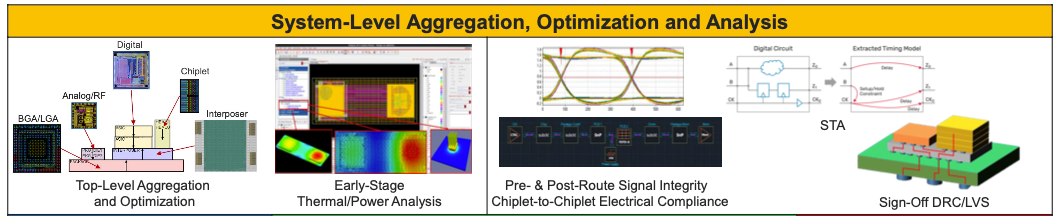

在设计方面,即使用几个或许多裸片来设计整个系统,最大的要求是为整个 3D-IC 建立一个共同的数据库:芯片、芯粒、tile、封装、PCB,甚至可能还包括连接器和背板。显而易见,这些设计的尺寸可能非常大,有数十亿甚至数百亿个器件(当然,更大的设计一直层出不穷)。下面的图表介绍了在进行这些设计时可能涉及的大量工具。

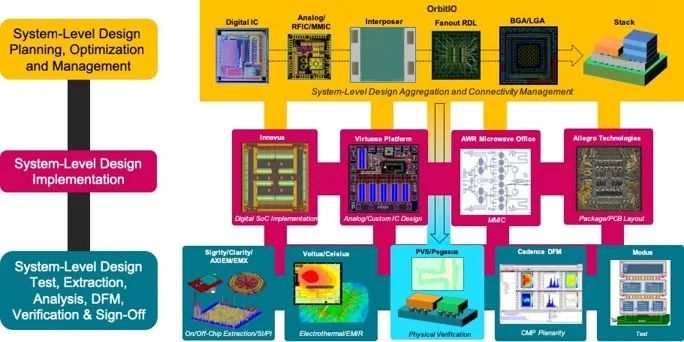

对此,Cadence 有以下产品帮助设计出色完成:

在一个封装中放置多个裸片的最后一个挑战是“已知良好裸片(Know Good Die,即KGD)”。这意味着在组装前需要对芯粒进行广泛的测试(可能是在晶圆分类时),以确保它们通过测试。如果对封装中某个裸片的测试稍有疏忽,就有可能让某个不良裸片蒙混过关,白白浪费了封装成本。由于芯片是坏的,与之一同付诸东流的还有芯片的生产与组装成本。一旦把多个裸片放置在一个封装中,就不是这么一回事了。如果有四个裸片,在最后测试时才发现了其中一个不良裸片,那么其结果不仅损失了一个裸片,还浪费了三个良好的裸片(此时假设没有办法打开封装,也无法以较低的成本完好无损地取回良好的裸片;虽然有时也并非如此)。

-

3D闪存的制造工艺与挑战2025-04-08 2813

-

3D集成电路的结构和优势2024-12-03 3283

-

3D 封装与 3D 集成有何区别?2023-12-05 2551

-

3D异构集成与 COTS (商用现成品)小芯片的发展问题2023-11-27 1874

-

美国斥巨资,发展3D异构集成2023-11-24 2728

-

3D IC制造技术已成主流,异构3D IC还有待进步2022-09-16 1996

-

异构集成基础:基于工业的2.5D/3D寻径和协同设计方法2021-07-05 1177

-

浩辰3D的「3D打印」你会用吗?3D打印教程2021-05-27 8261

-

如何通过Synopsys解决3D集成系统的挑战?2021-05-10 1757

-

英特尔异构3D系统级封装集成2021-03-22 3244

-

MEMS 3D打印技术经常面临各种挑战2020-07-08 4911

-

芯片的3D化历程2020-03-19 2232

-

3D集成系统的测试挑战2012-06-01 2274

-

什么是声卡3D环绕立体声系统/3D立体声系统2010-02-05 2528

全部0条评论

快来发表一下你的评论吧 !