Fujitsu A64FX处理器架构研究

处理器/DSP

描述

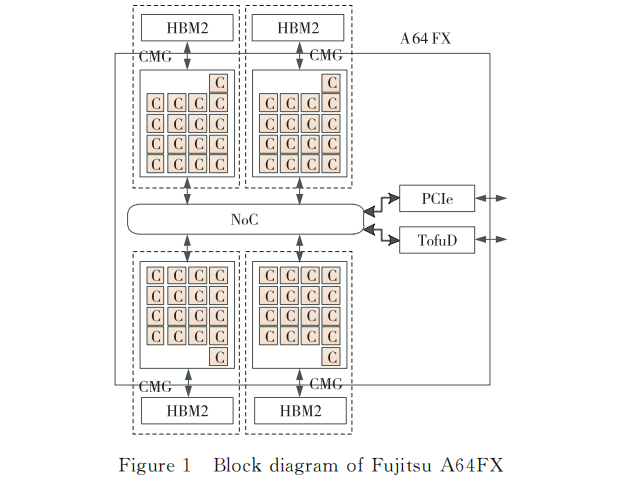

A64FX处理器结构框图如图1所示,分成4个处理核心存储组 CMG(CPU MemoryGroup),每个 CMG 包含13个同构核心、L2Cache和存储控制器,其中12个核心为计算核心,1个为辅助核心,用于运行操作系统和I/O 操作,全片共52个核心。每个 CMG 集成8GB 容量的 HBM2存储器,全片总容量为32GB,总带宽为 1024GB/s。

片上还集成了 PCIe3.016x接口和富士通特有的TofuD互连网络接口与路由器,这些外接口与4个CMG 通过片上网络 NoC(NetworkonChip)实现互连和通信。 A64FX 处理器采用台积电7nm 工艺和 CoWoS封装实现,集成了87.86亿晶体管,最高运行频率为2.2GHz,峰值性能为3.3792TFlops,功耗为200W.

FujitsuA64FX 处理器采 用 64 位 ARMv8.2A 指令集,同时支持以富士通为主导、与 ARM联合开发的可伸缩向量扩展SVE(Scalable Vector Extension)指令集,SVE支持3种128/256/512单指令多数据流 SIMD执 行 宽 度 的 自 动 向 量 化 处 理。

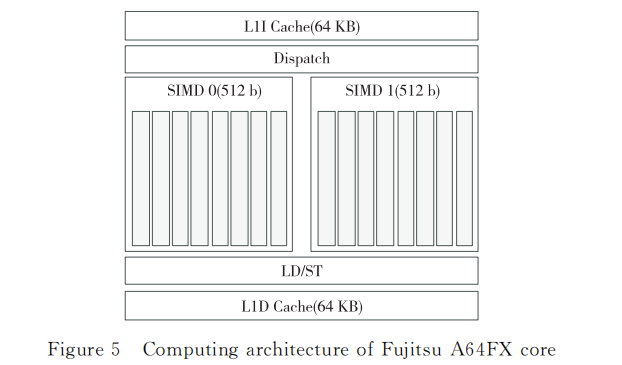

FujitsuA64FX运算核心架构如图5所示,包含2 条 512位宽的向量 SIMD 流水线,共享 64KB 指令 L1I Cache和64KB数据 L1DCache,每条向量流水线集成8/16/32个双/单/半精度浮点乘加部件,并支持8/16/32/64 个 64/32/16/8 位 整 数 乘 加 操 作。为加速AI运算,FujitsuA64FX 处理器还支持16位和8位整数的点积运算。

FujitsuA64FX每拍可以发射 2 条向量浮点乘加指令,并行在2条 SIMD 流水线上执行,因此单个核心每拍执行双精度浮点运算数32个,最高工作频 率 为 2.2 GHz,单 核 心 峰 值 性 能 为 70.4GFlops,全片集成48个计算核心,单处理器双精度浮点峰值性能为3.3792TFlops。

综上所述,FujitsuA64FX 采用超标量多发射和SIMD 并行方式提升性能,同时 SVE(Scalable Vector Extension)指 令 支 持 128/256/512 位SIMD自动向量化处理,扩展应用适用性;支持半精度和16/8位整数运算,并支持低精度点积运算,以加速 AI处理。

审核编辑:刘清

-

简单认识IA-64架构处理器2023-11-27 3372

-

基于SPARC64架构的Arm超级处理器2022-12-20 1777

-

PC处理器Athlon 64 FX-57的性能特点及适用范围2021-01-28 2148

-

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究2020-07-27 4387

-

64位MIPS架构为OCTEON III处理器提供处理能力2020-05-14 2319

-

新架构新动能,64核心的EPYC处理器带来全新体验2020-01-09 3404

-

富士通推出A64FX ARM处理器晶圆 采用台积电7nm FinFET工艺制造2019-12-06 1499

-

日本富士通发布最强ARM处理器,恰恰证明申威的先进性2018-09-18 7799

-

富士通公布最强ARM处理器的A64FX处理器2018-08-22 2467

-

蜕变盈方微16纳米64位处理器架构新品沟通2014-03-20 5526

-

ARM Cortex-A50导入大小核架构 促进64位处理器发展2013-11-18 1973

-

意法半导体率先部署64位ARM Cortex-A57处理器2012-11-06 2181

-

ARM推出具节能效率64位Cortex-A50处理器系列2012-11-01 2408

全部0条评论

快来发表一下你的评论吧 !