FPGA在线调试信号被优化原因分析及防止优化方法总结

可编程逻辑

描述

之前的一篇文章介绍了FPGA在线调试的方法[1]。这几种方法都比较常用,但是现实往往没有这么简单,很多时候,工具在综合,布局布线阶段会对某些代码进行优化,所以实际的电路与代码中的信号无法对应上,也是很常见的事情。而我们常常会使用代码中的信号名来抓取信号,后期布局布线阶段,无法找到对应的电路信号,可能会导致无法抓取信号或者布局布线失败。

一般来说,信号被优化,主要情况大致为两点:

- 多余的bit

例如,我们定义状态机信号state为4bit信号,但实际上我们的状态机只有0,1两种状态。这种情况下,工具会自动认为多余的3bit没有用到,直接将state优化为1bit,所以想直接抓取state完整的信号就没有办法抓到;计数器信号被优化大部分也是因为bit数多余了。

- 重复的信号,或者有更好的设计方法

很多人说verilog编写,心中要有电路。但是对于初学者来说,将verilog代码与数字电路对应上,还是比较困难的,所以他们的代码上,有很多优化空间,也有些代码只是为了“测试”,后期没有驱动其他信号。而工具也较为“智能”地发现这一点,帮助设计者做好优化。然而,设计者的信号可能就会被省略,导致实际电路没有代码对应的信号。

解决这种问题的方法也有多种,分为被动和主动方法。

- 被动方法:将被省略的信号输出

在我初学的时候,遇到这种情况的解决方案,是直接将被省略的信号输出,以上面说的state为例,直接在module的输入输出端口增加一个output reg [3:0] state,并将原来的state定义注释掉。如此一来,信号必须要输出,工具不会对信号进行优化。

对于一些仅仅用于“测试”的代码,没有驱动其他信号而被优化的情况,初学时的方法一般是给它增加一个驱动,让这个信号去驱动别的信号,让工具看到这个信号的“价值”,从而避免它被干掉。

- 主动方法:使用SYNTHESIS 语句防止被优化

使用专用的SYNTHESIS语句告诉工具,不要优化该信号,在不同的工具中,语句内容,使用方式不同。

在Quartus中,使用/ synthesis noprune /,/ synthesis preserve /等语句,注意,这些语句如果是用于信号的定义时,需要放在定义的语句尾部。如下图所示:

reg [3:0] state /*synthesis preserve*/;

reg [3:0] nxt_state /*synthesis preserve*/;

当然也有别的语句,还有将语句放在module定义尾部,防止模块内任意信号被优化,由于好久没有使用过quartus,怕说错了这部分内容,就不多说了,这些资料可以使用baidu/google/bing搜索“QUARTUS防止信号优化”获得。

在Vivado中,使用(* keep="true" ),( keep_hierarchy="yes" *)语句。这些语句是放在信号定义之前的。

(* keep="true" *)reg [3:0] state ;

(* keep="true" *)(* max_fanout=50 *) reg [12:0] index ;

以及

(* keep_hierarchy="yes" *)

clk_manager

clk_manager_inst(

.clk_in(clk_in),

.rst(rst),

...

);

(* keep="true" )对信号进行保护,但并不是说一定有效。一般遇到加了( keep="true" )还被优化的信号,我会使用( keep_hierarchy="yes" *)对整体模块进行保护,一般到这一步,信号就可以抓取到了。

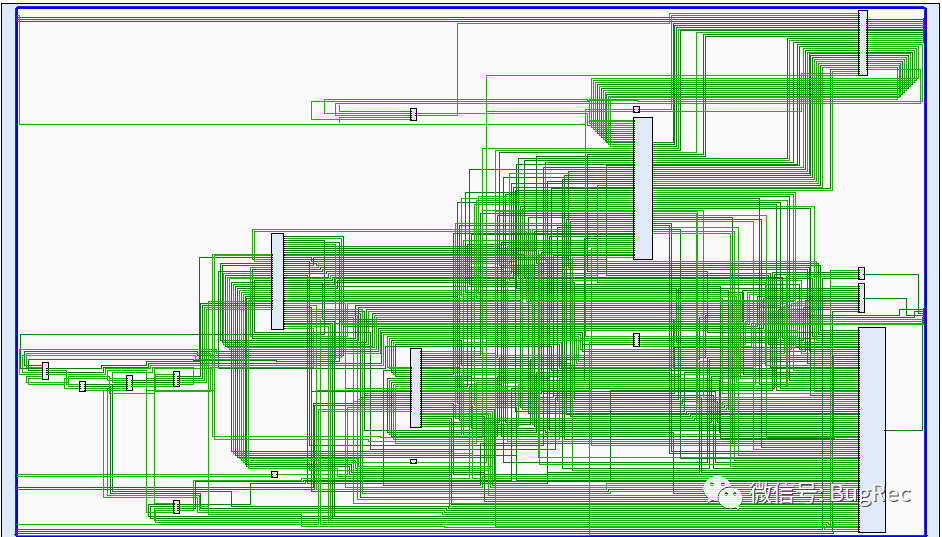

当然,也可以用Schematic,查看具体的实现之后,信号是否还存在。Schematic如下:

当然,最主要还是要提高自己的姿势水平,写出更“规范”的代码,规避工具所想与自己所想有差异。

使用工具版本:

QUARTUS II: 13.1

VIVADO: 2019.1

-

FPGA设计中如何防止信号被优化2023-05-25 5010

-

聊聊寄存器被优化的2种情况2023-09-08 3457

-

FPGA的时序优化高级研修班2013-03-27 4858

-

FPGA实战演练逻辑篇69:基于FPGA的在线系统调试概述2015-09-02 4760

-

HBase性能优化方法总结2018-04-20 1957

-

FPGA芯片_Gowin器件设计优化与分析手册2022-09-29 947

-

今日说“法”:如何防止reg、wire型信号在使用逻辑分析仪时被优化2023-05-16 961

-

chipscope使用教程以及FPGA在线调试的方法2018-03-02 1283

-

利用FPGA工具设置优化FPGA HLS设计2018-12-16 1903

-

FPGA开发在线调试和配置过程2020-11-01 5427

-

如何使用Xilinx的FPGA对高速PCB信号实现优化设计2021-01-13 1139

-

FPGA在线调试的方法简单总结2023-06-19 2695

-

介绍FPGA在线调试的一大利器—VIO2023-06-20 9654

-

浅谈寄存器被优化的原因2023-09-26 2217

-

深度学习的模型优化与调试方法2024-07-01 2511

全部0条评论

快来发表一下你的评论吧 !