介绍FPGA在线调试的一大利器—VIO

可编程逻辑

描述

之前的文章介绍了FPGA在线调试的方法,包括选定抓取信号,防止信号被优化的方法等等。

当存在多种参数的场景时,意味着我们需要多次综合布局布线,这十分浪费时间,虽然只是修改一个数值。

而本文将介绍FPGA在线调试的一大利器,VIO(Xilinx), In-System Memory Content Editor(Altera);使用这个利器,可以节省很多的综合布局布线时间,并且对故障重现等场景有很大的帮助。

在某些场景下,需要多次在线调试测量参数取其中最佳的参数,在这种测试场景下,推荐使用VIO,In-System Memory Content Editor;

以Xilinx的VIO为主要内容介绍:

首先,在Vivado的IP Catalog里找到VIO IP,VIO全称为Virtual Input Output,IP核配置界面如下:

其中Input Probe Count是输入端口的数量,Output Probe Count是输出端口的数量。根据自己的需要去定义。

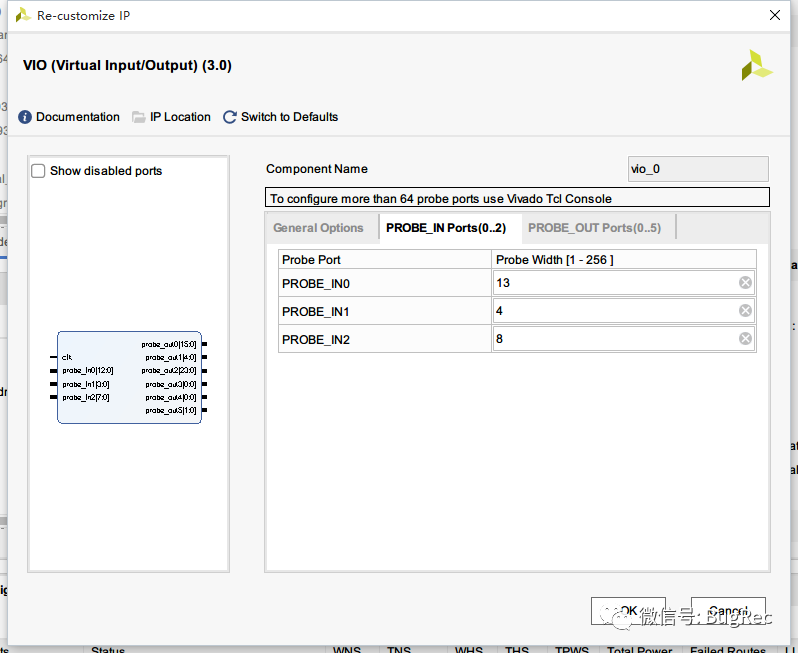

进入PROBE_IN Ports界面设置输入端口的信号位宽,如下图:

进入PROBE_OUT Ports界面设置输出端口的信号位宽,以及输出的初始值如下图

设置完成后,将其例化进项目,与对应的输入和输出信号相连。注意,时钟要与输入输出数据对应上。

等到综合,布局布线,比特流跑完,将bit文件和ltx文件下载进FPGA,Vivado会出现一个dashboard,如下图

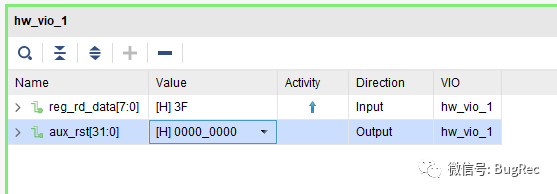

VIO有一个好,就是会显示出信号名称,例如输入端口的信号名是reg_rd_data,输出端口是aux_rst,都显示出来了,此外还包括位宽,Input/Output等信息。

做个简单实验,通过修改Output方向的aux_rst值,使整体FPGA复位,修改完成后如下图:

可以看到,reg_rd_data被复位到0。

然后我们再取消复位,将aux_rst设置为全0状态,如下图:

最近的VIO调试案例中,我们使用VIO去控制SPI模块向某芯片写入和读取数值,以测试芯片的部分功能;使用VIO修改DDS IP的频率控制字,使得DDS IP输出的频率做到实时更改,以此测试后续功能。

此外,除了Xilinx家的工具有这个功能,Altera家的工具也有,如下:

首先,我们需要在Quartus II中例化一个LPM_CONSTANT模块,如下图,设置好常数的位宽及初始值

选中那个复选框,然后给这个Instance ID取个名字,限制为4个字符。

同样在项目中例化这个LPM_CONSTANT,然后经过综合等一系列过程,最后将sof文件下载到FPGA,打开In-System Memory Content Editor,如下图

红框内会出现例化的Instance ID,选中后就可以修改对应的值(手边没有Altera的板子,没办法截完整图)。

由于Vivado的版本比Quartus新,VIO的功能看起来更加强大,不知道新版的Quartus是不是也与时俱进了。

最后,在线修改值的方法会占用FPGA内部的存储资料和触发器资源,请适量使用,不要浪费资源。

-

FPGA调试方式之VIO/ILA的使用2025-06-09 4362

-

Xilinx VIO介绍和应用场景2023-12-11 4265

-

XILINX FPGA Debug with VIO and TCL2012-03-08 5192

-

FPGA实战演练逻辑篇69:基于FPGA的在线系统调试概述2015-09-02 4833

-

玩转Zynq连载5——基于Vivado的在线板级调试概述2019-05-24 3195

-

玩转Zynq连载35——基于Vivado的Virtual IO在线板级调试2019-11-18 3178

-

玩转Zynq连载36——[ex55] 基于VIO在线板级调试的AXI GP总线读写实例2019-11-21 2603

-

GDB调试利器的相关资料分享2021-11-03 1265

-

chipscope使用教程以及FPGA在线调试的方法2018-03-02 1353

-

SMT贴片机在线编程调试的方法与流程介绍2020-03-10 10853

-

FPGA设计与调试教程说明2020-09-22 1189

-

FPGA开发在线调试和配置过程2020-11-01 5721

-

Vivado之VIO原理及应用2021-09-23 11818

-

VIO在chipscope上的使用2022-06-12 3811

-

FPGA在线调试的方法简单总结2023-06-19 2895

全部0条评论

快来发表一下你的评论吧 !