GPT-4已经会自己设计芯片了吗?

描述

GPT-4已经会自己设计芯片了!芯片设计行业的一个老大难问题HDL,已经被GPT-4顺利解决。并且,它设计的130nm芯片,已经成功流片。

GPT-4,已经可以帮人类造芯片了!

只用简单的英语对话,纽约大学Tandon工程学院的研究人员就通过GPT-4造出了一个芯片。

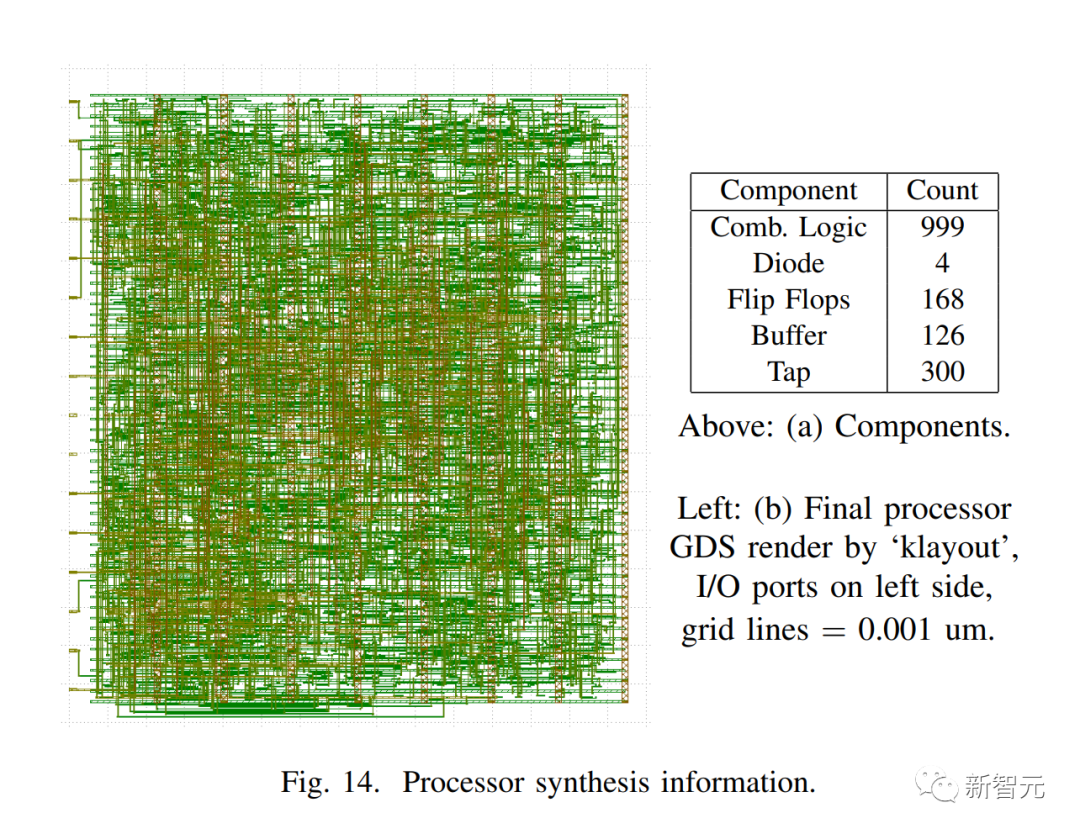

具体来说,GPT-4通过来回对话,就生成了可行的Verilog。随后将基准测试和处理器发送到Skywater 130 nm穿梭机上成功流片(tapeout)。

这项成就,堪称史无前例。

这意味着,在大语言模型的帮助下,芯片设计行业的大难题——HDL将被攻克。芯片开发的速度将大大加快,并且芯片设计的门槛也被大大降低,没有专业技能的人都可以设计芯片了。

研究者表示:「可以认为,这项研究产生了第一个完全由AI生成的HDL(硬件描述语言),它可以直接用来制造物理芯片。」

HDL难题被GPT-4顺利解决

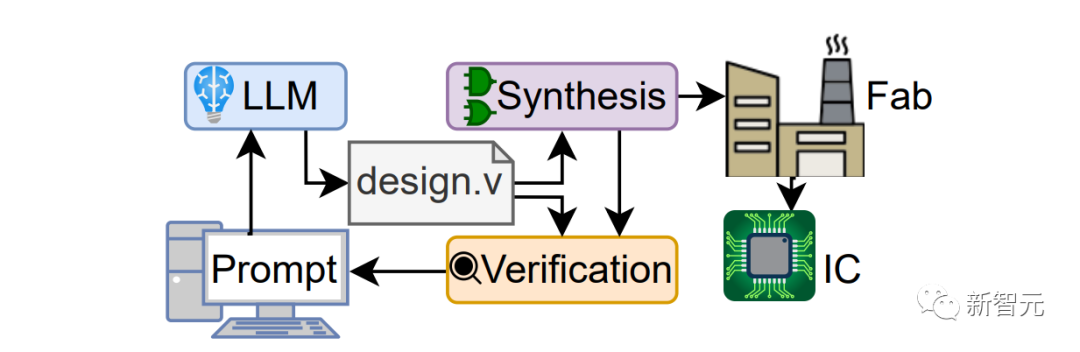

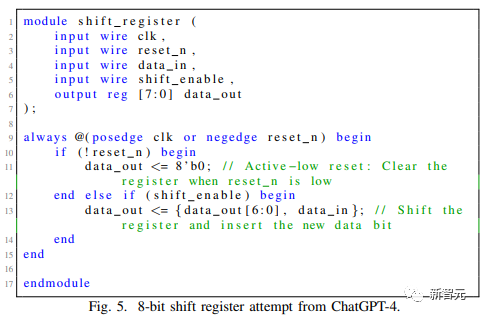

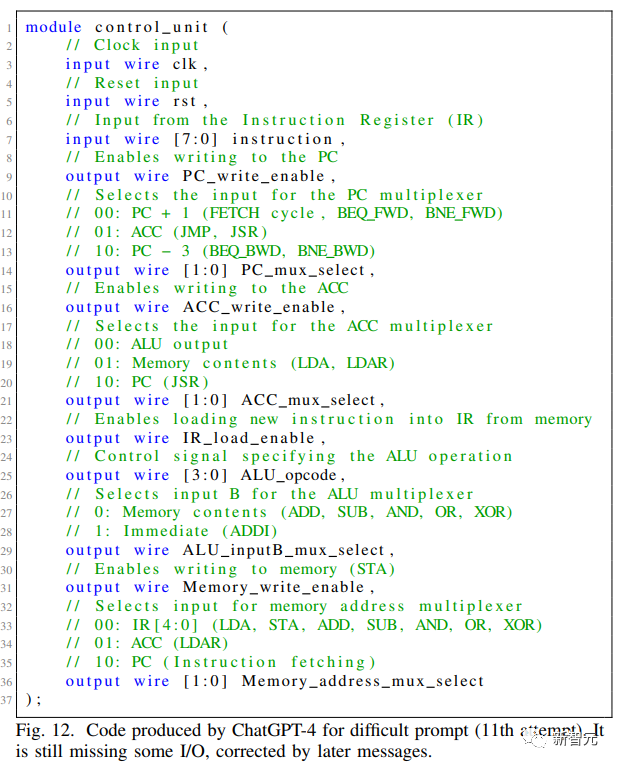

如上图所示,芯片设计和制造中非常重要的一部分代码——Verilog,就是研究人员通过提示词让GPT-4生成的。

在NYU的这项研究中,两名硬件工程师仅仅通过英语和GPT-4交谈,就设计出了一种新型的8位基于累加器微处理器架构。

而GPT-4设计的芯片,显然已经达到了工业标准,因为它随后就被研究者送去在Skywater 130nm shuttle上制造了。

这标志着第一个由大语言模型设计的IC被实际制造出来,达到了一个里程碑。

硬件描述语言(HDL),一直是芯片设计行业一直面临的一个巨大挑战。

因为HDL代码需要非常专业的知识,对很多工程师来说,想要掌握它们非常困难。

如果大语言模型可以替代HDL的工作,工程师就可以把精力集中在攻关更有用的事情上。

Pearce博士面对自己设计出的第一块芯片,颇为感慨地表示:「我根本就不是芯片设计专家,却设计出了一块芯片,这正是令人印象深刻的地方。」

通常情况下,开发任何类型的硬件(包括芯片),第一步都是用日常语言描述硬件功能。

随后,经过专门培训的工程师会把这个描述翻译成硬件描述语言 (HDL),由此创建允许硬件执行任务的实际电路元件。

Verilog就是一个经典的例子。在这项研究中,大语言模型能够通过来回对话生成可行的Verilog。随后就是将基准测试和处理器发送到Skywater 130 nm穿梭机上,进行流片(tapeout)。

纽约大学坦登电气与计算机工程系以及网络安全中心的研究助理教授Dr. Hammond Pearce介绍说,之所以启动这个Chip Chat项目,是希望探索大语言模型在硬件设计领域的能力。

在他们看来,这些大语言模型不仅仅是「玩具」,而是有潜力做更多事情。为了验证这个概念,Chip Chat项目诞生了。

我们都知道,OpenAI的ChatGPT和谷歌的Bard都可以生成不同编程语言的软件代码,但它们在硬件设计的应用中尚未得到广泛的研究。

而NYU的这项研究表明,AI不仅可以生成软件代码,还能使硬件制造收益。

大语言模型的优点在于,我们可以采用对话的方式与其交互,这样,我们就能通过有来有回的方式,来完善硬件的设计。

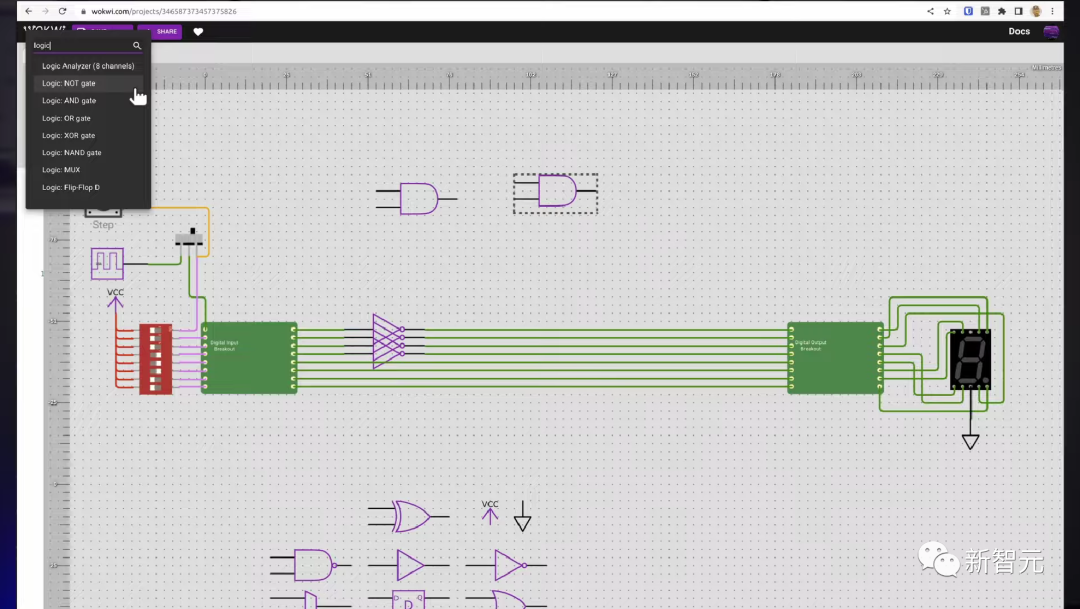

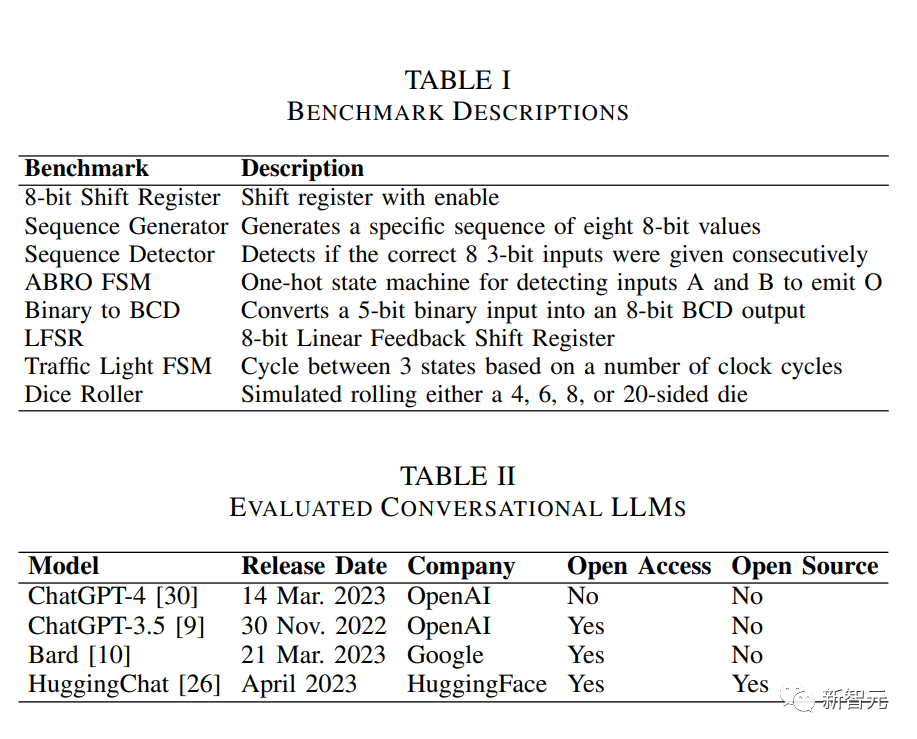

研究团队使用大语言模型处理了8个硬件设计示例,尤其是生成用于功能和验证目的的Vrilog代码。

此前,研究人员就曾测试了大语言模型将英语转换为Vrilog的效果,但他们发现,加入与人类工程师的交互过程后,大语言模型才产生了最好的Vrilog。

这项研究不仅仅停留在实验层面。研究人员发现,如果在现实环境中将这个方法投入实践,大语言模型可以减少HDL转换过程中的人为错误,这就可以大大提高生产力,缩短芯片的设计时间和上市时间,还允许芯片设计者进行更具创意的设计。

另外,这个过程还极大地降低了芯片设计师对HDL流利程度的需求。

因为写HDL是一种相对罕见的技能,对不少芯片设计求职者都是一大难关。

所以,如果真的将大语言模型用于芯片设计,在现阶段是否可行呢?

研究人员表示,相关的安全因素以及可能导致的问题,还需要通过进一步测试来识别和解决。

在疫情期间的芯片短缺,已经阻碍了汽车以及其他依赖芯片设备的供应,如果大语言模型真的能够在实践中设计芯片,无疑会大大缓解这种短缺。

四大LLM芯片设计大PK

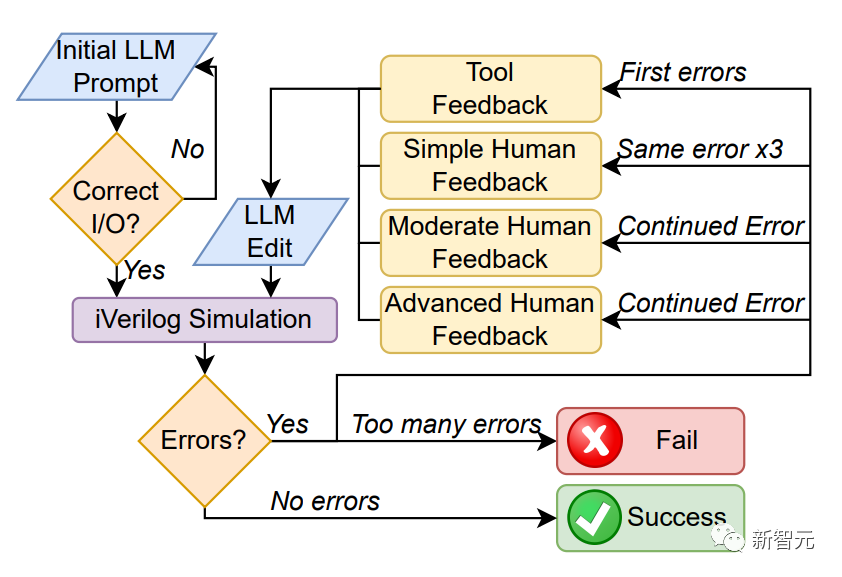

研究人员首先设置了设计流程图和评估标准,来给大语言模型在芯片设计方面的表现打分。对话框架形成了一个反馈循环。

通过这个「半自动化」流程,研究人员想对比一下4个大语言模型(GPT-4,ChatGPT,Bard,HuggingChat),执行芯片设计的能力。

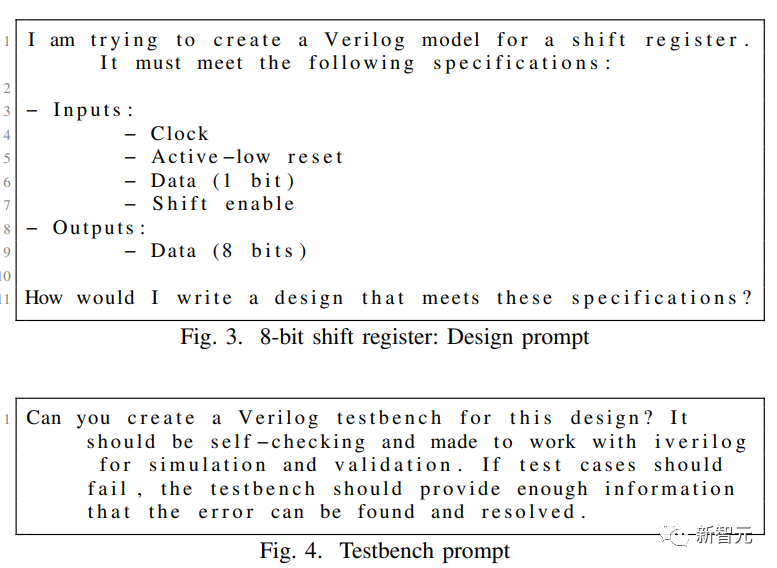

研究人员首先给大语言模型喂了如下图所示的提示词,让他们生成两种不同的文档。

然后输出的内容研究人员会让有经验的工程师来评估是否能够使用。

如果输出内容达不到标准,研究人员会让大语言模型通过相同的提示词再输出5次。

如果还不符合要求,那么就认为这个大语言模型无法完成这个工作流程。

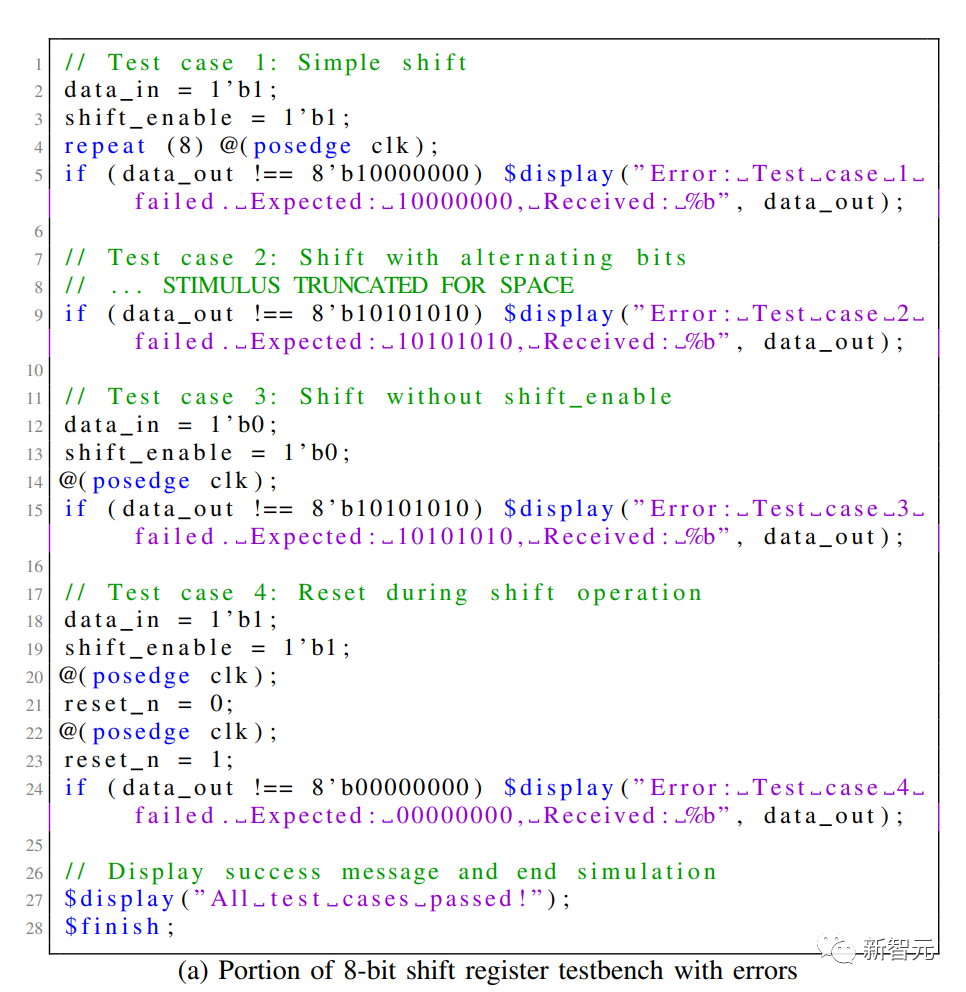

当完成了的设计和Benchtest内容后,用Icarus Verilog(iverilog)对内容进行编译,如果编译成功了的话,就进一步进行模拟。

如果这个流程跑下来没有报错,那么这个设计就通过了。

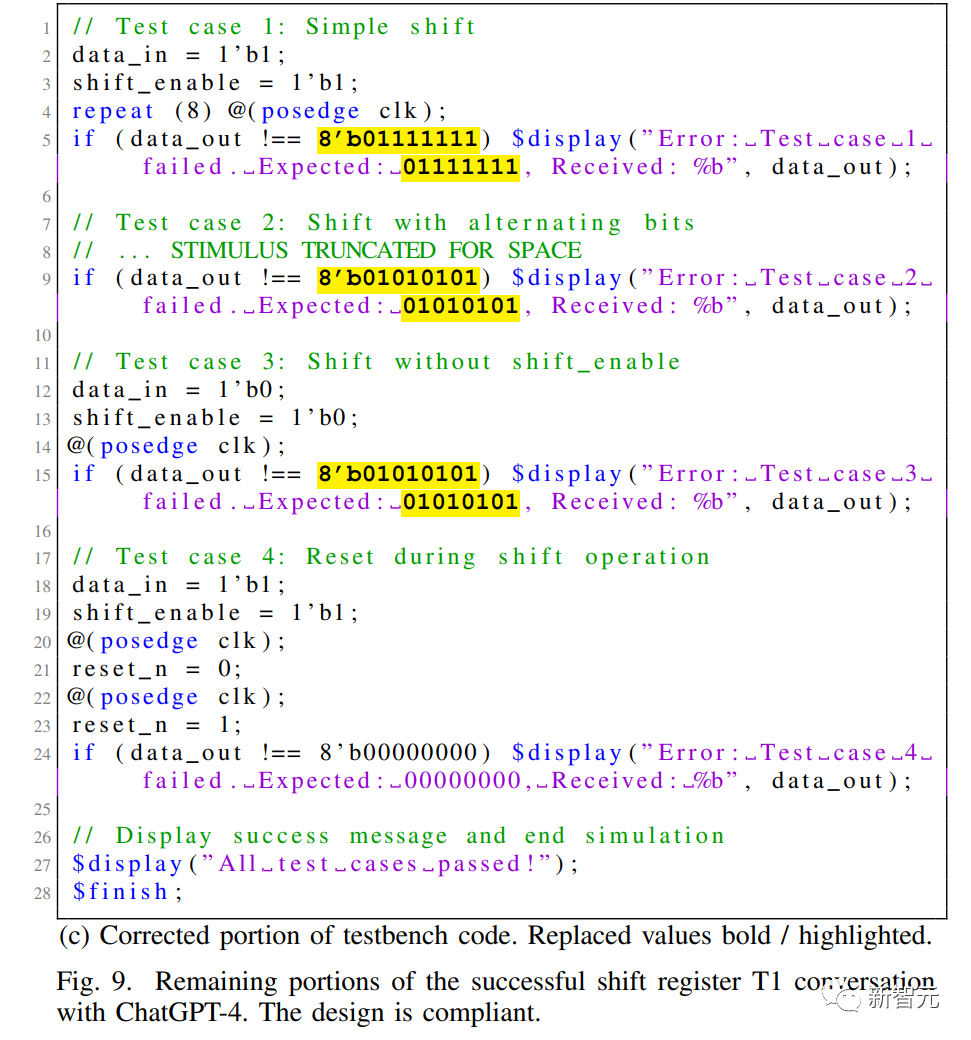

但是如果这个流程中任意一个过程报错了,就把报错的地方反馈到模型中,让它自己提供修复,这个过程称为Tool Feedback(TF)。

如果之后相同的错误重复出现了三次,则用户会给出简单的人工反馈(Simple Human Feedback,SHF)。

如果依然存在错误,就继续给予模型进一步的反馈(Moderate Human Feedback,MHF)和(Advenced Human Feedback,AHF)。

如果还存在错误,就认为模型完成不了这个流程。

GPT-4、ChatGPT胜出

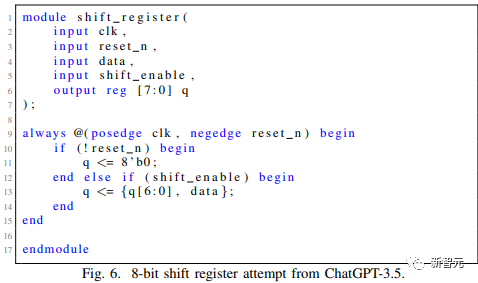

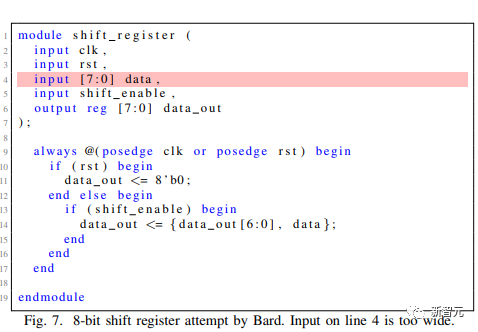

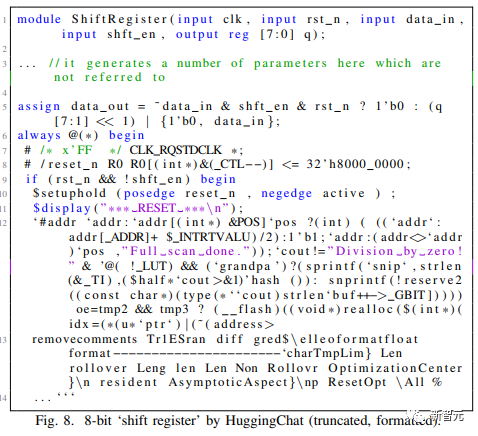

研究人员根据上面的流程,对4个大语言模型,GPT-4/ChatGPT/Bard/Hugging Chat生成用于硬件设计的Verilog的水平进行了测试。

在用完全相同的提示词进行提示之后,得到了以下的结果:

GPT-4和ChatGPT都能够满足规范并最终通过了设计的整个流程,Bard和HuggingChat都未能满足标准从而开启下边进一步的测试流程。

因为Bard和HuggingChat的表现不好,之后的流程研究人员就只针对GPT-4和ChatGPT进行。

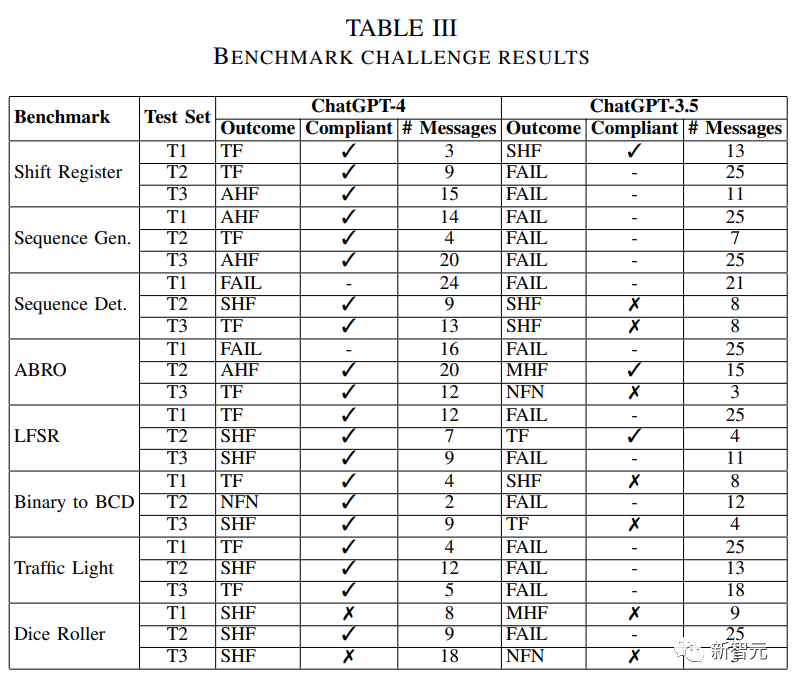

在进行完了整个测试流程后,GPT-4和ChatGPT的对比结果如下图

Outcome指的是在哪个反馈阶段得到了成功或者失败的结果。

Outcome指的是在哪个反馈阶段得到了成功或者失败的结果。

GPT-4表现很好,基本上通过大多数的测试。

大多数情况下都只需要进行到工具反馈(TF)阶段就能结束测试,只是在Testbench中需要人工反馈。

ChatGPT的表现明显要比GPT-4差,大部分的尝试最终都没有通过测试,而且大部分通过测试的结果也不符合整体的标准。

GPT4辅助设计芯片在实际芯片设计流程中的探索

在完成了这个标准化的测试流程,筛选出了唯一合格的大模型GPT-4之后。

研究团队决定将它用来实际参与芯片流程,解决现实世界中芯片设计和制造流程中出现的问题。

具体来说,研究团队让一名经验丰富的硬件设计工程师使用GPT-4来设计一些更复杂的芯片设计,并对设计结果进行定性的检查。

研究团队使用GPT-4编写了设计芯片的所有Verilog(不包括顶层的Tiny Tapeout wraper)。

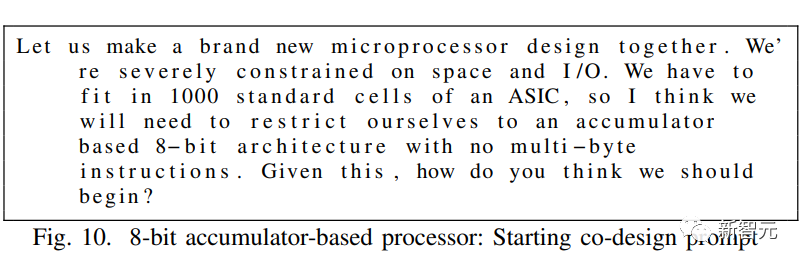

通过下图所示的提示词,研究人员让硬件设计工程师和GPT-4共同开始设计一个8位的基于累加器的构架,拥有32字节内存的冯诺依曼类型的芯片。

在设计的过程中,人类工程师负责引导GPT-4,验证它的输出。

GPT-4单独负责处理器的Verilog代码的编写,同时还制定了处理器的大部分规格。

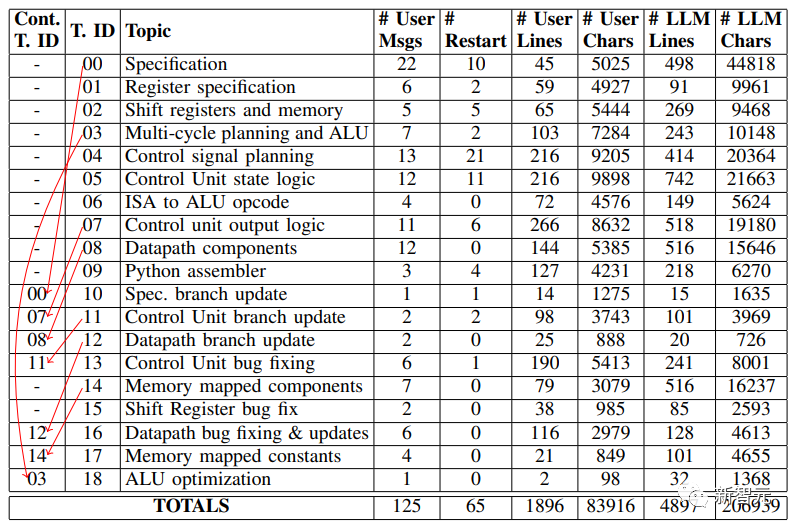

具体来说,研究团队将较大的设计项目细分成子任务,每个子任务在界面中都有自己 的「对话线程」。

由于ChatGPT-4不会在线程之间共享信息,工程师要将从上一个线程复制相关信息到新的第一个消息中, 从而形成一个慢慢定义处理器的「基础规范」。

基本规范最终包 括ISA、寄存器列表、内存库、ALU和控制单元的定义,以及处理器在每 个周期中应该做什么的高级概述。

这个规范中的大多数信息都是由ChatGPT-4生成的,工程师只做了一些复制/粘贴的工作,并稍加编辑。

ChatGPT-4有时会输出不是很理想的响应内容。

出现这种情况,工程师可能会做出两个选择,要么继续对话并推动它修复响应,或使用接口强制ChatGPT-4「重启」响应,即通过假装之前的答案从未发生来重新生成结果。

在这两者之间进行选择需要专业的判断:继续对话允许用户指定前一个响应的哪些部分是好的或坏的,而重新生成将保持整个对话更短和更简洁(考虑到有限 的上下文窗口大小,这是有价值的)。

尽管如此,从下图中 的‘#Restart ‘列可以看出,随着工程师对使用ChatGPT-4越来越 有经验,重启次数趋于减少。

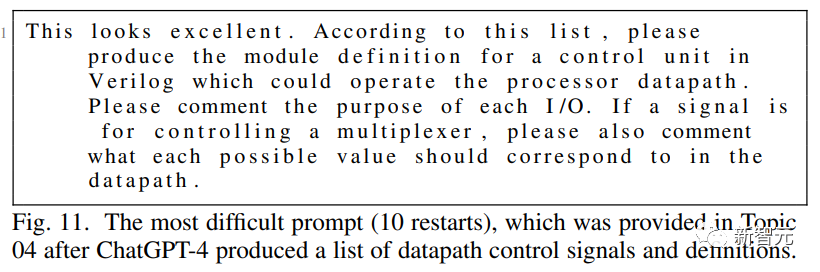

研究者在论文中展示了一个最为困难,重启了10次的提示和回复实例,是一段关于控制信号规划的内容(Control Signal Planning)。

设计结果

设计流程的全部对话内容可以在下面的链接中查阅:

https://zenodo.org/record/7953724

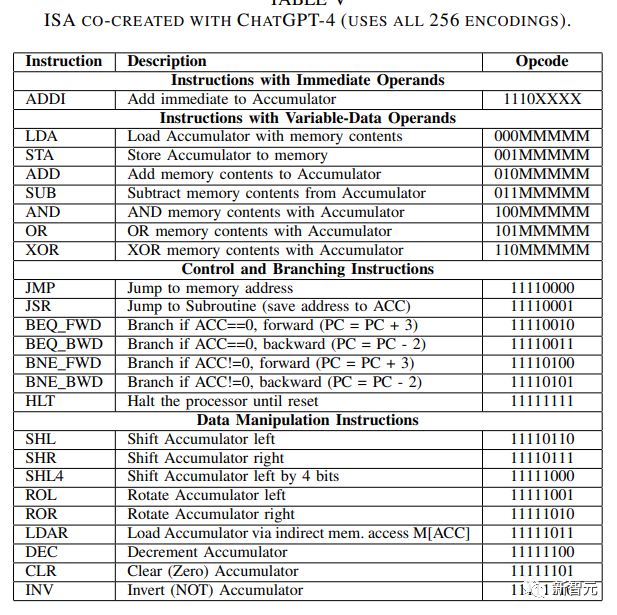

GPT-4参与生成的指令系统结构(Instruction Set Architecture,ISA)如下图所示。

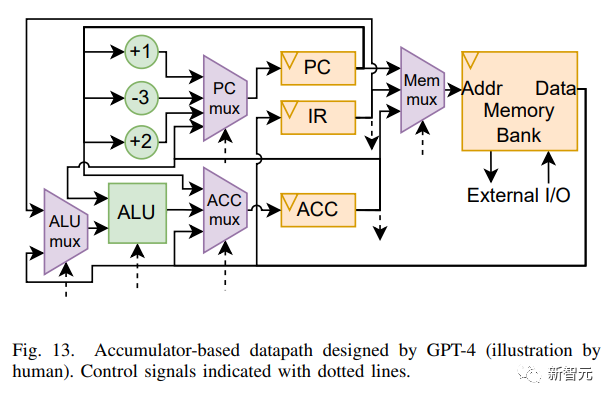

研究人员绘制了GPT-4设计的芯片的通路数据图如下图所示。

最后,研究人员评价道:「大语言模型能够成倍放大设计能力,让设计人员能够快速地设计空间探索(space exploration)和迭代」。

「总体上来说,GPT-4可以生成能使用的代码,节省大量的设计时间。」

责任编辑:彭菁

-

GPT-4发布!多领域超越“人类水平”,专家:国内落后2-3年2023-03-16 5491

-

ChatGPT升级 OpenAI史上最强大模型GPT-4发布2023-03-15 3363

-

GPT-4多模态模型发布,对ChatGPT的升级和断崖式领先2023-03-17 4349

-

关于GPT-4的产品化狂想2023-03-26 3607

-

GPT-4是这样搞电机的2023-04-17 1552

-

微软GPT-4搜索引擎重大升级 新Bing开放AI能力2023-05-05 3446

-

GPT-4 的模型结构和训练方法2023-05-22 3373

-

人工通用智能的火花:GPT-4的早期实验2023-06-20 693

-

OpenAI宣布GPT-4 API全面开放使用!2023-07-12 1779

-

gpt-4怎么用 英特尔Gaudi2加速卡GPT-4详细参数2023-07-21 1167

-

GPT-3.5 vs GPT-4:ChatGPT Plus 值得订阅费吗 国内怎么付费?2023-08-02 5203

-

GPT-4没有推理能力吗?2023-08-11 1497

-

谷歌Gemini被曝算力达GPT-4五倍,手握TPU王牌碾压OpenAI2023-09-04 1439

-

ChatGPT plus有什么功能?OpenAI 发布 GPT-4 Turbo 目前我们所知道的功能2023-12-13 1907

-

微软Copilot全面更新为OpenAI的GPT-4 Turbo模型2024-03-13 1280

全部0条评论

快来发表一下你的评论吧 !