简易FM信号解调的FPGA实现过程讲解

可编程逻辑

描述

FM解调需要去掉载波得到基带的信号,考虑到FM的特殊性,使用参考资料1中的小角度近似解调算法。

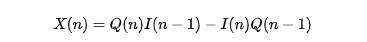

简单来说,FM信号采样后,进行下变频后,传统方法需要对正交分量和同相分量进行反正切及差分运算,这样在FPGA中实现起来相对来说复杂且耗费资源。改进的小角度近似解调法利用了FM的恒包络特性,角度相似原理,得到的解调公式如下:

如此,仅需对信号进行延时,相乘再相减的操作,运算过程简化且使用频率提升,优缺点如下图所示:

最后,解调的整体过程还包括下变频过程,本工程为简化流程,未使用载波恢复进行频偏补偿。整体过程流程图如下:

下变频

使用NCO IP核,设置好对应中心频率的频率控制字即可,如下图,NCO输出预设频率的正弦波信号,NCO的设置可见参考资料2及上篇文章。

将采样信号分为两路,分别与cos,sin信号相乘,如下图,乘法器的IP核需要注意数据类型,需要选择为有符号数,最好使用流水线结构,其它的如数据位宽根据实际需求设置:

时域混频对应频域频谱搬移,需要使用滤波器滤除高频分量。滤波器的参数设置见参考资料3,设置好对应的采样频率,截止频率,滤波器系数位宽和输入位宽参数即可。如下图,信号通过滤波器:

至此,下变频过程结束。

小角度近似解调

使用D触发器将下变频后的信号延迟一个时钟周期,按照上述提到的公式,进行对应的乘法,最后做减法即可。

这块没什么可说的,基本上就是照着公式调用乘法/减法IP核,设置好对应参数,可能需要截位,截位见参考资料4。

整体结构搭建起来并不复杂,实际出来的信号效果还需要使用Signaltap II进行板上验证,并调整滤波器参数和截位得到最好的效果。

最终得到的效果如下:

第二个是原始基带信号,最后一个就是解调的信号,可以看到还是有部分载波信号在,这是因为我们所使用的FPGA芯片l里的资源比较少,滤波器的阶数和系数位宽不能设置过大,省资源导致的,其次下变频的本振信号与信号载波之间可能存在频偏,未进行补偿操作。

FPGA型号:Altera Cyclone EP4CE10F17C8

-

简易FM信号调制的FPGA实现过程讲解2023-06-20 3286

-

简易AM信号调制的FPGA实现过程简单讲解2023-06-06 2445

-

软件无线电中调制解调的实现AM-FM讲解2021-04-28 1533

-

如何写一个简易AM信号的FPGA实现?2021-03-29 3029

-

多种调制信号的解调的实现过程2019-04-12 4339

-

以FPGA为基础的激光陀螺信号解调系统设计过程详解2018-07-17 3446

-

基于FPGA的DSTFT算法对FSK信号解调的改进2017-11-15 1182

-

FM调制/解调电路的设计方案分析2017-10-27 4383

-

QPSK调制解调2016-12-12 1210

-

频率信号解调(FM信号解调)2015-10-12 6839

-

FM解调器电路原理解析2015-01-30 11559

-

(新手求解答)如何用labview仿真解调FM信号?2013-04-22 7228

-

FM信号的解调电路--斜率鉴频器2010-05-27 25642

全部0条评论

快来发表一下你的评论吧 !