从锁存器角度看亚稳态发生的原因及方案简单分析

电子说

描述

发生亚稳态的原因是信号在传输的过程中不能满足触发器的建立时间和保持时间。发生亚稳态时,触发器的输出是个中间态,也是x态,不能确定为0或1,而且这个亚稳态还会往后传递至更多的组合逻辑和时序逻辑电路。

所谓建立时间,就是在clk有效边沿到来之前输入信号需要保持稳定的最小时间;所谓保持时间,就是在clk有效边沿到来之后输入信号还需要保持稳定的最小时间。

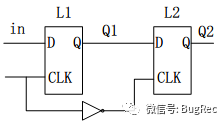

为了简便分析,将一个触发器的结构简化为下图:

一个触发器等效为两个触发电平不一样的锁存器的信号链;锁存器的特性为:

- 当clk为有效电平时,锁存器是透传模式,Q随着D的变化而变化;

- 当clk为无效电平时,锁存器在锁存模式,Q为之前保存的值,D输入值不会对Q有影响。

所以,如上图,当clk为低电平的时候, L1为透明传输模式,输入信号in透传至Q1,但是L2是锁存模式,Q2并不会受到Q1的影响;

而当clk翻转至高电平时,L1将会进入锁存模式,这个过程需要一段时间完成。L2会进入透传模式,而此时L1可能还处于透传模式。那么在clk翻转之前的一段时间到L1完成进入锁存,L2进入透传模式这段时间内,输入信号in都是不可以变化的,否则可能导致Q1传导中间值,进而Q2也传输x态,也就是所谓的亚稳态。

图来自百度百科

再探讨一些异步信号同步的方法原理。对于单bit信号来说,我们都知道一般用两个DFF触发器来做同步,当然这不是一定的,具体几个DFF需要根据两个时钟域的频率做计算。但本文分析以两个DFF触发器为例。

值得一提的是,多个DFF触发器解决异步信号同步的亚稳态方案,并不能完全地消除亚稳态,只是极大地降低了亚稳态发生的概率。有一个MTBF的平均无故障时间公式计算,公式跟芯片工艺的PVT,接收数据时钟频率,接收数据的翻转率有关。如果我们的MTBF时间大于产品的保质期,可以视为没问题(保修期的作用之一)

图来自百度百科

那么,为什么加两个触发器就能降低亚稳态的概率呢?从电路上分析来说,虽然触发器的输出是中间值,但是现实世界中是存在噪声的,那么一定会导致信号会偏向某个固定值0或1。但这个过程是需要一定时间的,所以通过加两级触发器,让这个趋向确定值的过程在触发器传递过程中完成,那么最后触发器的输出就是一个确定值了。

当然,也会发生某些情况下,这个趋向确定值的过程会很漫长,所以说只能降低发生的概率而不能消除。

那么对于多bit信号的同步呢,在我看来,方案是让把多bit信号转换为单bit信号同步(格雷码),或者让多bit信号保持稳定,只要能够保证在接收数据时钟域内,信号一直稳定不变,就不会产生亚稳态。大家可以想想诸如FIFO,D-MUX,握手等方法是不是等待多bit信号稳定后再去采样。

-

亚稳态的分析与处理2023-06-21 5417

-

什么是亚稳态?如何克服亚稳态?2023-05-18 6246

-

今日说“法”:让FPGA设计中的亚稳态“无处可逃”2023-04-27 885

-

关于FPGA设计的同步信号和亚稳态的分析2022-10-18 2395

-

亚稳态产生原因、危害及消除方法2022-09-07 11681

-

FPGA--中复位电路产生亚稳态的原因2020-10-22 2073

-

在FPGA复位电路中产生亚稳态的原因2020-10-19 1730

-

关于FPGA设计中的亚稳态及其缓解措施的分析和介绍2019-10-06 1841

-

FPGA触发器的亚稳态认识2012-12-04 4709

-

FPGA中亚稳态——让你无处可逃2012-01-11 4658

-

一种消除异步电路亚稳态的逻辑控制方法2011-10-01 1194

-

利用IDDR简化亚稳态方案2010-12-29 3617

全部0条评论

快来发表一下你的评论吧 !