时序逻辑电路之时钟分频设计

可编程逻辑

描述

和单片机一样,FPGA开发板上也都会配有晶振用来生成板载时钟。前一篇我们提到了小脚丫的固定板载时钟频率为12MHz,这个频率实际上就是作为我们的时间参考基准。正如歌里唱的那样:

嘀嗒嘀嗒嘀嗒嘀嗒

时针它不停在转动

因此,小脚丫只要在通电之后,它的内部时钟就会每隔83.8ns滴答一次。这个时间真的很快,连光速还没来得及跑出小区大门就被掐断了。那么问题来了:如果在某些应用场合中,我们不需要这么快的嘀嗒该怎么办?比如,我们想让小脚丫上的LED灯以可观察的频率闪烁,如1Hz,也就是1秒闪一下。

相信大家和我的想法一样,就一个字:等。既然一秒钟可以嘀嗒一千两百万次,那我们每次点亮LED之前就先等你跳一千两百万次好了,毕竟也不耗油。换句话说,就是把内部时钟频率放慢12,000,000倍。这个操作就叫做时钟分频,也就是我们今天要掌握的内容。

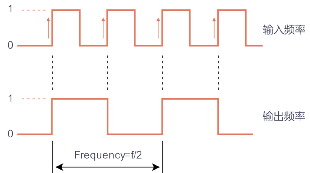

先说偶数分频,也就是说将内部时钟放慢的除数为偶数。在这里,我们只考虑占空比为50%的波形(高电平和低电平对半分)。图1中,我们设定内部时钟为我们的输入频率,也就是12MHz,那么如果想获得一个6MHz的输出频率,只需要等第二次上沿信号即可,因此分频除数为2。

图1

如果想得到更低的输出频率,比如1MHz,则除数调整12;如果1KHz,除数调成12000,依次类推。 注意,这种方法只对除数为偶数的情况下才管用! 以下是生成1Hz输出的代码,于是我们将除数调成了12,000,000。

module clkdivider(clock_in,clock_out);

input clock_in;

output reg clock_out;

reg[23:0] counter=24'd0;

parameter DIVISOR = 24'd12000000;

always @(posedge clock_in)

begin

counter <= counter + 24'd1;

if(counter >= (DIVISOR-1))

counter <= 24'

clock_out <= (counter< DIVISOR/2)?1'b1:1'b0; //条件赋值

end

endmodule

在代码中我们注意到了这一行代码:

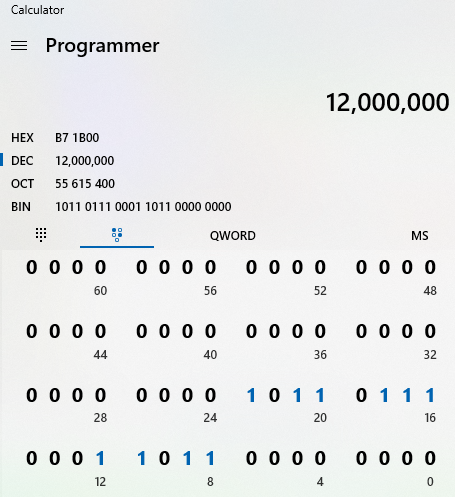

reg[23:0] counter=24’0

这个实际上就是用于存储小脚丫固定时钟频率的一个数据格式,至于为什么是24位宽直接参考图2就可以。打开你们电脑里的计算器,调成码农模式即可。

图2

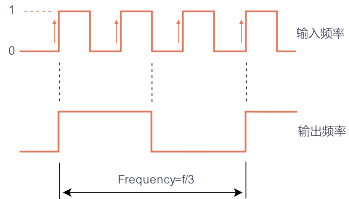

再说奇数分频。比如说我们想获得一个4MHz的频率,按道理说我们把分频除数调成3即可。而实际上奇数分频的故事还是稍微多一点。我们看一下图3就明白了。

图3

不难发现,当除数为奇数时,此刻对应的时间为内部时钟的下沿,如果仅靠上沿触发的话,此时输出是不会改变的。所以奇数分频需要经历上沿触发和下沿触发才能完成。还好,在Verilog里,我们先不用研究边沿触发的构造原理,只需要通过行为级描述即可直接完成指令:

always @(posedge clk) //上沿触发

always @(negedge clk) //下沿触发

现在我们来看一个分频倍数为3的例子。图3中,不论输出信号是高电平还是低电平,都只涵盖了两个边沿信号,也就是说,不论是上沿还是下沿时钟,我们只需要分别等待2次触发后进行赋值即可。

module clk_div3(clk, clk_out);

input clk;

output clk_out;

reg [1:0] pos_count, neg_count;

wire [1:0] r_nxt;

always @(posedge clk) //处理上沿时钟触发部分

if (pos_count ==2) //等待输入时钟上沿触发2次

pos_count <= 0;

else

pos_count <= pos_count +1;

always @(negedge clk) //处理下沿时钟触发部分

if (neg_count ==2) //等待输入时钟下沿触发2次

neg_count <= 0;

else

neg_count <= neg_count +1;

assign clk_out = ((pos_count == 2) | (neg_count == 2)); //每等待2次触发后进行赋值

endmodule

了解了3倍分频之后,如何实现通用的奇数分频自然也就不在话下了,这一部分就交给愿意动手尝试的朋友们去自行练习了。

最后,我们的任务是,让小脚丫上的L1-L4这四个灯以2Hz的频率闪烁,另外四个灯L5-L8分别以1Hz的频率闪烁,看看能否实现呢?

-

时序逻辑电路有记忆功能吗2024-08-29 2874

-

什么是组合逻辑电路和时序逻辑电路?它们之间的区别是什么2024-03-26 7067

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 14378

-

组合逻辑电路和时序逻辑电路的区别和联系2023-03-14 9227

-

模拟电路教程之时序逻辑电路的课件资料免费下载2020-06-22 1190

-

什么是时序逻辑电路2019-02-26 33193

-

数字电路教程之时序逻辑电路课件的详细资料免费下载2018-12-28 1403

-

数字电路基础教程之时序逻辑电路的详细资料概述2018-10-17 1725

-

时序逻辑电路由什么组成_时序逻辑电路特点是什么2018-03-01 112362

-

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别2018-01-30 95127

-

时序逻辑电路的分析与设计2016-09-02 1224

-

时序逻辑电路2010-08-10 951

-

同步时序逻辑电路2009-09-01 1139

全部0条评论

快来发表一下你的评论吧 !