芯片设计进阶之路—从CMOS到建立时间和保持时间

EDA/IC设计

描述

建立时间(setup time)和保持时间(hold time)是时序分析中最重要的概念之一,深入理解建立时间和保持时间是进行时序分析的基础。

在介绍建立时间和保持时间之前,我们从CMOS电路开始。

1. CMOS晶体管简介

金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。由MOS管构成的集成电路称为MOS集成电路,而由PMOS管和NMOS管共同构成的互补型MOS集成电路即为 CMOS-IC( Complementary MOS Integrated Circuit)

MOS管就相当于一个开关,如下图所示。

所以,NMOS需要输入高电压(逻辑1)才能导通,PMOS需要输入低电压(逻辑0)才能导通。可以认为NMOS是“正开关”,PMOS是“反开关”。

现在的工艺中,主要使用的就是CMOS工艺,就是把PMOS和NMOS这两类晶体管构成一个单元,称为CMOS单元或者反相器单元。

所以很多文章都在分析CMOS反相器,是因为CMOS反相器就是CMOS电路的基本单元,或者说可以看作最小单元。

所以从CMOS反相器开始。

1.1 CMOS 反相器

反相器就算输入位1,输出位0;输入为0,输出为1. 实际的反相器没有这么理想。

CMOS 反相器电路如下:

当左边vI=0V时,vGND=0V,VTN截止,∣vGSP∣=VDD ,VTP导通,vO≈VDD,门电路输出输出高电平;在这个过程中,从VDD到接地GND这一个供电回路都没有导通,因此理论上不存在电流从VDD流到GND,因此功耗为0.

当左边vI=VDD时,VGND=VDD ,VTN导通,NMOS打开,∣VGSP∣=0V,VTP截止,PMOS关闭,vO≈0V,门电路输出低电平,但是从VDD到接地GND这一个供电回路也没有导通,因此理论上也不存在电流从VDD流到GND,因此功耗也为0。

如果将0V定义为逻辑0,VDD定义为逻辑1,将实现逻辑“非”功能。

所以理论上,CMOS进行传输的时候是没有功耗的,但是实际情况肯定不可能没有功耗,但是功耗会很小。所以在低功耗如此重要的今天,为什么CMOS能称为主流就不奇怪了。

2. CMOS逻辑电路

2.1 CMOS 门电路

CMOS反相器就是一个非门,由非门可以组成与非门和或非门。

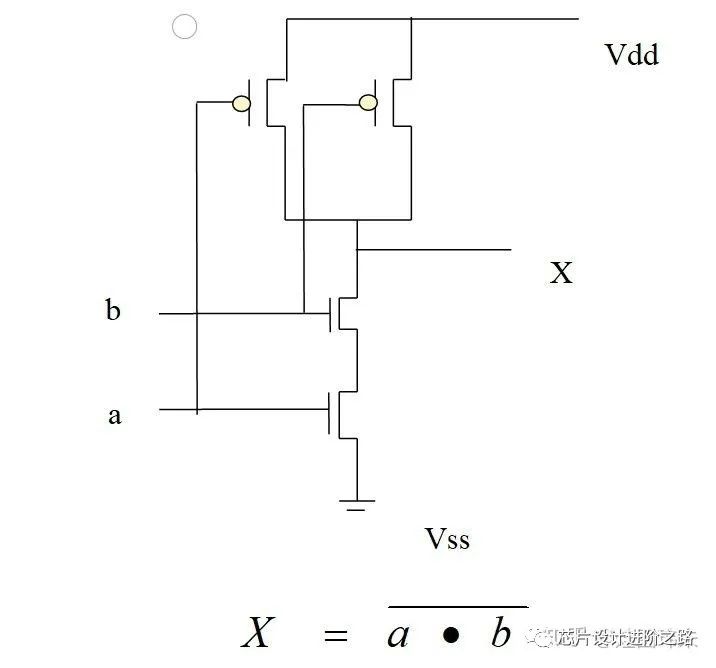

- CMOS与非门(NAND)

CMOS 与非门电路及行为如下面图所示:

- a = 0, b=0时,上面并联的PMOS导通,下面串联的NMOS截止,输出X=Vdd=1;

- a = 0, b=1时,上面并联的PMOS导通,下面串联的NMOS截止,输出X=Vdd=1;

- a = 1, b=0时,上面并联的PMOS导通,下面串联的NMOS截止,输出X=Vdd=1;

- a = 1, b=1时,上面并联的PMOS截止,下面串联的NMOS截止,输出X=Vdd=0;

可见,这个电路实现了与非功能。

- CMOS或非门(NOR)

CMOS 或非门电路及行为如下面图所示:

- a = 0, b=0时,上面串联的PMOS导通,下面并联的NMOS截止,输出X=Vdd=1;

- a = 0, b=1时,上面串联的PMOS截止,下面并联的NMOS导通,输出X=Vdd=0;

- a = 1, b=0时,上面串联的PMOS截止,下面并联的NMOS导通,输出X=Vdd=0;

- a = 1, b=1时,上面串联的PMOS截止,下面并联的NMOS导通,输出X=Vdd=0;

可见,这个电路实现了或非功能。

2.2 双稳态器件

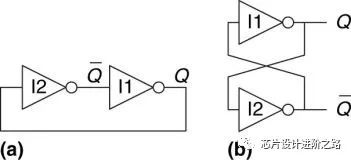

双稳态器件是指稳定状态有两种,一种是0,一种是1的器件;双稳态器件是存储器件的基本模块,双稳器件的的一种电路结构是:交叉耦合反相器 结构,如下图所示:

连个反相器连在一起,这就构成了一个双稳态器件,为什么是双稳态呢?我们现在就来分析一下:

由于没有输入,于是我们就假设I1的输出先为1,即Q=1;那么I2的输入为1,Q’就为0,于是反馈给Q的输入,导致Q的输出为1,也就是使得Q的状态稳定为1,因此这个器件有一个稳定的状态为1.如下图所示:

我们再假设I1的输出先为0,即Q=0;那么I2的输入为0,Q’就为1,于是反馈给Q的输入,导致Q的输出为0,也就是使得Q的状态稳定为0,因此这个器件还有一个稳定的状态为0.如下图所示:

由此可见,这种交叉耦合反相器的器件是双稳态器件。但是需要注意的是,电路有可能存在第三种状态,也就是前面文章介绍过的亚稳态。

为什么介绍双稳态器件呢?那是因为锁存器、寄存器都是双稳态器件,它们都有两个稳定状态1和0。正是因为它们有两个稳定的状态,因此才可以拿它们来存储数据,也就是说双稳态电路(比如交叉耦合反相器、锁存器和寄存器)可以存储数据。

下面我们来看一下锁存器和触发器。

2.3 锁存器(latch)

很显然,上面的那种交叉耦合反相器没有输入,是存储不了输入的数据的了,因此就需要有输入的类似“交叉耦合反相器”结构的双稳态电路,这就是锁存器。

锁存器:不需要触发信号,由输入信号直接完成置0或置1操作。

最常见最基本的锁存器是SR锁存器,常用的锁存器是D锁存器。这里只介绍RS触发器和D触发器。

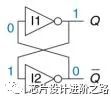

2.3.1 SR锁存器

SR(Set-Reset)锁存器,也叫基本RS触发器是各种触发器构成的基本部件,也是最简单的一种触发器。SR锁存器电路结构和符号如下图所示:

这里用的或非门搭建的SR锁存器,同样也可以用与非门搭建SR锁存器,只需要把或非门换成与非门就可以了。

工作原理:

S端是置位端,S=1的时候把输出Q置为1;

R端是复位端,R=1的时候把输出Q复位成0;

当S=0, R=0的时候,输出Q的值就保持前一个状态的值,也就是把原理的状态锁存了。

当S=1, R=1的时候,根据与非门的特性,Q=0, Q=0, 这样Q=Q;不符合输出Q`=~Q的逻辑。所以S=1, R=1是不允许的状态。这也是SR锁存器的一个限制。

工程中,为了解除这个限制,一般都是把一个信号A接到S端同时把A通过一个反相器(非门)输入到R端,这样S,R就不可能同时为1了。

虽然SR锁存器电路简单,但是在应用中有两个缺点:

- S,R不能同时为1;不够方便;

- 锁存的时间点不清楚,任何时刻,输入都能直接改变输出的状态。也就是不知道什么时候锁存了什么数据,没有一个参考的时刻来确切的知道电路的状态。

下面我们分析一下SR锁存器的传输延时:

假设SR锁存器的初始状态是Q=0, Q`=1,与非门的传输延时是tpd。输入信号波形如下图所示:

- S的下降沿到达后,经过G1的传输延迟时间tpd,Q端变为高电平;

- Q端高电平加到门G2的输入端,再经过门G2的传输延迟时间tpd, 使Q`变为低电平;

- 当Q`的低电平反馈到G1的输入端以后,即使S=0变成S=1,触发器被置成q=1状态也将保持下去。

可见,为保证触发器可靠地翻转,必须等到Q`=0的状态反馈到G1的输入端以后,S=0的信号才可以取消。

因此,S输入的低电平信号宽度tw应满足tw≥2tpd。

同理,如果从R端输入置0信号,其宽度也必须大于、等于2tpd。

可见,如果S,R端输入的信号宽度很小,比如毛刺,那么输出是不会改变的。SR锁存器的结构,在门控时钟切换防毛刺中很有用,后面会写一篇文章专门讲一下这个电路。

2.3.2 D 锁存器

为了解决SR锁存器的缺点,改进的结构就是D锁存器。

D锁存器最大的特点是,引入了一个特殊信号——时钟信号。

注意:时钟信号首先是一个信号,它只是一个特殊的信号,由于它的特殊性和重要性,所以他才有了一个名字叫做时钟信号, 同样的还有复位信号。在分析时钟的时候,请不要忘记,时钟信号首先是一个信号。

引入时钟信号的作用是,作为参考和同步。因为时钟是一个特殊的,高低电平循环的信号,它的行为是确定的, 而且送给不同电路的时钟信号是同一个。所以就能以它作为参考。

比如,引入时钟信号后,D锁存器就只能在时钟有效的时候,S和R才能起作用,也就是给SR加了一个前提条件,这样对照周期性的时钟信号,就能明确知道锁存的时间点了。

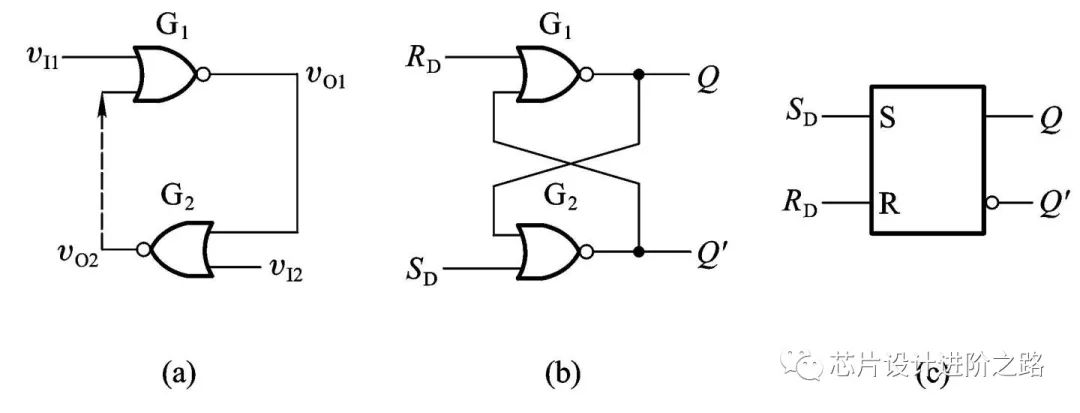

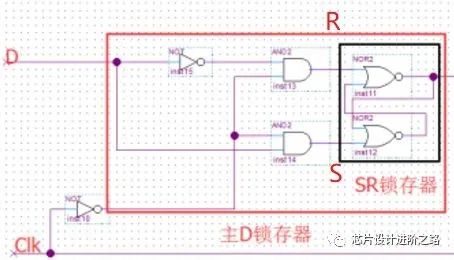

D锁存器常见结构和电路符号图如下所示:

可以看到,D锁存器可以分为前级门电路(两个与门和一个非门)和后级SR锁存器组成。

下面我们就来分析一下它的功能:

输入是Clk和D,也就是输入有四种可能:

·当clk=0时,红S红R都为0,也就是SR锁存器的输入为00,根据SR锁存器的功能,输出Q和Q’将保持原来的状态;因此clk=0时,不管D是什么,输出Q和Q’都不随D变化,只与原来的状态有关,也就是保持。

·当clk=1时,R=(1·D’)=D’;S=(1·D)=D。

也就是说,当clk=1的时候,SR锁存的输入是互补的,不会出现S和R同时有效的情况。当D=1时,S=1,置位有效,输出Q=1;当D=0时,R=1,复位有效,输出Q=0;因此就可以知道,在clk=1时,输出Q=D,也就是输出等于输入。

通过上面的分析,上面的D锁存器结构功能为:在clk=1时,数据通过D锁存器流到了Q;在Clk=0时,Q保持原来的值不变。这样的锁存器也称为透明锁存器或者电平敏感锁存器。

注意:这里说的电平敏感是指时钟电平为1的时候,输入才能引起输出变化。

2.4 触发器(Flip-Flop)

虽然锁存器结构简单面积小,速度快,但是锁存器是电平敏感的,在时钟为高的时候,输入信号的任何改变都会随时引起输出的改变,一个时钟高电平期间可能会有多次改变。而且受布线延迟影响较大,很难保证输出没有毛刺产生。

为了改进这个缺点,就发明了边沿触发器,边沿触发器最大的特点是边沿敏感的,也就是仅取决于CLK的下降沿(或上升沿)到来时的输入信号状态,与在此前、后输入的状态没有关系。这样就提高可靠性,增强抗干扰能力。

最常见最简单的触发器就是D触发器。

2.4.1 D 触发器

D触发器的结构和电路符号图如下所示:

D触发器可以由两个D锁存器构成,驱动时钟的相位相反,前面的D锁存器称为主锁存器,后面的D锁存器称为从锁存器,因此D触发器也可以称为主从触发器。

下面我们分析一下D触发的功能(注意主锁存器的时钟是clock取反):

假设要传输的数据D=D1:

在时钟clk=0的时候,主锁存打开进行传输数据,把输入传送到从到从锁存器的输入端,即Qm = D1。然后clk从0→1的时候,主锁存器准备关闭,保持原来的值D1,与此同时从锁存器准备打开,把Qm的值传输到输出Qs,也就是Qs=Qm=D1。

在clk=1的时候,主锁存器是关闭的,Qm保持D1不变,即Qm=D1;从锁存器是打开的,Qs=Qm=D1。接着clk从1→0的时候,主锁存器准备打开,准备传输数据;而从锁存器准备关闭。在clk=0的时候,主锁存打开进行传输数据,把输入传送到从到从锁存器的输入端,即Qm *= D2;与此同时,从锁存器关闭,由于新的Qm即Qm*还没有到达从锁存器的D端,因此在从锁存器关闭的时候,从锁存器锁存的是原来的值即D1,因此输出Qs =D1。然后接下来上升沿就传输D2....

从上面的分析可以找到,D触发器在时钟上升沿的时候锁存在时钟上升沿采到的值,并且保持一个时钟周期。这种在时钟上升沿锁存数据的触发器称为正边沿触发器,与此对应的还有负边沿触发的触发器,这里就不进行介绍了。

由D触发器延伸出去的知识点还有很多,比如寄存器:

寄存器(Register)由多个D触发器构成(一个D触发器可以看做1位的寄存器);寄存器可以看成是多位的DFF。

比如带使能的触发器:

再比如带复位的触发器:

3. 建立时间和保持时间

3.1 建立时间和保持时间的定义

下面我们通过分析D触发器来理解建立时间和保持时间。

如果想深入理解一个概念,那么我们一定要知道这个概念的清晰的定义。

建立时间和保持时间都是针对触发器的特性说的,比如对于一个D触发器:

时序图如下:

建立时间(Tsu:set up time):

是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间。如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

保持时间(Th:hold time):

是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间。如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。

建立时间和保持时间其实就是数据在时钟上升沿前后的一个时间窗口内必须保持稳定,不然数据就不能正确的存到触发器。

3.2 为什么需要建立时间和保持时间

那么为什么会有建立时间和保持时间的要求呢?

D触发器的门级电路如下:

我们知道D触发器是在(上升)边沿进行锁存数据的,也就是clk从在0→1的时候锁存数据,那我们就看看这个上升沿的时候发生了什么:

假设原来的数据是1(也就是从锁存器锁存的数据是1),然后我们要锁存的数据是0。

要让D端的输入0在Q端输出,那么需要主锁存器稳定的锁定输入的0,而从锁存器则负责传输主锁存器锁存的数据。所以我们重点分析主锁存器。

为了简化分析假设反相器,与门,或非门这些门的延时都是tpd, 我们分析SR锁存器的输入端。假设输入D从0->1相对于CLK上升沿的延时是tdd, 那么输入端S的波形如下:

可以看到,CLK取反有tpd的延时,S端输入相对于D端也有tpd的延时。这样S=~Clk & D后第一个脉冲的宽度就是tw=tdd。

同样分析R端也可以得到相同的结论。

也就是说,输入数据D在时钟上升沿到来之前稳定的时间就表现为SR锁存器的S/R端信号的脉冲宽度。

参考2.3.1的分析,SR锁存器对输入信号的脉冲宽度是有要求的。

S输入的低电平信号宽度tw应满足tw≥2tpd

所以,我们可以得到tw=tdd≥2tpd.

也就是说,数据在时钟上升沿到来之前,稳定时间必须要不小于2tpd(tpd为门电路延时), 才能被正确的采样到。

这就是建立时间:Tsu ≥2tpd

同样的分析,我们可以得到保持时间: Th≥2tpd

所以,我们的结论就是,由于门电路的延时和触发器的电路结构,建立时间和保持时间是一定存在的,否则就不能满足触发器的功能要求。

4. 后记

建立时间和保持时间是时序分析最基础的概念,很多工程师只知道这两个概念的定义,但是未必知道需要建立时间和保持时间真正的原因。本文从CMOS门电路的结构和特性,逐步分析了为什么需要建立时间和保持时间的原因,为深入理解这两个概念提供了帮助。

本文作者:烓围玮未。 主要从事ISP/MIPI/SOC/车规芯片设计

首发于知乎专栏:芯片设计进阶之路

-

关于建立时间和保持时间的测量方法2023-12-05 4106

-

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量2023-09-04 1759

-

SOC设计中的建立时间和保持时间2023-08-23 2094

-

FPGA时序分析-建立时间和保持时间裕量都是inf怎么解决呢?2023-07-30 2389

-

到底什么是建立时间/保持时间?2023-06-27 19426

-

数字IC设计中的建立时间和保持时间2023-06-21 5322

-

静态时序之建立时间和保持时间分析2022-08-22 5809

-

为什么触发器要满足建立时间和保持时间2021-08-09 7772

-

数字 IC 笔试面试必考点(9)建立时间以及保持时间 精选资料分享2021-07-26 1196

-

保持时间与建立时间2018-11-29 3980

-

什么叫建立时间,保持时间,和恢复时间2017-04-08 4367

-

建立时间和保持时间(setup time 和 hold time)2017-02-08 7227

-

FPGA实战演练逻辑篇51:建立时间和保持时间2015-07-17 9194

-

建立时间和保持时间讨论2015-03-10 4891

全部0条评论

快来发表一下你的评论吧 !