浅析PCIe标准和布线的开发

接口/总线/驱动

描述

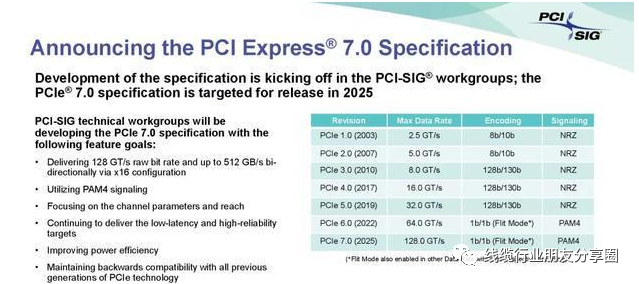

近日,PCI 特别兴趣小组 (PCI-SIG) 将在圣克拉拉举办其年度开发者大会。业界卓越的扩展总线的开发人员和生态系统成员的年度聚会为硬件开发人员提供了大量的技术会议,但对于局外人来说,来自该展会的最重要的新闻往往是 SIG 的年度更新状态生态系统。今年也不例外,他们更新了 PCIe 7.0 的开发状态,以及 PCIe 6.0 的采用和布线工作。据TomsHardware报道,PCIe 7.0规范的数据传输速率将再次倍增,达到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一个PCIe 7.0 x16通道可以支持512 GB/s,使用了四级脉冲幅度调制(PAM4)信令和1b/1b flit模式编码和前向纠错(FEC),这些都延用了之前PCIe 6.0规范的功能。

就像PCI-SIG设计的其他规范一样,每个PCI Express规范都会有五个主要的节点。

0.3版本:概念。该草案描述了需要实现的目标和实现这些目标的方法。

0.5版本:第一稿。这个版本必须完全解决0.3草案中设定的目标,它还包括所有的架构方面和要求。此外,它还包含了来自各相关方的反馈意见,此时PCI-SIG的成员可以将功能添加到正在制定的规范中。

0.7版本:完整草案。这个版本必须有一套完整的功能需求和方法定义,因为在这个版本之后不能再增加新的功能了。此外,电气规范必须已经使用测试芯片进行了验证。在这一点上,PCI-SIG成员可以提出新接口的不同实现。

0.9版本:最终草案。此时,PCI-SIG成员正在对技术进行内部审查,以确保其知识产权和专利。同时,不允许进行任何功能上的修改。

1.0版本:最终版本。从这个版本开始,所有的更改和增强都必须通过正式的勘误表文档和工程变更通知(ECN)。

据了解,和这几代的变化类似,PCIe 7.0在PCIe 6.0的基础上再次实现带宽翻翻,达到128GT/s,x16通道双向可以达到512GB/s。即便是SSD常走的x2/x4通道,理论峰值速度也分别提高到64GB/s和128GB/s,想象空间无限大。细节方面,PCIe 7.0和6.0一样,采用全新的PAM4调制,1b/1b编码。值得一提的是,PCIe 7.0依然保持了向下兼容。PCI SIG组织称,接下来的草案中会着重优化信道参数,并提高能效水平。PCIe 7.0规范将满足对可靠、高速、低延迟I/O互连的需求,路线图涵盖了数据密集型应用和市场,包括800Gig以太网、人工智能(AI)和机器学习(ML)、高性能计算(HPC)、量子计算、超大规模数据中心和云端应用等。PCIe 7.0规范需要更短的PCIe走线,这使得根设备和端点设备之间的距离进一步缩短。目前要实现PCIe 5.0的设计,需要更厚的PCB和更高质量的用料,也就是说成本提高了,暂时还不清楚PCIe 7.0对于这方面的考虑。按计划,PCIe 7.0标准正本会在2025年完工

PCIe 5.0/6.0 布线将于 2023 年末推出

New style

虽然 PCIe 7.0 正在开发中,但 PCIe 6.0 的第一个硬件仍在开发中,甚至 PCIe 5.0 设备也只有不到一年的时间。因此,在开发核心规范的同时,PCI-SIG 还在完成规范的一些辅助领域,特别是布线。预计将于今年第四季度发布。规格将涵盖 PCIe 5.0 和 PCIe 6.0(因为信号频率不变,PCIe 5.0的目的是简单地提高到PCIe 4.0标准的速度,而没有任何其他重要的新功能。例如,PCIe 5.0不支持PAM 4信号,只包括使PCIe标准能够在尽可能短的时间内支持32 GT/s所需的新功能),包括内部和外部电缆的规格。内部布线将把设备连接到系统内的其他部分——包括设备和主板/背板——而外部布线将用于系统到系统的连接。在信号技术和绝对信号速率方面,PCI Express 落后以太网一代左右。这意味着以太网工作组已经解决了高速铜信号的大部分初始开发问题。因此,尽管仍需努力使这些技术适用于 PCIe,但基本技术已经得到验证,这有助于稍微简化 PCIe 标准和布线的开发。

编辑:黄飞

-

PCIe 8.0规范开发更新!2025-09-25 6248

-

pcie布线对信号传输的影响2024-11-13 2113

-

数据中心布线标准有什么2024-06-14 1777

-

PCIe标准的演进历史 各代PCIe标准之间的主要差异2023-12-14 10923

-

PCIe:用CopprLink取代OCuLink?2023-11-16 3920

-

PCIe®标准演进历史2023-07-26 2975

-

2022最新综合布线规范标准来喽2023-05-23 8057

-

综合布线标准 看了这篇再施工!2023-03-22 2500

-

PCIe总线标准演进2022-11-29 1789

-

带宽进步推动 PCIe 标准2022-07-20 1730

-

综合布线系统的特点_综合布线系统标准2019-10-07 4001

-

PCIe是什么?PCIe标准和PCIe布线规则总结概述2018-10-03 44292

-

综合布线系统标准介绍2010-06-09 762

-

ISO9001:2000标准难点浅析2010-04-14 791

全部0条评论

快来发表一下你的评论吧 !