FPGA时序分析之关键路径

可编程逻辑

描述

关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径 (这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。

对关键路径进行时序优化,可以直接提高设计性能。对同步逻辑来说,常用的时序优化方法包括** Pipeline 、 Retiming 、逻辑复制、加法 / **乘法树、关键信号后移、消除优先级****等解决。

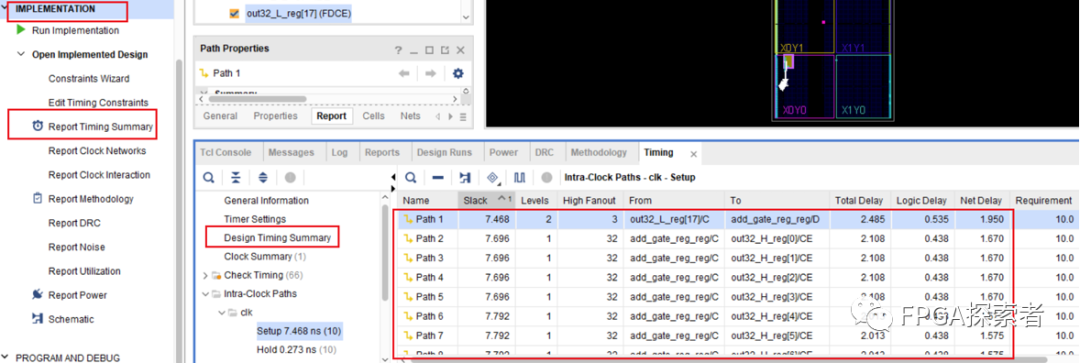

静态时序分析能够找出逻辑电路的关键路径。通过查看静态时序分析报告,可以确定关键路径。在Vivado工具中,可以通过report_timing_summary 等来查看,如下图所示, WNS ( Worst Nagative Slack )对应最大延迟分析的所有时序路径的最差裕量( Setup ) ,显示的Slack为时序裕量,Levels为该条路径上源逻辑驱动的级数,HignFanout为高扇出的值,源和目的,总的延时=逻辑延时+布线延时,这里,使用100MHz的时钟,对应周期10ns,逻辑延时最大0.535ns,布线延时1.950ns。

1. 组合逻辑中插入寄存器(插入流水线)

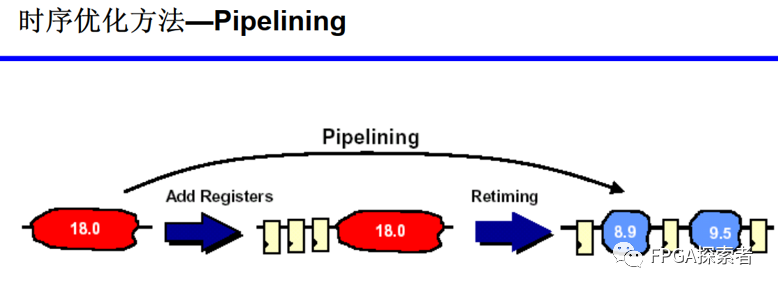

组合逻辑的延时过长,就会成为关键路径,这时可以考虑 在该路径上插入额外的寄存器 ,这种方法也称为插入流水线,多用于高度流水的设计中,因为这种设计中 额外插入寄存器增加的时钟周期延时并不会违反整个设计的规范要求,从而不会影响设计的总体功能性实现 ,也 即额外插入的寄存器在保持吞吐量不变的情况下改善了设计的时序性能 。当然,其不可避免地会带来部分面积的增加,如图6-11所示。

在插入寄存器时,要在组合逻辑中选择合适的位置进行插入,使得插入寄存器后被分割出的几块小的组合逻辑延时基本一致,也相当于下图所示的先加入寄存器,再对寄存器进行重定时 Retiming 。

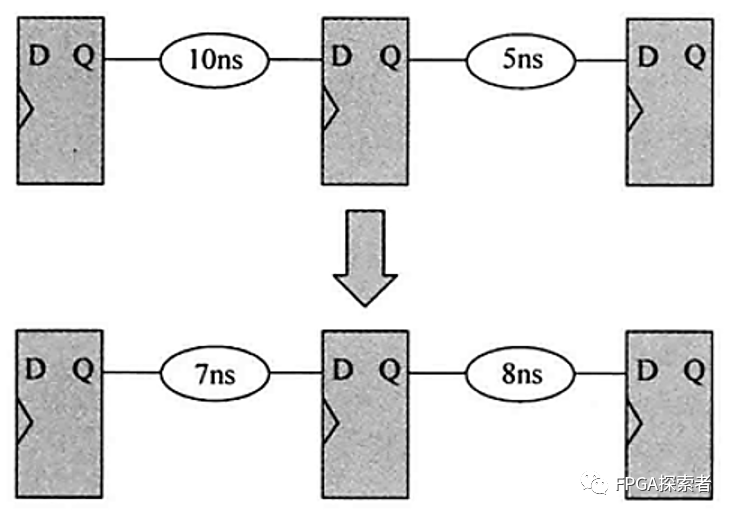

2. 寄存器平衡(重定时Retiming)

在不增加寄存器个数的前提下,通过改变寄存器的位置来优化关键路径 ,可以 对比和流水线插入寄存器的不同 。

3. 操作符平衡(加法树、乘法树)

平衡前,a和b均经过3个乘法器带来的延时,c经历2个,d经历1个,最长延时为3个乘法器延时。平衡后,树形结构,a、b、c、d均经历2个乘法器延时,最长延时为2个乘法器延时。

4. 消除代码优先级(case代替if…else)

本身确实不需要优先级的地方,可以使用case代替if…else ,使得顺序执行的语句编程并行执行。如果确实有优先级兵,则不能这样做。这种消除代码中的优先级的策略也称为代码结构平坦化技术,主要针对那些带优先级的编码结构。

5. 逻辑复制

当某个信号的扇出fanout比较大时,会造成该信号到各个目的逻辑节点的路径变得过长,从而成为设计中的关键路径,此时可以通过对该信号进行复制来降低扇出。高扇出的危害是大大增加了布局布线的难度,这样其扇出的节点也就无法被布局得彼此靠近,所以就导致了布线长度过大的问题。

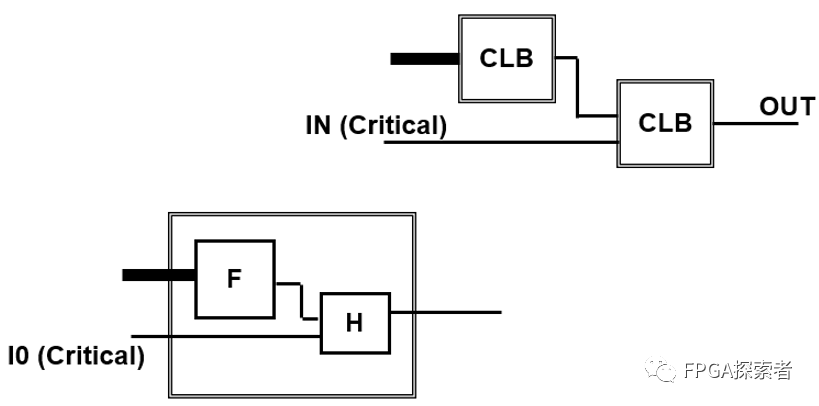

6. 关键信号后移

关键输入应该在逻辑最后一级提供,其中关键输入为芯片、Slice、或者LUT提供的时延最大的输入,比如在if…else if…链中,将关键信号放在第一级。

-

FPGA时序约束之设置时钟组2025-04-23 1637

-

FPGA时序约束之时序路径和时序模型2023-08-14 1704

-

详解时序路径的相关概念2023-06-26 2170

-

FPGA时序约束之伪路径和多周期路径2023-06-12 3235

-

如何从时序分析中排除跨时钟域路径?2022-08-02 1864

-

什么是时序路径和关键路径?2021-09-28 2378

-

时序路径和关键路径的介绍2021-07-26 1372

-

全面解读时序路径分析提速2021-05-19 4186

-

华为FPGA硬件的静态时序分析与逻辑设计2020-12-21 1660

-

详细解析vivado约束时序路径分析问题2020-11-29 10474

-

FPGA案例之时序路径与时序模型解析2020-11-17 3955

-

大西瓜FPGA--FPGA设计高级篇--时序分析技巧2017-02-26 6895

-

基于时序路径的FPGA时序分析技术研究2017-01-03 982

-

时序关键路径2014-02-27 4520

全部0条评论

快来发表一下你的评论吧 !