FPGA的编译过程讨论

可编程逻辑

描述

综合

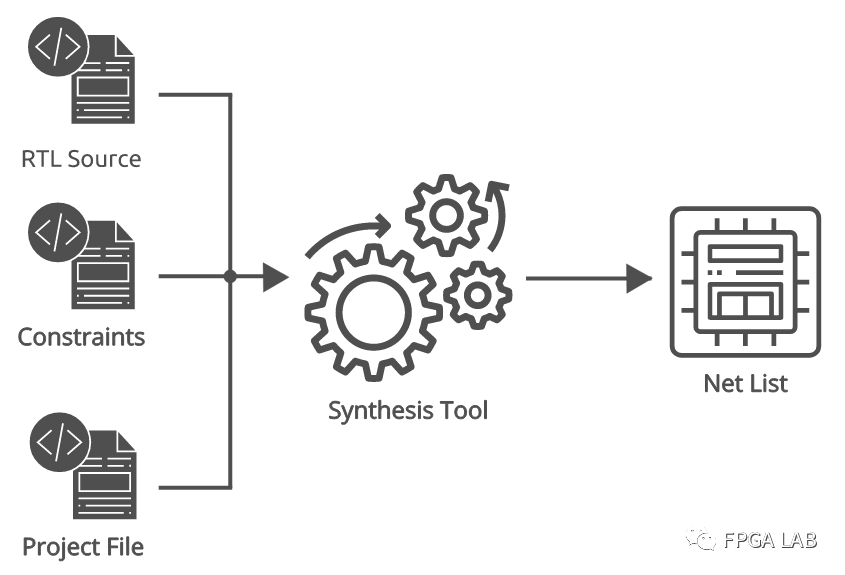

构建FPGA的第一阶段称为综合。此过程将功能性RTL设计转换为门级宏的阵列。这具有创建实现RTL设计的平面分层电路图的效果。

在这种情况下,宏实际上是内部FPGA单元的模型。这可以是FPGA中的任何数字元素,例如触发器,RAM或查找表(LUT)。

综合工具

我们可以使用许多不同的工具来运行综合过程。

两个主要的FPGA供应商(Xilinix 和 Intel)都提供适用于大多数项目的免费综合工具。

除此之外,还有许多 我们可以使用的开源综合工具。这些工具中最流行的是 yosys ,它经常与 Lattice FPGA一起使用。

也有用于此目的的付费工具。这些工具中最著名的是Synopsys的Synplify Pro 和Mentor Graphics的Leonardo Spectrum。

与免费工具相比,付费工具通常能够提供更多优化的网表。通常,对于大型或高速设计,我们只需要付费工具即可。

综合过程至少需要两个输入。

其中第一个是我们设计的源代码。

我们还需要一个脚本或项目文件,用于定义综合工具的配置。该脚本通常告诉工具目标为哪个FPGA,设计的引脚以及在运行综合时使用哪种策略。

除此之外,优良作法是创建一个文件,该文件定义设计的时序约束,我们称之为约束文件。

综合

我们使用时序约束来定义有关FPGA的细节,而这些细节无法在源代码中指定。

这包括诸如时钟频率,时钟域数和外部接口的时序之类的信息。

这些细节决定了综合器为优化FPGA内的时序投入了多少精力。

逻辑利用率

作为综合过程的一部分,我们还可以对设计进行一些分析。但是,在布局和布线过程之后,此信息通常更可靠。

这些分析中的第一个是设计的逻辑利用率。该分析详细说明了我们设计使用的每种不同类型的FPGA单元有多少个。

设备中的各个单元随芯片的不同以及供应商之间的不同而不同。

几乎所有现代芯片都将包括RAM,某种形式的LUT和触发器。

高端芯片还可以包括专用的DSP内核,时钟管理模块(例如PLL)以及其他外围接口(例如ADC)或专用的高速接口。

完成综合过程后,我们可以生成报告,以绝对值和器件中所有可用单元的百分比告诉我们设计中使用了多少个单元。

在运行综合过程之后,经常会发现我们的设计对我们的设备而言太大了。发生这种情况时,我们有很多选择。

通常可以通过更改综合工具的配置来降低利用率。这样的示例可以是更改FSM编码或选择其他综合算法。

如果我们的设计仅比我们选择的FPGA大一点,那么这种减少就足够了。

如果这还不能充分降低利用率,那么我们必须选择一个新的FPGA或提高原始代码的效率。

时序分析

运行综合后,我们还可以分析FPGA的时序。

我们使用该分析来确定FPGA是否可以以所需的频率运行我们的设计。

当我们的设计不能以所需的频率运行时,我们不能确定内部触发器将不会有时序违规。因此,我们无法保证我们的设备能够按预期运行。

我们通常会在布局和布线过程之后详细分析设计的时序。由于时序取决于FPGA中单元的位置,因此经过此过程,结果将更加准确。

综合后仿真

在综合过程中,我们可以要求该工具以VHDL或verilog生成网表。

此过程还生成一组时序延迟,该时序延迟可对信号通过FPGA的传播进行建模。

然后,我们可以使用此信息来运行我们的综合网表的仿真。

由于这些仿真还可以对我们的设计时序进行建模,因此它们可以为最终设备的行为提供更准确的模型。

无论我们在设计中使用哪种语言,我们通常都使用verilog生成综合后仿真模型。

这样做的原因是基于Verilog的模型比其VHDL等效模型的仿真速度更快。这对于综合后仿真尤其重要,因为它们通常执行时间较长。

运行综合后仿真有两个主要优点。

- 首先,这些仿真有助于确保我们生成的网表与原始RTL模型的行为相匹配。

- 其次,可以更紧密地考虑芯片的时序。这有助于我们发现可能与基于时序的错误(例如时序违规)相关的错误。

尽管运行后综合仿真有很多优点,但是我们通常不会在设计流程中这样做。

- 原因之一是这些仿真需要很长时间才能运行。综合后的仿真需要几天来运行全套测试的情况并不少见。

- 另一个原因是,我们也可以在由我们的布局和布线工具生成的网表上运行仿真。

由于这些网表更能代表最终的芯片方案,因此最好使用该网表进行任何时序仿真。

布局布线(实现)

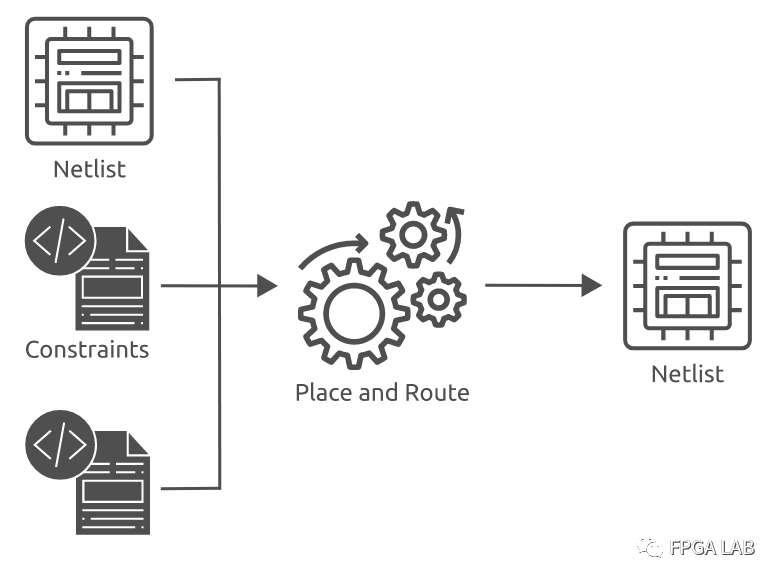

完成综合后,我们需要将网表映射到FPGA中的实际资源。此过程称为“布局布线”,实际上包含几个不同的步骤。

- 通常,此过程的第一阶段涉及优化网表。我们使用此过程删除或替换网表中任何多余或重复的元素。

- 然后,将优化后的网表映射到FPGA中的物理单元,这通常称为布局。

- 完成布局过程后,然后运行称为布线的过程。

我们使用构建过程的这一部分来定义所选FPGA中不同单元之间的互连。

为了满足设计的时序要求,我们通常会执行此过程的几次运行。但是,布局布线工具负责根据我们的配置安排这些多次运行。

当我们难以使设计满足时序要求时,通常会增加允许工具执行的运行次数和类型。

布局布线工具

对于Xilinx或Intel部件,没有第三方布局和布线工具,这意味着我们必须使用供应商特定的工具。这些版本可以免费下载,尽管也提供付费版本。

这些工具也有付费版本可用,尽管通常只有针对高端FPGA的设计才需要它们。

对于莱迪思的FPGA,开源的nextpnr软件是一种流行的布局布线工具。

根据我们设计的大小,布局和布线过程可能需要几个小时才能完成。

与综合过程一样,布局布线工具需要大量输入才能正确运行。

我们使用综合工具生成的网表是最重要的输入。该网表通常是.edf文件,尽管这在工具之间有所不同。

通常,我们还使用项目文件或脚本来确定布局和布线工具的配置。

我们使用它来定义重要信息,例如FPGA零件号和封装。除此之外,我们使用此脚本定义布局和路线工具的配置。

我们还需要向工具提供一个约束文件,以定义我们设计的时序特征。该文件通常与我们在综合过程中使用的文件相同,该文件定义了有关时钟频率和域的信息。

我们还使用约束文件来定义我们的设计的物理特性,而这些特性在HDL代码中无法描述。至少,这将包括输入和输出到设备物理引脚的映射。

流程图显示了综合网表,约束和项目文件作为布局和布线工具的输入,网表作为输出。

布局布线

时序与利用率

与综合过程一样,在布局和路线完成之后,我们可以生成许多报告。这使我们可以进一步分析设计以确保其正常工作。

我们通常会在完成布局和布线过程后运行实用程序报告。

该报告详细介绍了我们用于通过FPGA实现设计的不同单元的数量。

该报告与我们在综合过程中可以生成的报告完全相同。但是,当我们在完成布局布线过程后生成此报告时,该报告会更准确。

我们通常在完成布局和布线过程后执行的另一项分析是静态时序分析(STA)。

我们使用此过程来计算设计中所有逻辑链的延迟时间。通过计算此信息,布局布线工具可以确定芯片是否能够以指定的时钟频率运行。

布局布线工具会在最坏情况和最佳情况下的定时条件下执行此分析。但是,最常见的情况是在硅中出现最坏情况下的延迟会导致时序问题。

我们通常将STA报告用作设计验证的关键部分。

如果我们的设计使STA失败,那么我们将无法保证FPGA能够可靠地工作。发生这种情况时,我们要么必须使用不同的设置再次运行实施过程,要么必须更改设计。

编程文件生成

FPGA设计实现的最后阶段是生成编程文件。

通常,我们使用布局和布线工具来生成我们的编程文件。

但是,我们通常将其作为单独的过程运行。

仅当布局和布线过程生成其输出后,才能运行此过程。我们只需要告诉工具生成该输出所需的文件类型即可。

完成此过程后,我们可以使用生成的文件对FPGA进行编程。

-

C语言的编译过程2023-06-25 1066

-

Linux内核的编译主要过程2023-08-08 1307

-

C语言的编译链接过程2023-08-21 3757

-

C程序的完整编译过程2023-11-15 5644

-

简化Xilinx和Altera FPGA调试过程2009-11-20 633

-

FPGA的ROM初始化问题讨论2012-02-08 5981

-

谁能缩短大容量FPGA的编译时间?增量式编译QIC!2012-12-25 9753

-

基于FPGA的3B4B编译码电路2017-02-07 1606

-

编译UCOSII源码过程2017-10-30 1220

-

Linux内核编译过程详解2017-11-07 1104

-

基于FPGA处理器的C编译指令2017-11-18 3223

-

如何节省FPGA编译时间?2018-08-04 7436

-

赛灵思软件通过调整编译参数以及运行并行编译来优化FPGA时序性能2019-07-26 4469

-

解析C语言编译过程中所做的工作2021-06-27 4272

-

OpenHarmony应用的编译构建过程2022-04-21 5387

全部0条评论

快来发表一下你的评论吧 !