CRC校验码的多种Verilog实现方式

电子说

描述

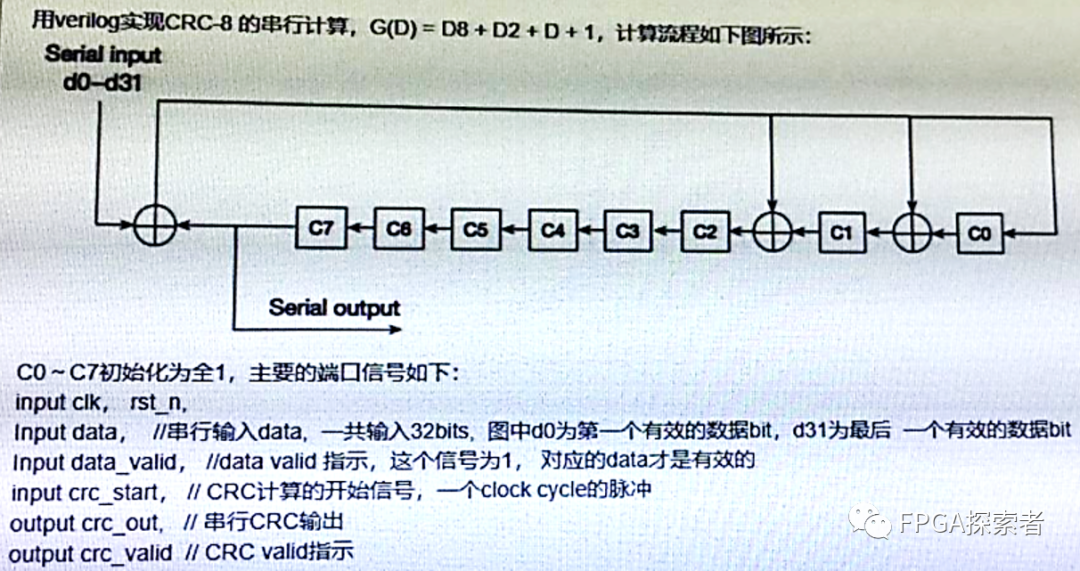

用Verilog实现CRC-8的串行计算,G(D)=D8+D2+D+1,计算流程如下图所示:

一、分析

CRC循环冗余校验码(Cyclic Redundancy Check),检错码。

(1)该题目所述为CRC-8,即输出8位CRC校验值,给定一段长为N-bit的有效输入序列,输出(N+8)-bit的数据,其中前N-bit数据为输入的原始数据,添加的8-bit数据为CRC校验数据;

(2)该CRC-8的生成多项式为G(D)=D8+D2+D+1,对CRC进行简化表示时可以忽略最高位的D8,结合图示中三个异或运算的位置更容易理解生成多项式,8位CRC有8个寄存器C0~C7,根据多项式,C0、C1和C2的输入是由异或运算而来;

二、Verilog编程

1. 并行计算,串行输出

对于输入位宽为****1 的输入,这种方法的计算非常简单,直接根据生成多项式运算 。

( 注意! 如果输入位宽不为1,则需要根据多项式进行化简,可以生成运算逻辑和代码)

1.1 自己一步一步写

( 1 )先定义8个寄存器****reg [7:0]

reg [7:0] crc_reg_q;// 寄存器 Q 输出端

reg [7:0] crc_reg_d;// 寄存器 D 输入端

(对crc_reg_d,使用always赋值就定义成reg,使用assign就定义成wire)

( 2 )异或计算

** 寄存器0的输入** crc_reg_d[0] ,来自寄存器7的输出 crc_reg_q[7] 和数据输入****data_in 异或运算 ,即:

crc_reg_d [0] = crc_reg_q[7] ^ data_in;

同理可得:

always @ (*)

begin

crc_reg_d[0] = crc_reg_q[7] ^ data_in;

crc_reg_d[1] = crc_reg_q[7] ^ data_in ^ crc_reg_q[0];

crc_reg_d[2] = crc_reg_q[7] ^ data_in ^ crc_reg_q[1];

crc_reg_d[3] = crc_reg_q[2];

crc_reg_d[4] = crc_reg_q[3];

crc_reg_d[5] = crc_reg_q[4];

crc_reg_d[6] = crc_reg_q[5];

crc_reg_d[7] = crc_reg_q[6];

end

上述使用组合逻辑实现异或运算和数据的传递,另外,对于每个寄存器的输入到输出(D端到Q端),使用时序逻辑,并且按照题目要求,设置初始值为全1,将数据有效标志作为控制逻辑:

always @ (posedge clk)

begin

if( rst)

crc_reg_q <= 8’hff;

elsebegin

if(data_valid )

crc_reg_q<= crc_reg_d;// 输入数据有效就更新值

else

crc_reg_q<= crc_reg_q;// 输入数据无效就等待

end

end

( 3 )串行输出

上述已经实现了并行的 CRC,计算出的 CRC 结果就是直接的 8 位 CRC,按照题目要求,需要串行输出 CRC 结果。

思路:写一个计数器,当需要输出 CRC 时,串行计数输出,实现并串转换。这里,由于题目给了一个信号 crc_start,我把这个信号作为 CRC 的标志,当 data_valid 有效时表示输入的是数据,当 data_valid 无效且crc_start 有效表示数据输入完毕,该输出 CRC 了。

reg [2:0] count;

always @ (posedge clk)

begin

if(rst)begin

crc_out <= 0;

count<= 0;

end

elsebegin

if(data_valid) begin

crc_out <= data_in;

crc_valid <= 1'b0;

end

elseif(crc_start)begin

count <= count + 1'b1;

crc_out <= crc_reg_q [7-count];

crc_valid <= 1'b1;

end

elsebegin

crc_valid <= 1'b0;

end

end

end

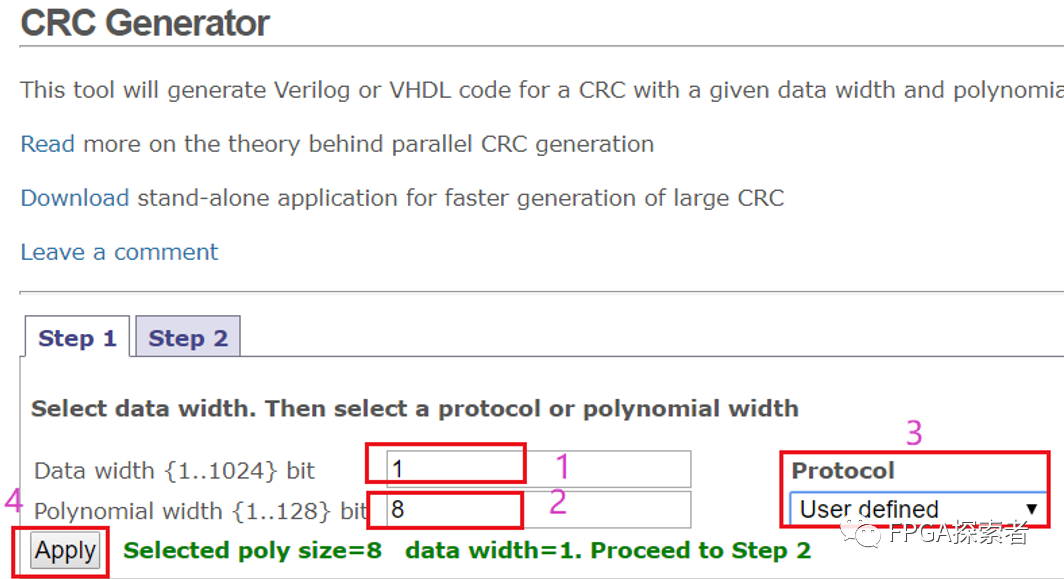

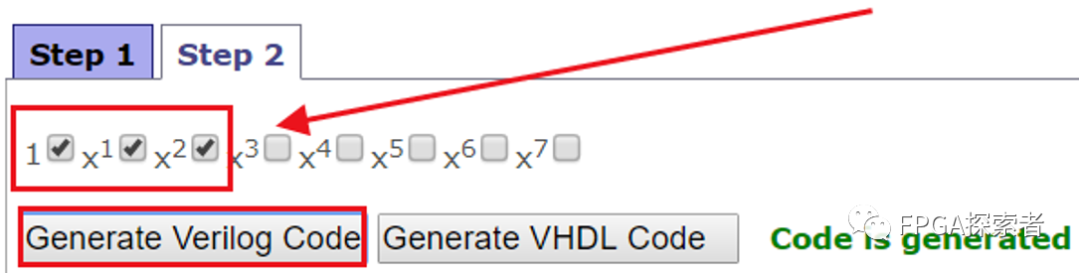

1.2 CRC Generator自动生成

根据生成多项式,勾选1、X1、X2即可(对应1+D1+D2,最高位的D8不用管)。

//-----------------------------------------------------------------------------

// Copyright (C) 2009 OutputLogic.com

// This source file may be used and distributedwithout restriction

// provided that this copyright statement is notremoved from the file

// and that any derivative work contains theoriginal copyright notice

// and the associated disclaimer.

//

// THIS SOURCE FILE IS PROVIDED "ASIS" AND WITHOUT ANY EXPRESS

// OR IMPLIED WARRANTIES, INCLUDING, WITHOUTLIMITATION, THE IMPLIED

// WARRANTIES OF MERCHANTIBILITY AND FITNESS FORA PARTICULAR PURPOSE.

//-----------------------------------------------------------------------------

// CRC module for data[0:0] , crc[7:0]=1+x^1+x^2+x^8;

//-----------------------------------------------------------------------------

module crc(

input [0:0] data_in,

input crc_en,

output [7:0] crc_out,

input rst,

input clk);

reg [7:0] lfsr_q,lfsr_c;

assign crc_out = lfsr_q;

always @(*) begin

lfsr_c[0] = lfsr_q[7] ^ data_in[0];

lfsr_c[1] = lfsr_q[0] ^ lfsr_q[7]^ data_in[0];

lfsr_c[2] = lfsr_q[1] ^ lfsr_q[7]^ data_in[0];

lfsr_c[3] = lfsr_q[2];

lfsr_c[4] = lfsr_q[3];

lfsr_c[5] = lfsr_q[4];

lfsr_c[6] = lfsr_q[5];

lfsr_c[7] = lfsr_q[6];

end // always

always @(posedge clk, posedge rst) begin

if(rst) begin

lfsr_q <= {8{1'b1}};

end

else begin

lfsr_q <= crc_en ? lfsr_c: lfsr_q;

end

end // always

endmodule // crc

将上述代码按照题目要求改变输入输出的名称,并进行串并转换(并->串)即可。

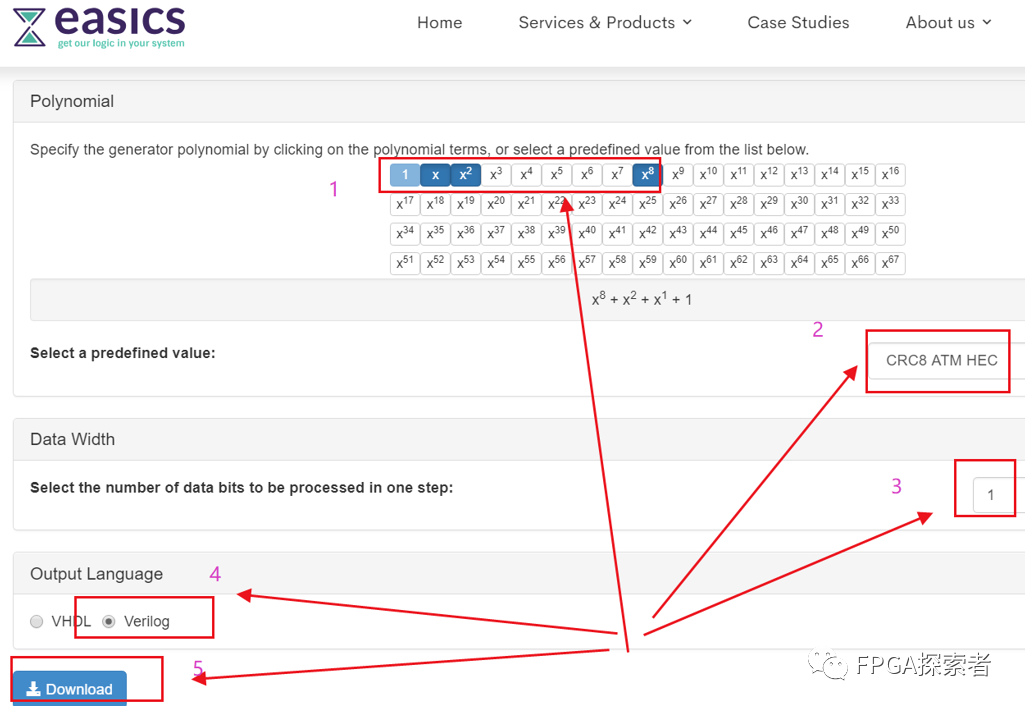

1.3 easics自动生成

(1)1处选择CRC的生成多项式,这里与1.2的不同在于,要把最高位的D8选上,easics能识别的CRC协议更多;

(2)2处自动识别出这个CRC多项式其实是CRC8 ATM HEC协议使用的 CRC;

(3)3处设置输入数据位宽为1;

(4)选择生成Verilog代码;

(5)下载代码。

仔细阅读代码注释,注意!

convention: the first serial bit is D[0]

数据的最低位先输出 ,此代码将会把低位作为异或移出位,而上面已经提到的两种方法均是将最高位作为移出位去异或, 所以,代码中需要稍作修改 ,将d[0]改成d[7],d[1]改成d[6],…,以此类推,c[0]- c[7]不要变。

有兴趣的可以去看看【大小端问题】,在不同处理器、不同协议中非常常见。

///////////////////////////////////////////////////////////////////////////////

// Copyright (C) 1999-2008 Easics NV.

// This source file may be used and distributedwithout restriction

// provided that this copyright statement is notremoved from the file

// and that any derivative work contains theoriginal copyright notice

// and the associated disclaimer.

//

// THIS SOURCE FILE IS PROVIDED "AS IS"AND WITHOUT ANY EXPRESS

// OR IMPLIED WARRANTIES, INCLUDING, WITHOUTLIMITATION, THE IMPLIED

// WARRANTIES OF MERCHANTIBILITY AND FITNESS FOR APARTICULAR PURPOSE.

//

// Purpose : synthesizable CRC function

// *polynomial: x^8 + x^2 + x^1 + 1

// * datawidth: 1

//

// Info : tools@easics.be

// http://www.easics.com

///////////////////////////////////////////////////////////////////////////////

module CRC8_D1;

//polynomial: x^8 + x^2 + x^1 + 1

// datawidth: 1

//convention: the first serial bit is D[0]

function[7:0] nextCRC8_D1;

inputData;

input[7:0] crc;

reg [0:0]d;

reg [7:0]c;

reg [7:0]newcrc;

begin

d[0] =Data;

c = crc;

newcrc[0]= d[0] ^ c[7];

newcrc[1]= d[0] ^ c[0] ^ c[7];

newcrc[2