Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

可编程逻辑

描述

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

(1)主要先把我博客的介绍原理的文章搬过来;

(2)用 FPGA 的实例看下 AXI4 和 AXI4-Lite 的握手;

(3)自定义一个 AXI-Lite 的 IP 作为从机设备 Slave,并将其挂载到 AXI Interconnect 上,由 ZYNQ 的 PS 侧作为主机来控制 LED;

(4)对 AXI-Lite 作源码分析。

AMBA® AXI4(高级可扩展接口 4) 是 ARM® 推出的第四代 AMBA 接口规范,AMBA(Advanced Microcontroller Bus Architecture)是片上总线标准,包含AHB(Advanced High-performance Bus)、ASB(Advanced System Bus)和 APB(Advanced Peripheral Bus)。

AXI ( Advanced eXtensible Interface ),高性能、高带宽、低延迟片内总线。

AXI4:高性能内存映射需求(如读写DDR、使用BRAM控制器读写BRAM等),为了区别,有时候也叫这个为 AXI4-Full;

AXI4-Lite:用于简单、低吞吐量的内存映射通信(例如,与控制寄存器和状态寄存器之间的通信);

AXI4-Stream :高速流数据(视频、图像等流式数据);

AXI4 具有:

(1)一致性: 所有接口子集都使用相同的传输协议。

(2)全面规范化: 便于客户采用。

(3)标准化: 配套提供标准模型和检查器以供设计人员使用。

(4)接口去耦化: 互连电路与接口之间有去耦机制。

(5)可扩展性: AXI4 是一种可满足未来需求的开放式标准。

其它优势:

(1)支持存储器映射型和串流型接口;

(2)为通信、视频、嵌入式以及 DSP 功能提供统一化 IP 接口;

(3)简便易用,并具有自动流水线例程化等特性,可帮助用户轻松实现既定性能目标;

1. AXI4

AXI4 协议是 AXI3 的升级,旨在提高多个主系统使用时的互连性能和互连利用率。其包括了如下增强功能:

(1)支持高达 256 个突发长度

(2)服务质量信令

(3)支持多个区域接口

2. AXI4-Lite

AXI4-Lite 是 AXI4 协议的子集,旨在与组件中较小较简单的控制寄存器型接口实现通信。AXI4-Lite 接口主要特性为:

(1)所有处理的突发长度为 1

(2)所有数据存取的大小等同于数据总线宽度

(3)不支持独占访问

3 . AXI4-Stream

AXI4-Stream 协议针对主系统向从系统进行单向数据传输, 流式数据(比如视频流) 。该协议的主要优势包括:

(1)使用相同的共享线集支持单数据流和多数据流;

(2)在同一互连中支持多数据宽度;

(3)FPGA 实现的理想选择。

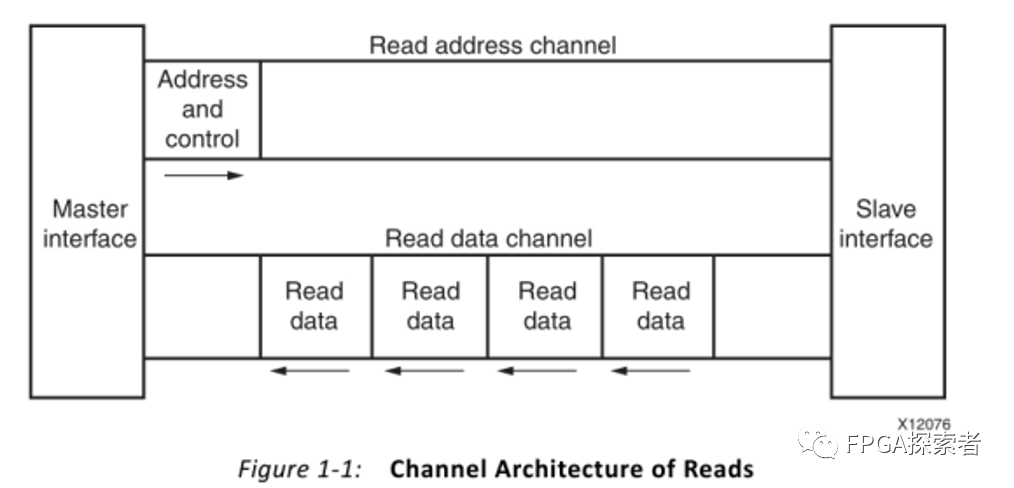

如图 1-1 所示为 AXI4 读事务使用读地址和读数据通道,主机在读地址通道上给出要读取的数据的地址和控制信息(当突发读取多个数据时,给出数据存储的首地址和突发长度),从机收到后在将数据通过读数据通道发送给主机。

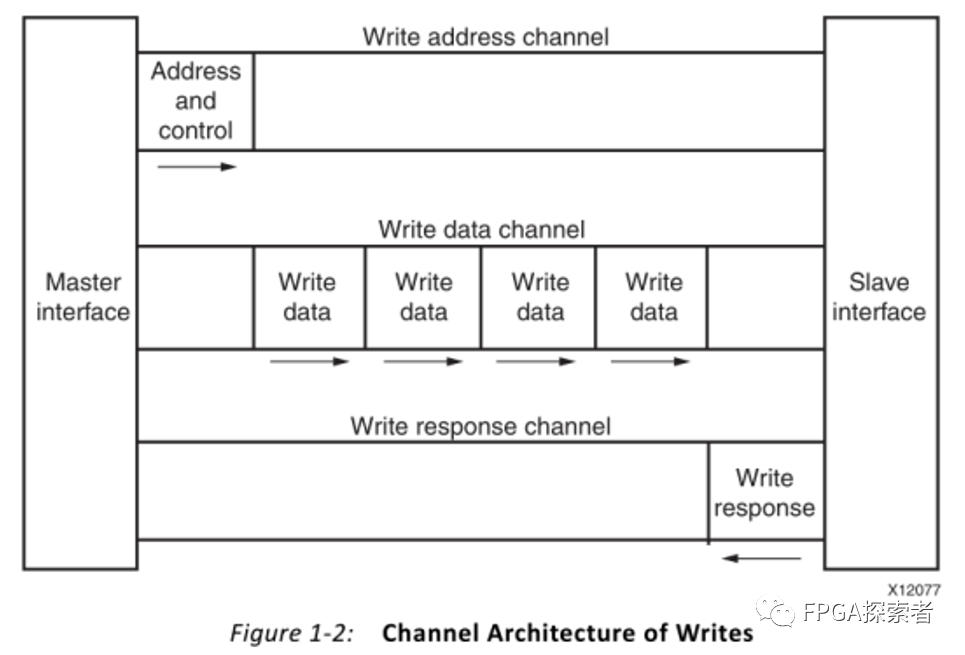

如图 1-2 所示为写事务使用写地址、写数据和写响应通道的方式,主机首先向发送写控制,然后发送要写入的数据,从机在收完本次写事务的数据后给出写响应信号代表接收完成。

AXI4-Stream协议为流数据的传输定义了单个通道,与****AXI4 不同, AXI4-Stream 接口可以突发无限数量的数据 。

对上述5个独立的通道,每个通道都包含一个信息信号和一个双路的 valid 、 ready 握手信号, valid 信号表示发出的数据有效, ready****信号表示已经准备好。

-

Zynq中AXI4-Lite和AXI-Stream功能介绍2020-09-27 10085

-

Xilinx zynq AXI总线全面解读2020-12-04 9347

-

NVMe IP之AXI4总线分析2025-06-02 6195

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3297

-

AMBA 4 AXI4、AXI4-Lite和AXI4-流协议断言用户指南2023-08-10 689

-

AXI4接口协议的基础知识2020-09-23 7235

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7554

-

ZYNQ中DMA与AXI4总线2020-11-02 5285

-

AXI-Stream代码2020-11-05 4986

-

深入AXI4总线一握手机制2021-03-17 1269

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10926

-

使用AXI4总线实现视频输入输出2022-10-11 7902

-

AXI3与AXI4写响应的依赖区别2023-03-30 2068

-

FPGA AXI4协议学习笔记(二)2023-05-24 3033

-

FPGA通过AXI总线读写DDR3实现方式2024-04-18 2673

全部0条评论

快来发表一下你的评论吧 !