操作BASEPRI特殊功能寄存器时无效解决方法(上)

描述

有STM32用户发现在操作BASEPRI特殊功能寄存器时,根本不起作用。比方,它目前配置了几个中断,优先级各不相同,按照STM32CubeMx里的配置分别为2、3、4不等,当他在BASEPRI寄存器里写这几个数字中的任意一个时,发现BASEPRI的数字始终是0,没有任何效果。

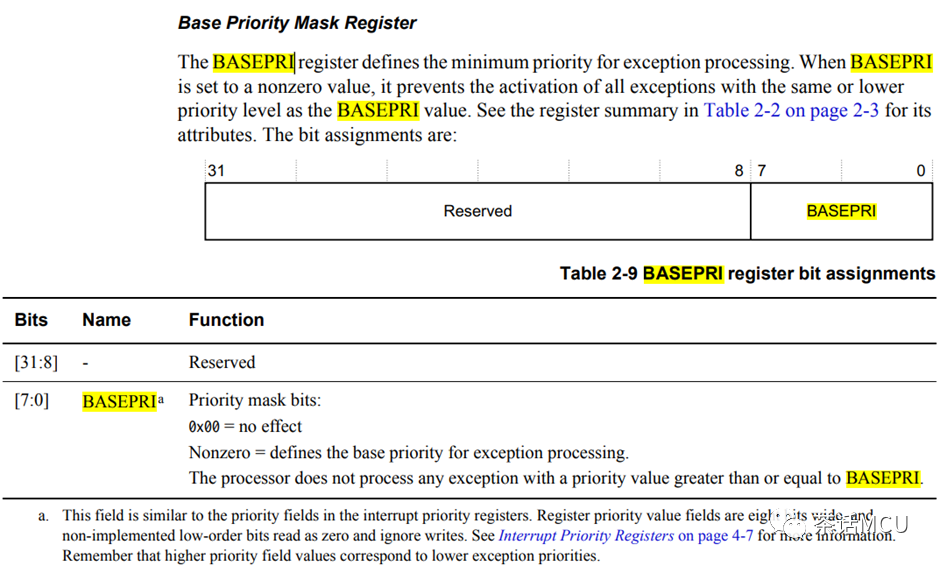

我们知道,通过配置BASEPRI寄存器非0值来给系统中的中断响应设置门槛,当中断优先级低于某个级别时将不会得到CPU的响应执行,也就是说只有中断优先级高于某个级别时才能得到响应。下面截图是来自ARM

CORTEX M4技术手册中有关BASEPRI寄存器的描述。

从这里可以看到该寄存器的有效配置位有8位,对其写0无意义,或者说放弃设置中断响应门槛功能。在ARMCORTEX-M内核系统里,中断优先级的高低跟表示优先级的数字大小成相反关系,即数字越小的中断优先级配置值所对应的优先级反而越高。

根据BASEPRI寄存器的定义,假设给BASEPRI写数字5,那就意味着只有中断优先级高于5的中断,即中断优先级的数字小于5的中断可以得到响应,而其它低于优先级5的中断将会被屏蔽。【注:这里说的优先级比较最终都体现在抢占优先级上】

另外,在ARM内核里关于每个中断的优先级配置寄存器也是8位,并支持字节访问。

内核里还有跟中断优先级有关的寄存器,它把中断优先级配置位分成2部分,用来分别设置每个中断的组优先级和子优先级,或称抢占优先级和响应优先级,也有称主优先级和子优先级的,意思都一样。个人喜欢中间的术语。

以上图优先级分组值【PRIGROUP】等于3为例。中断优先级寄存器中的bit0bit3用作配置该中断的响应优先级,显然,它的值可以是0到15的任一值。bit4bit7用来配置该中断的强占优先级,同样它的值也可以是0到15的任一值。若以【PRIGROUP】等于7为例,则所有可配置优先级的中断只配置响应优先级,不区分强占优先级,或者说抢占优先级都一样,或者说彼此不发生中断抢占都一个意思。所谓中断抢占即指另一中断事件打断正在执行的中断服务程序而响应更高优先级的程序。

上面都基于ARM

Cortex-M内核的最初设计来说的,我们知道,STM32是基于ARM内核添加ST的外设而成,ST在设计芯片的中断优先级这个地方,在AMR核的设计基础上做了些针对性的调整,涉及中断优先级的寄存器的有效控制位由8位变成4位,且仅使用高4位,低4位变成保留位。【下图来自STM32

Cortex M4 编程手册。注意红色下划线特别说明。】

不难理解,BASEPRI寄存器也会跟着做了调整,不然没法跟上面调整过的中断优先级寄存器匹配,它也只使用高4位,低4位变保留位。【下图来自STM32F4系列编程手册】

当然,关于优先级分组的控制寄存器的内容也做了相应调整,即针对优先级寄存器的高4位来划分抢占优先级和响应优先级的配置。详见下图:

把上图的各种优先级分组配置变得更直观点就是下图的样子。绿色用于配置抢占优先级,黄色用于配置响应优先级,灰色保留位,一共有5种可能的分组情形。

聊到这里,我们得知每个可配置的STM32片内中断,都有一个8位优先级配置寄存器与之对应,且只用到高4位。我们接着看看开篇的问题。目前STM32的有关中断配置如下图所示【使用STM32CubeMx工具进行】:

-

特殊功能寄存器的解释整理汇总2024-05-09 540

-

操作BASEPRI特殊功能寄存器时无效解决方法(下)2023-06-21 2637

-

为何修改BASEPRI寄存器无效?2023-04-26 3680

-

STC单片机常用特殊功能寄存器速查2022-09-30 1097

-

特殊功能寄存器位置及功能是什么2022-01-05 884

-

51单片机的特殊功能寄存器到底在哪,为何51子系列没有高128B仍然有特殊功能寄存器2021-11-23 1194

-

7课:单片机的特殊功能寄存器 2020/11/152021-11-20 881

-

51单片机的21个特殊功能寄存器的详细资料说明2019-09-10 2586

-

51单片机的21个特殊功能寄存器详细资料概述2019-07-09 4975

-

51单片机常用的特殊功能寄存器有哪些2019-07-08 1533

-

【硬见小百科】单片机的特殊功能寄存器2019-01-16 6373

-

在C语言环境下访问特殊功能寄存器sfr的经验2017-11-10 10890

-

特殊功能寄存器2012-02-06 2425

-

关于三星2410A处理器特殊功能寄存器问题2011-10-02 4428

全部0条评论

快来发表一下你的评论吧 !