定时器DMA Burst传输无法实现

描述

有人使用STM32F4系列开发产品,程序运行过程中需要不时地对外输出一串驱动脉冲,并要求这几串脉冲的频率可变、占空比固定。他想到使用基于STM32定时器的DMA

BURST传输。具体点说,他期望不时地通过TIM3的CH1输出一串频率可变、占空比固定的脉冲然后停下来。这个思路在原理上是没问题的,可是他在测试过程中发现怎么也折腾不出预期的效果。

他目前使用的芯片是STM32F401,虽有点老旧,但我查看了手册,确认该芯片的TIM3是支持基于TIMER事件实现TIME寄存器与内存间的DMABURST传输的。即每个TIMER事件可以申请多个DMA请求从而实现定时器寄存器与内存间的批量数据传输。要知某个STM32

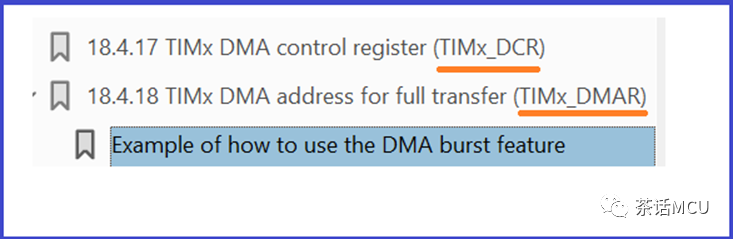

TIMER是否支持上述功能,只需查看STM32参考手册的相关定时器的寄存器中有无TIMx_DCR和TIMx_DMAR寄存器的介绍。

既然支持,为什么实现不了呢?关于这个功能我们还需要注意几点:

1、所选择的TIMER必须支持基于定时器事件的DMA BURST传输功能。

2、触发事件必须是来自参与DMA传输的定时器事件,不能是别的定时器事件。比方说你想实现TIM1的寄存器与内存间的DMA

BURST传输,触发事件不能是来自TIM2、TIM3这些非TIM1的事件。

3、定时器DMA

Burst传输时,用来被BURST访问的定时器寄存器应该是同一定时器的而且是地址连续的寄存器,不可跳跃访问。比方说像下面某TIMER的4个比较寄存器物理地址是安排在一起的,而CH2恰好因为某些原因没有被用上。

如果你仅对CH1/CH3/CH4三个通道的比较寄存器的值做BURST访问,此时尽管CH2没有被用上,BURST访问的传输个数应该是4而不是3。

4、STM32

HAL库里的例程或函数重点在演示相应的功能或特性,但它不能包罗万象或保证适用于任何场景。有些时候我们可能需要在现有库函数的前提下适当地做些调整来满足需求。

结合这几点,我们一起排查下。第1点、第2点已经核对过了,没问题。看看第3点,即设置BURST传输个数。下图是F40x系列TIM2~TIM5的内存地址映射图。

现在使用者真正需要用到的寄存器只有TIM3-》ARR和TIM3-》CCR1两个寄存器,但二者中间还有个预留空位【其它高级定时器的RCR寄存器的位置】也必须算进来,即这里BURST传输个数应该是3而不是2。

再看看上面提到的第4点要注意的地方。这点我就不过多解释了,ST提供的HAL库例程及相关函数只能实现1次BURST传输的功能,如果要实现多次BURST传输就得在其代码基础上做些调整,更多细节可以参考我之前分享的那篇《STM32定时器BURST传输介绍及示例》。不过,在那篇的演示例程里我使用的是DMA

Circular模式,现在的用户则要使用DMA

Normal模式。采用Normal模式和采用Circular模式基于现有HAL库函数组织代码还略有差异,若没处理好这点小差异,可能让你完全出不来想要的结果。

下面我使用STM32G4芯片的TIM3-CH1演示上面用户的功能。每次输出5个脉冲,3次输出为一个循环,同一循环中的3次输出的频率各不相同,占空比一样。【为什么没用STM32F401芯片,是因为此时手上没有带该芯片的开发板。不过演示功能的配置及代码基本一样。】

我使用CubeMx对TIM3进行配置,参考配置如下:

开启TIM3基于更新事件的DMA传输功能并做相关配置。

配置完成,生成初始化工程,添加用户代码。

我准备了3串脉冲的ARR/CCR1的值,分别以数组PulseData1[]、PulseData2[]、PulseData3[]来存放,占空比都设置为50%。显然数组行中间的0值用于前面提到过的预留字,此处无实际作用。另外,每个数组中的第6行数据其实是关闭当前通道PWM输出,具体应用时注意结合所选择的PWM模式及极性选择。

-

CW32使用DMA单通道、定时器触发ADC实现了多路AD采集2024-05-24 1781

-

STM32通过DMA方式传输TIM3定时器计数值,数值重复是为什么?2024-04-10 1006

-

定时器设计实现2023-11-08 1777

-

使用MM32F0270 定时器DMA方式输出PWM2023-10-17 2037

-

TIMx“DMA Burst Feature”如何通过SPI触发多个DMA请求?2023-02-07 523

-

运用 DMA 功能实现高级定时器和 ADC 的同步触发采样2022-06-06 1306

-

stm32 定时器触发ADC多通道采样+DMA提取数据2021-12-16 2038

-

STM32F103定时器触发ADC+DMA传输2021-11-30 2043

-

STM32CUBEMX配置教程(十二)STM32的定时器触发的固定频率ADC采样(使用DMA)2021-11-24 2626

-

测试代码中使用DMA传输,定时器触发ADC2020-08-10 5457

-

STM32定时器BURST传输介绍及示例2020-05-14 13884

-

STM32定时器触发DMA数据传输失败的原因如何解决2018-11-25 23273

-

STM32F030的定时器PWM使用设置与ADC的dma代码2016-03-21 3283

全部0条评论

快来发表一下你的评论吧 !