被ISSCC接收的Digital to Time Converter是如何设计的?

电子说

描述

工作原理

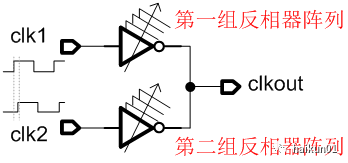

下图给出了反相器相位插指器的基本结构。结构很简单,两个反相器阵列输入分别接两个时钟,输出直接短接在一起,数字信号控制反相器阵列选通的数目。

两个反相器阵列输出短接,输入接不同相位的时钟,即构成了相位插值器

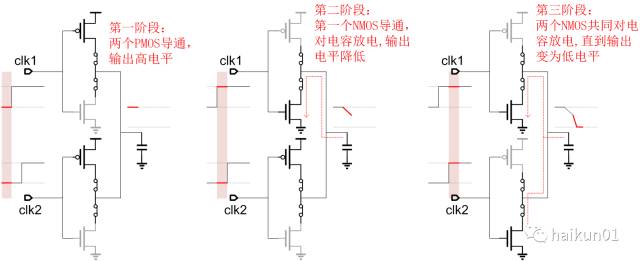

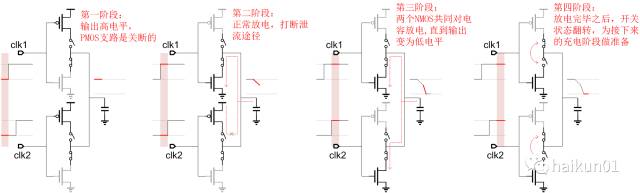

下面我们来看输入时钟上升沿来临时的情况(下降沿的情况类似)。在时钟上升沿来临之前,所有的PMOS导通,NMOS关断,输出为高电平(下图第一阶段)。接下来,第一个时钟clk1的上升沿先来临,第一组反相器阵列的NMOS导通,开始对输出节点的电容放电,输出电平逐步将小(下图第二阶段)。一直到第二个时钟clk2的上升沿到来,第二组反相器阵列的NMOS也导通,一起对输出节点的电容放电,直到输出电平变为低电平(下图第三阶段)。最终得到的输出电压波形可以使用分段直线来近似。

相位插值器工作原理,利用两个阶段不同的充放电速度来实现相位插值

那么我们怎么改变输出的相位呢?

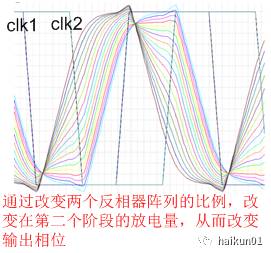

很简单, 改变两组反相器阵列使能的数目即可改变输出相位 。当第一组反相器阵列数目多,那么在第一个放电阶段放掉的电荷多,最终输出波形的相位靠前;当第一组反相器阵列数目少,则第一个放电阶段放掉的电荷少,输出波形的相位靠后。最终得到的不同输出波形如下图所示。

从上面对反相器相位插值器工作原理的描述,很容易得知设计反相器相位插值器的几个关键点:

1)相位插值器输出相位的调节范围等于两个输入时钟的相位差;

2)相位插指器的输出波形上升/下降沿不能太陡峭。

设想这一种情况,在第二个时钟上升沿到来之前,第一组反相器阵列的NMOS已经把输出电压放电放到低电平,第二组反相器阵列的NMOS无电可放,输出的相位与第二个时钟无关,那也就不能相位插值了。

3)当两个输入时钟间隔越近,相位插值器的性能越好。

一般而言,我们要求反相器阵列输出的上升时间和下降时间大于两个输入时钟的间隔。较小的间隔意味着可以取较短的上升时间/下降时间,也意味着jitter和功耗表现好。这也是为什么这篇论文在多模分频器MMD之后,又插入了一级可调延时器,产生22.5度的时钟间隔。

4) 还有一点比较隐晦,不太容易得出:对于反相器相位插值器,输入时钟的边沿越陡峭越好。

存在的问题

基于反相器的相位插值器主要有两点问题:

1)工作频率范围有限。 前面已经讲到,反相器阵列的输出上升下降时间需要大于输入时钟的间隔。对于一定的角度,频率变低时,相应的时间间隔变大,本来合适的上升下降时间变得相对较快,导致线性度变差。 若想要在各个频率下都保证较好的线性度,则需要针对频率对反相器的速度进行校准。 这又是件麻烦事。

不同工作频率下的线性度

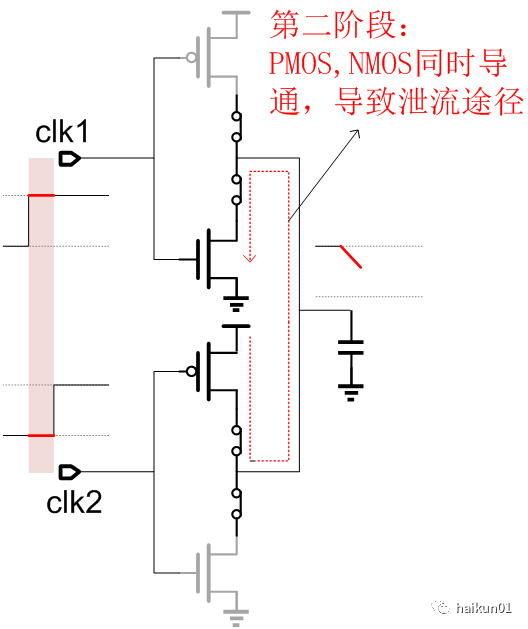

2)从之前的图可以看出, 在两个时钟上升沿之间的这一段时间,第一个反相器阵列的NMOS打开,第二个反相器阵列的PMOS打开,这样实际上形成了一条从电源到地的通路。 这是我们不想要的,这会消耗不必要的电流,同时也使线性度变差。下一部分我们会看到这篇论文是怎么解决这个问题的,以及付出的代价。

论文中改进的相位插值器

上面讲到,PMOS的导通导致了电流泄露。既然这样, 那么最直接的解决思路:我把PMOS这个通路关断不就行了么? 这篇论文的确是这样做的。一般反相器的使能开关同时导通或关断PMOS和NMOS支路,在这里被分开了。在放电过程中,只导通NMOS支路,从而掐断了泄流路径(下图第二阶段)。

现在放电阶段没问题了,那充电阶段呢? 如果使能开关保持不变,那PMOS通路一直被关断,等时钟下降沿到来之后也没有办法充电。 因此,这篇论文在这里加了一个反馈: 检测输出电平,当放电完毕后,通过反馈使得两路的使能信号翻转,把NMOS支路关断,PMOS支路打开 (下图第四阶段)。预先为充电阶段做好准备,待时钟下降沿一到就可以开始充电了。

在放电时,只打开NMOS支路,充电完成后通过反馈翻转开关状态。通过精细控制开关,在不影响插值功能的情况下掐断了泄流通路

从上面的图可以看出, 在第二个上升沿到第一个下降沿这一段时间内,输出节点是悬空的。这样有两个问题,一是晶体管的漏电会导致输出节点电平变化,二是悬空的节点更容易受到噪声的影响。 因此,这篇论文里又加入了一些电平保持单元,在放电和充电之间使能,用于保持输出电平。

总结起来,这篇论文的解题方法是: 精细控制反相器的NMOS和PMOS支路,而不是传统反相器相位插值器里的同开同关。 具体实施上,将一个时钟周期分成了四份,在充电时,只打开PMOS支路,充电完成后通过反馈翻转开关状态;放电情况类似。

付出的代价

下面来讲讲这种解决方案付出的代价。

首先,开关的控制变得很复杂,不合适高频。 从上面的原理描述我们可以知道, 在一个时钟周期内,开关的状态要翻转数次,反馈环路需要快速稳定下来,这对速度提出了很高的要求。 而在传统设计中,开关本身的速度可以远慢于时钟速度的。此论文工作频率为2GHz,相对于它使用的28nm工艺相对较低,因此它使用这种方法还能得到一些好处。如果工作在14GHz或者28GHz,我猜好处会变得极其有限,甚至得不偿失。

其次,版图会变得比较复杂。 开关有速度要求,因此开关的控制逻辑和反相器本身不能分隔太远,否则寄生电容大,开关无法在半个时钟周期内翻转并稳定。整个开关和反相器阵列耦合在一起,将会导致版图变得复杂。在2GHz处额外的寄生效应不明显,到了更高频时,寄生效应会变得很关键。

原论文中的版图布局较复杂

-

D某某

2024-06-27

0 回复 举报请问原论文的标题叫啥 收起回复

D某某

2024-06-27

0 回复 举报请问原论文的标题叫啥 收起回复

-

请问Time-to-Digital converter的作用是什么?2024-12-30 578

-

Analog-to-Digital Converter(模数转换器)的使用2022-02-17 1165

-

求大神分享ISSCC. 2004的PPT文件2021-06-22 1501

-

UG-1630: Evaluating the AD9146 Dual, 16-Bit, 1230 MSPS, TxDAC+® Digital-to-Analog Converter2021-01-29 1010

-

AD9286: 8-Bit, 500 MSPS, 1.8 V Analog-to-Digital Converter (ADC) Data Sheet2021-01-28 1797

-

AD6649BCPZ&a/d converter2020-10-09 660

-

TMS320x281x_DSP_Analog-to-Digital_Converter(ADC)Reference_Guide2016-01-19 861

-

Configuring the MAX35101 Time-to-Digital Converter as an Ultrasonic Water Meter2015-10-02 1852

-

MAX1425 10-bit, analog-to-digital converter2011-08-03 687

-

Time-to-Digital-Converter应用指南2010-09-14 519

-

Analog-to-Digital Converter Gr2010-06-01 626

-

什么是ADC (Analog to Digital Conv2010-02-22 817

-

Digital Control Concepts For P2009-11-28 652

全部0条评论

快来发表一下你的评论吧 !