九种简易MOS管开关电路图

应用电子电路

描述

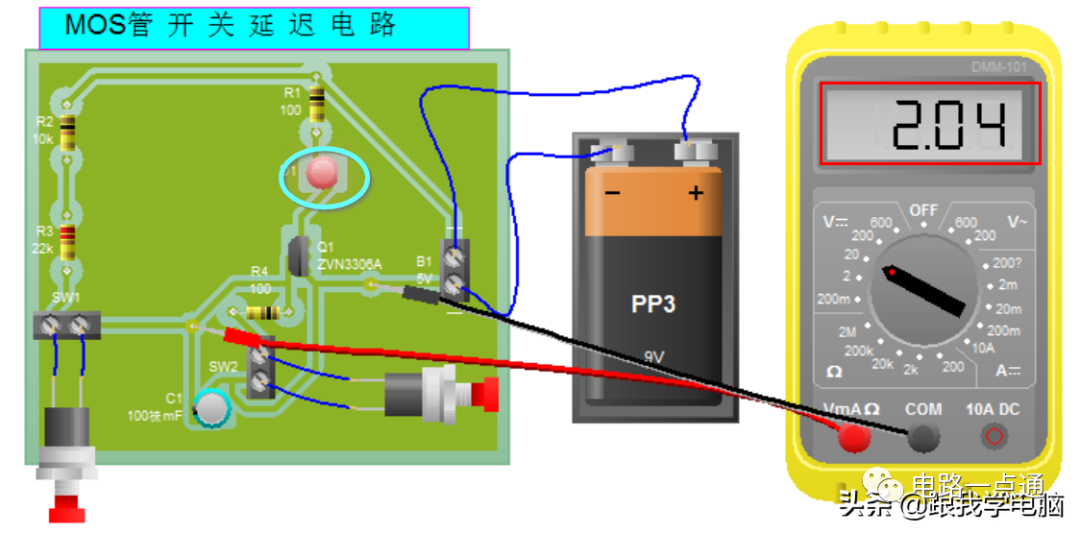

MOS管开关延迟电路讲解达到多少V才能导通

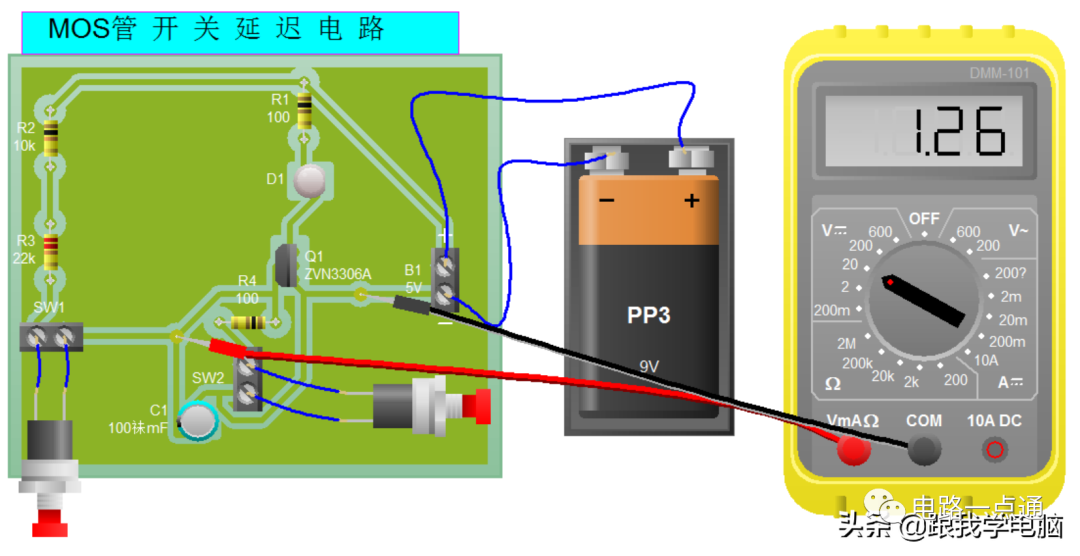

1.本电路由1颗MOS管、4只电阻、发光二极管、电池组成,电路非常简单.

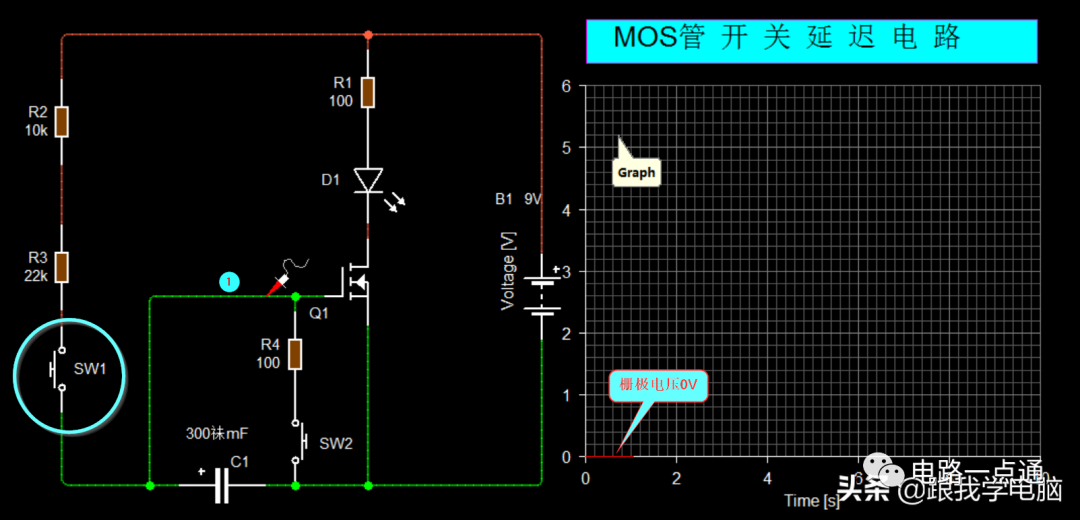

2.当SW1没有按下去的时候Q1栅极电压为0V,Q1为截止状态。

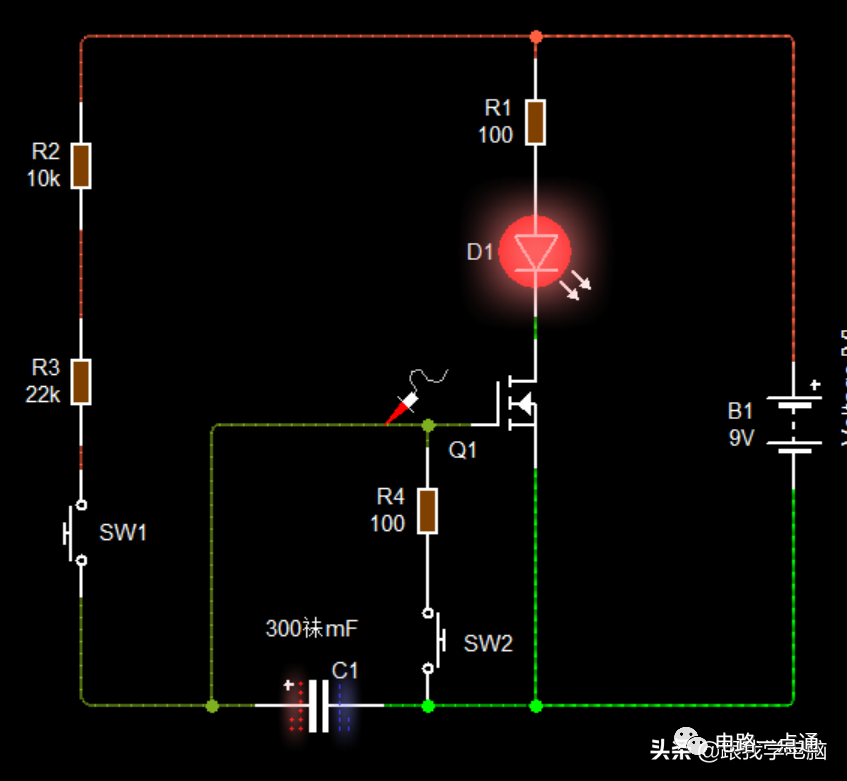

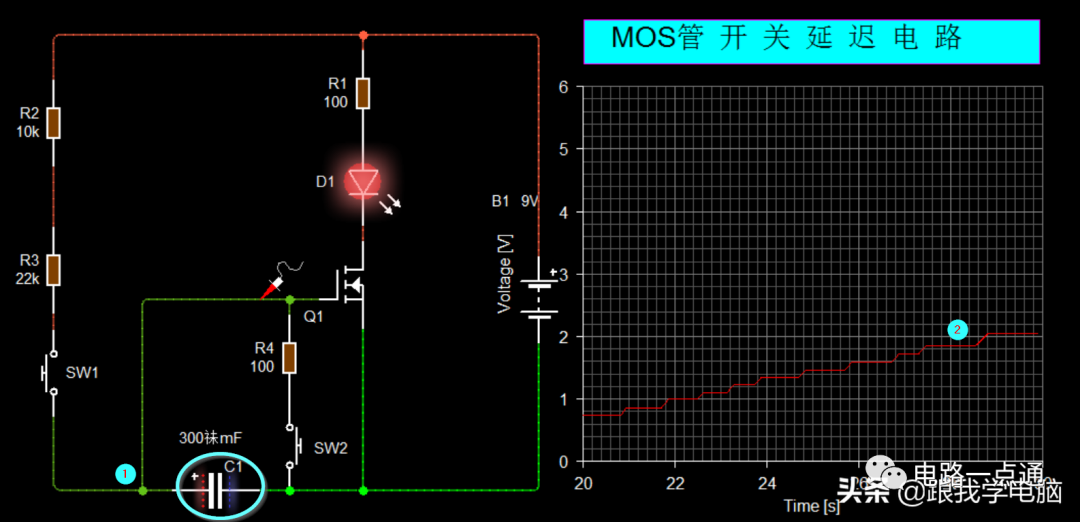

3.当开启电压达到MOS管开启电压后MOS才能打开,DS之间才能导通D1二极管才能点亮,电路中有一颗关键的元器件C1电容,当按下SW1时电压开始给C1充电,只有当电容充到2V以上的时候Q1才会导通,导通之后按下SW2就会熄灭。

4.通过下图可以看出电压达到2.04V时Q1才开始慢慢导通,如果持续性按下SW1时间越长,C1上的电压越高,Q2导通力越强,这样发光二极管就会越亮。

九种简易mos管开关电路图

第一种:mos管开关电路图

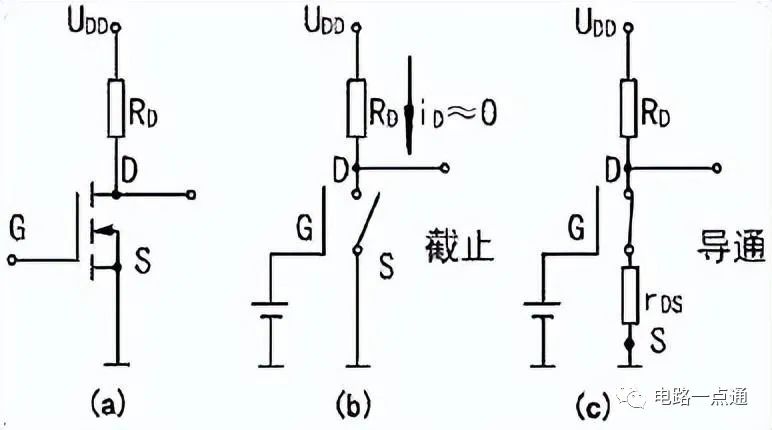

MOS管的开关特性

静态特性 MOS管作为开关元件,同样是工作在截止或导通两种状态。由于MOS管是电压控制元件,所以主要由栅源电压uGS决定其工作状态。 工作特性如下: ※uGS<开启电压UT:MOS管工作在截止区,漏源电流iDS基本为0,输出电压uDS≈UDD,MOS管处于“断开”状态,其等效电路如下图所示。

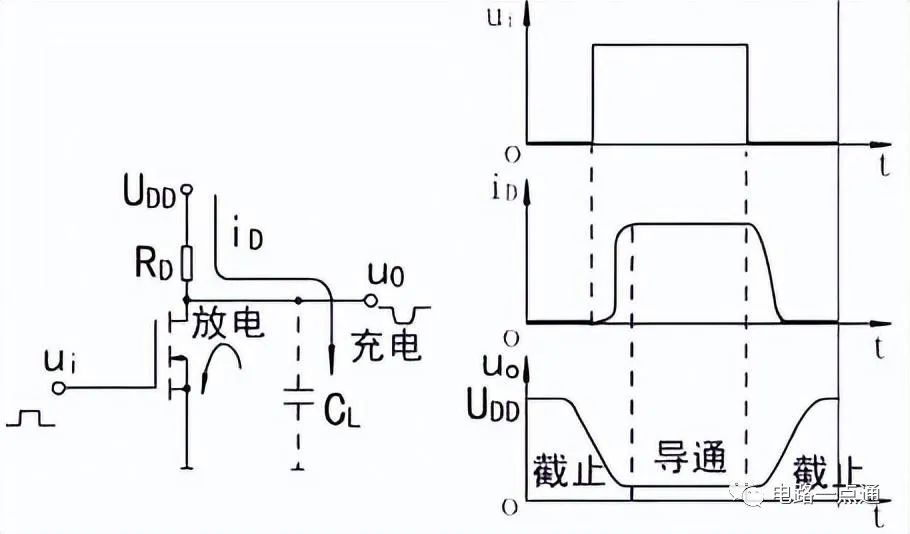

※ uGS>开启电压UT:MOS管工作在导通区,漏源电流iDS=UDD/(RD+rDS)。其中,rDS为MOS管导通时的漏源电阻。输出电压UDS=UDD·rDS/(RD+rDS),如果rDS《RD,则uDS≈0V,MOS管处于“接通”状态,其等效电路如上图(c)所示。 动态特性 MOS管在导通与截止两种状态发生转换时同样存在过渡过程,但其动态特性主要取决于与电路有关的杂散电容充、放电所需的时间,而管子本身导通和截止时电荷积累和消散的时间是很小的。下图 (a)和(b)分别给出了一个NMOS管组成的电路及其动态特性示意图。

(NMOS管动态特性示意图)

当输入电压ui由高变低,MOS管由导通状态转换为截止状态时,电源UDD通过RD向杂散电容CL充电,充电时间常数τ1=RDCL.所以,输出电压uo要通过一定延时才由低电平变为高电平;当输入电压ui由低变高,MOS管由截止状态转换为导通状态时,杂散电容CL上的电荷通过rDS进行放电,其放电时间常数τ2≈rDSCL.可见,输出电压Uo也要经过一定延时才能转变成低电平。但因为rDS比RD小得多,所以,由截止到导通的转换时间比由导通到截止的转换时间要短。 由于MOS管导通时的漏源电阻rDS比晶体三极管的饱和电阻rCES要大得多,漏极外接电阻RD也比晶体管集电极电阻RC大,所以,MOS管的充、放电时间较长,使MOS管的开关速度比晶体三极管的开关速度低。不过,在CMOS电路中,由于充电电路和放电电路都是低阻电路,因此,其充、放电过程都比较快,从而使CMOS电路有较高的开关速度。

MOS管导通特性

导通的意思是作为开关,相当于开关闭合。 NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以了。 PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS.

MOS开关管损失

不管是NMOS还是PMOS,导通后都有导通电阻存在,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗。选择导通电阻小的MOS管会减小导通损耗。现在的小功率MOS管导通电阻一般在几十毫欧左右,几毫欧的也有。 MOS在导通和截止的时候,一定不是在瞬间完成的。MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失。通常开关损失比导通损失大得多,而且开关频率越快,损失也越大。 导通瞬间电压和电流的乘积很大,造成的损失也就很大。缩短开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数。这两种办法都可以减小开关损失。

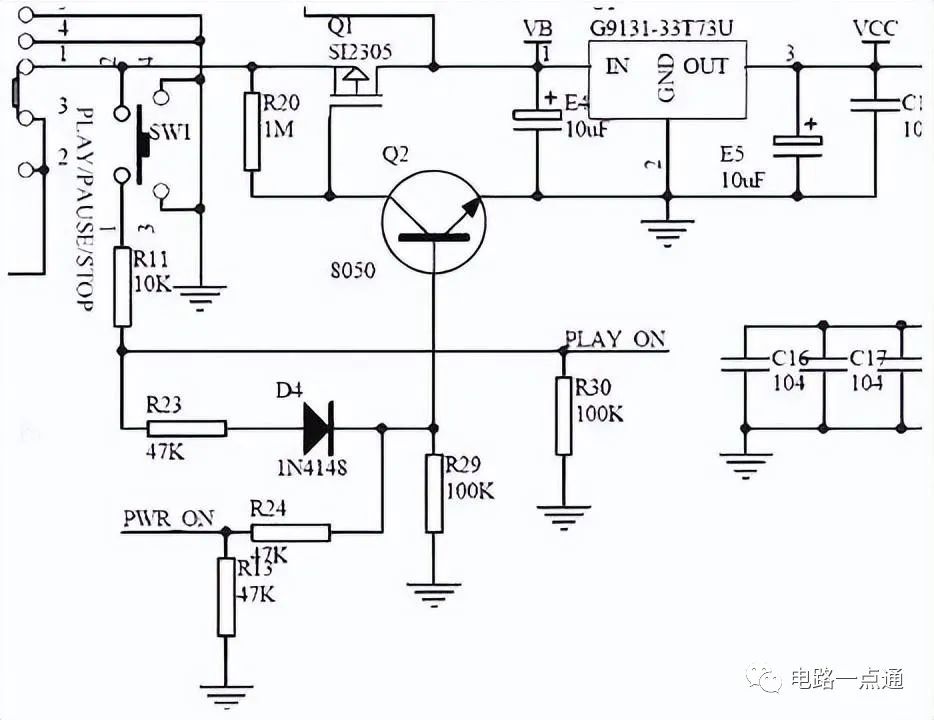

第二种:mos管开关电路图

图中电池的正电通过开关S1接到场效应管Q1的2脚源极,由于Q1是一个P沟道管,它的1脚栅极通过R20电阻提供一个正电位电压,所以不能通电,电压不能继续通过,3v稳压IC输入脚得不到电压所以就不能工作不开机!这时,如果我们按下SW1开机按键时,正电通过按键、R11、R23、D4加到三极管Q2的基极,三极管Q2的基极得到一个正电位,三极管导通(前面讲到三极管的时候已经讲过),由于三极管的发射极直接接地,三极管Q2导通就相当于Q1的栅极直接接地,加在它上面的通过R20电阻的电压就直接入了地,Q1的栅极就从高电位变为低电位,Q1导通电就从Q1同过加到3v稳压IC的输入脚,3v稳压IC就是那个U1输出3v的工作电压vcc供给主控,主控通过复位清0,读取固件程序检测等一系列动作,输处一个控制电压到PWR_ON再通过R24、R13分压送到Q2的基极,保持Q2一直处于导通状态,即使你松开开机键断开Q1的基极电压,这时候有主控送来的控制电压保持着,Q2也就一直能够处于导通状态,Q1就能源源不断的给3v稳压IC提供工作电压!SW1还同时通过R11、R30两个电阻的分压,给主控PLAYON脚送去时间长短、次数不同的控制信号,主控通过固件鉴别是播放、暂停、开机、关机而输出不同的结果给相应的控制点,以达到不同的工作状态!

第三种:mos管开关电路图

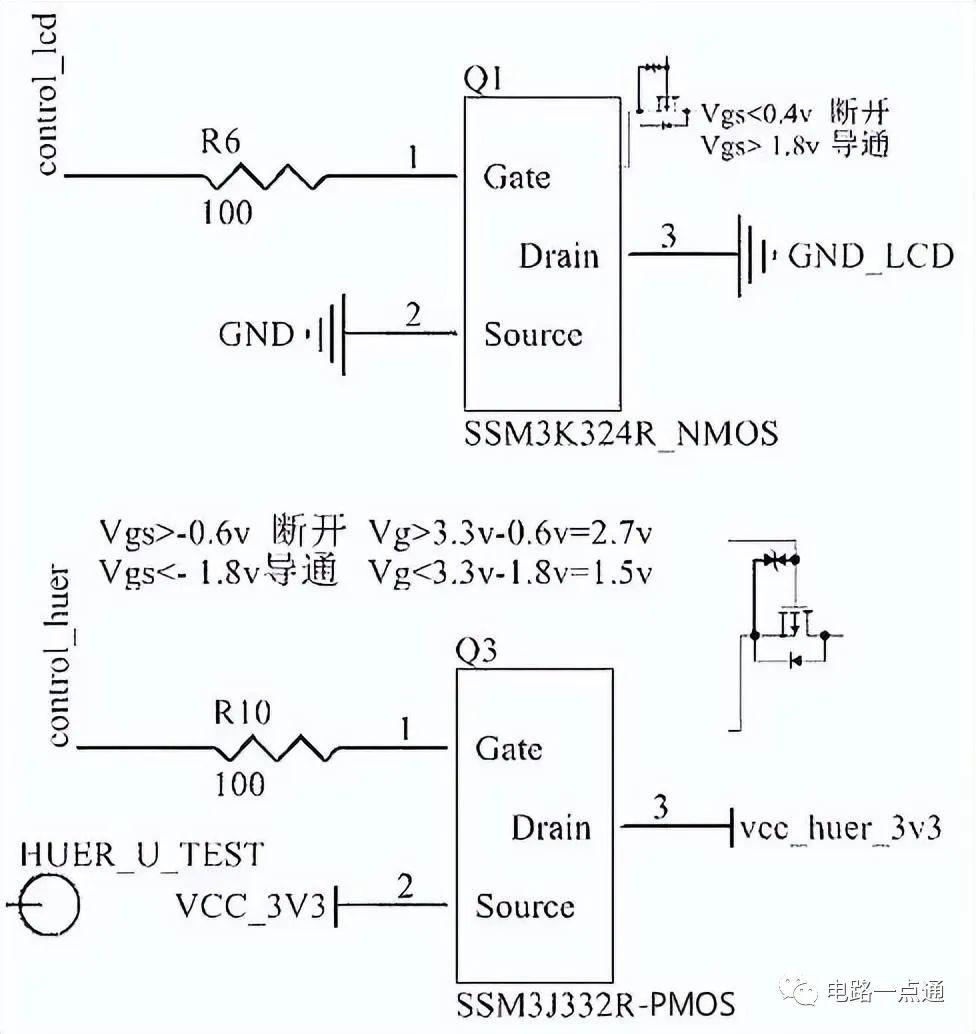

下图是两种MOS管的典型应用:其中第一种NMOS管为高电平导通,低电平截断,Drain端接后面电路的接地端;第二种为PMOS管典型开关电路,为高电平断开,低电平导通,Drain端接后面电路的VCC端。

第四种:mos管开关电路图

驱动电路加速MOS管关断时间

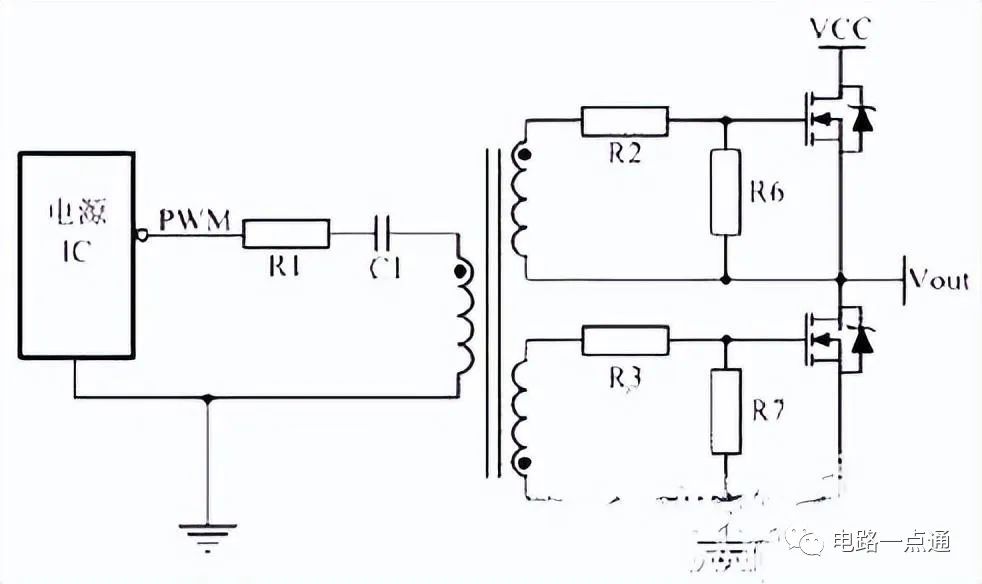

图5 隔离驱动 为了满足如图5所示高端MOS管的驱动,经常会采用变压器驱动,有时为了满足安全隔离也使用变压器驱动。其中R1目的是抑制PCB板上寄生的电感与C1形成LC振荡,C1的目的是隔开直流,通过交流,同时也能防止磁芯饱和。

第五种:mos管开关电路图

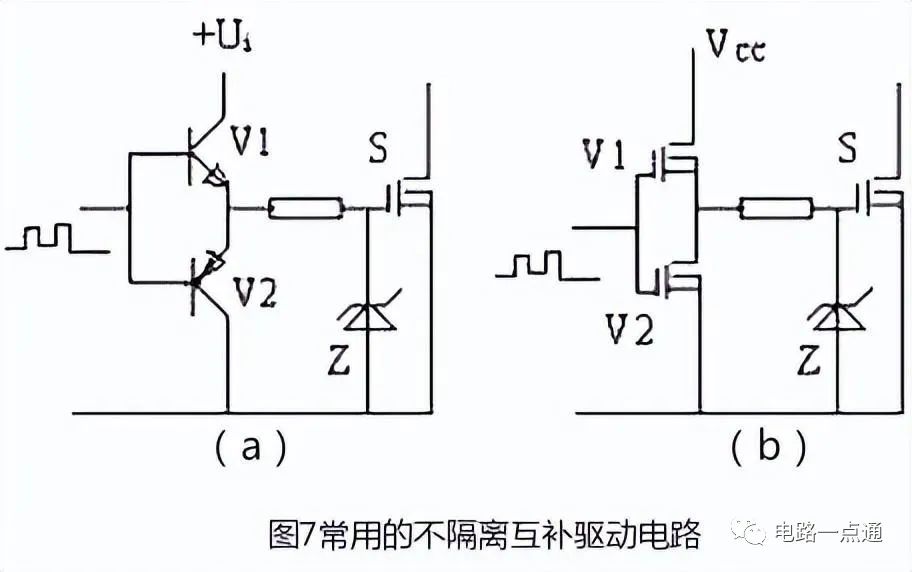

图7(a)为常用的小功率驱动电路,简单可靠成本低。适用于不要求隔离的小功率开关设备。图7(b)所示驱动电路开关速度很快,驱动能力强,为防止两个MOSFET管直通,通常串接一个0.5~1Ω小电阻用于限流,该电路适用于不要求隔离的中功率开关设备。这两种电路特点是结构简单。

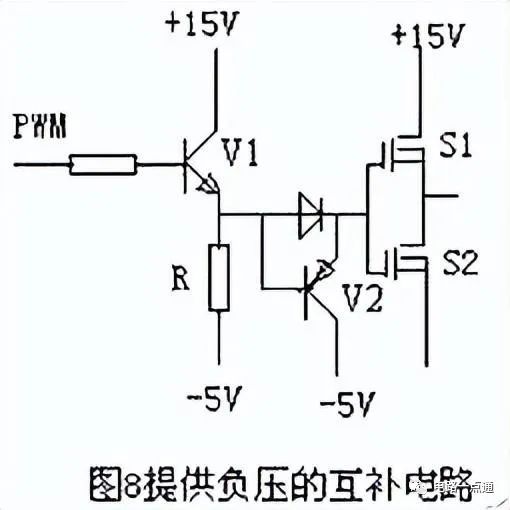

功率MOSFET属于电压型控制器件,只要栅极和源极之间施加的电压超过其阀值电压就会导通。由于MOSFET存在结电容,关断时其漏源两端电压的突然上升将会通过结电容在栅源两端产生干扰电压。常用的互补驱动电路的关断回路阻抗小,关断速度较快,但它不能提供负压,故抗干扰性较差。为了提高电路的抗干扰性,可在此种驱动电路的基础上增加一级有V1、V2、R组成的电路,产生一个负压,电路原理图如图8所示。

当V1导通时,V2关断,两个MOSFET中的上管的栅、源极放电,下管的栅、源极充电,即上管关断,下管导通,则被驱动的功率管关断;反之V1关断时,V2导通,上管导通,下管关断,使驱动的管子导通。因为上下两个管子的栅、源极通过不同的回路充放电,包含有V2的回路,由于V2会不断退出饱和直至关断,所以对于S1而言导通比关断要慢,对于S2而言导通比关断要快,所以两管发热程度也不完全一样,S1比S2发热严重。 该驱动电路的缺点是需要双电源,且由于R的取值不能过大,否则会使V1深度饱和,影响关断速度,所以R上会有一定的损耗。

第六种:mos管开关电路图

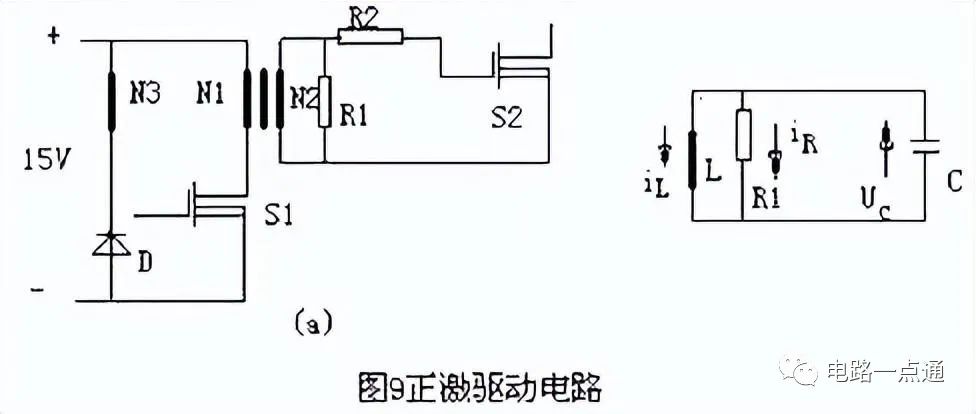

正激式驱动电路

电路原理如图9(a)所示,N3为去磁绕组,S2为所驱动的功率管。R2为防止功率管栅极、源极端电压振荡的一个阻尼电阻。因不要求漏感较小,且从速度方面考虑,一般R2较小,故在分析中忽略不计。

其等效电路图如图9(b)所示脉冲不要求的副边并联一电阻R1,它做为正激变换器的假负载,用于消除关断期间输出电压发生振荡而误导通。同时它还可以作为功率MOSFET关断时的能量泄放回路。该驱动电路的导通速度主要与被驱动的S2栅极、源极等效输入电容的大小、S1的驱动信号的速度以及S1所能提供的电流大小有关。由仿真及分析可知,占空比D越小、R1越大、L越大,磁化电流越小,U1值越小,关断速度越慢。该电路具有以下优点:①电路结构简单可靠,实现了隔离驱动。②只需单电源即可提供导通时的正、关断时负压。③占空比固定时,通过合理的参数设计,此驱动电路也具有较快的开关速度。 该电路存在的缺点:一是由于隔离变压器副边需要噎嗝假负载防振荡,故电路损耗较大;二是当占空比变化时关断速度变化较大。脉宽较窄时,由于是储存的能量减少导致MOSFET栅极的关断速度变慢。

第七种:mos管开关电路图

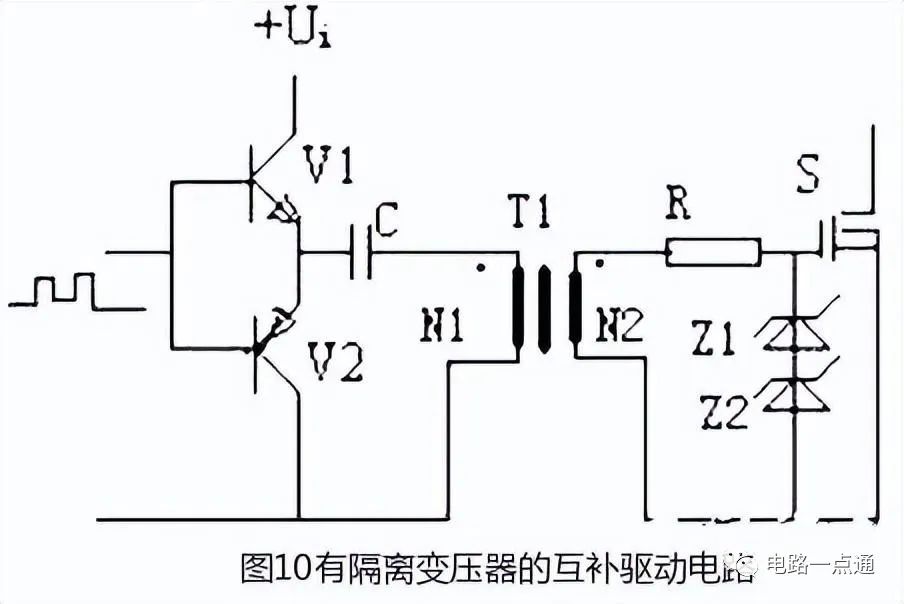

有隔离变压器的互补驱动电路

如图10所示,V1、V2为互补工作,电容C起隔离直流的作用,T1为高频、高磁率的磁环或磁罐。

导通时隔离变压器上的电压为(1-D)Ui、关断时为DUi,若主功率管S可靠导通电压为12V,而隔离变压器原副边匝比N1/N2为12/[(1-D)Ui]。为保证导通期间GS电压稳定C值可稍取大些。该电路具有以下优点: ①电路结构简单可靠,具有电气隔离作用。当脉宽变化时,驱动的关断能力不会随着变化。 ②该电路只需一个电源,即为单电源工作。隔直电容C的作用可以在关断所驱动的管子时提供一个负压,从而加速了功率管的关断,且有较高的抗干扰能力。 但该电路存在的一个较大缺点是输出电压的幅值会随着占空比的变化而变化。当D较小时,负向电压小,该电路的抗干扰性变差,且正向电压较高,应该注意使其幅值不超过MOSFET栅极的允许电压。当D大于0.5时驱动电压正向电压小于其负向电压,此时应该注意使其负电压值不超过MOAFET栅极允许电压。所以该电路比较适用于占空比固定或占空比变化范围不大以及占空比小于0.5的场合。

第八种:mos管开关电路图

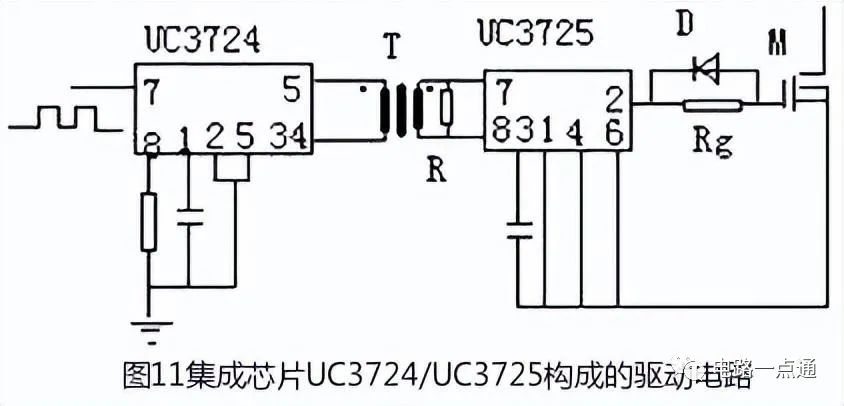

集成芯片UC3724/3725构成的驱动电路

电路构成如图11所示。其中UC3724用来产生高频载波信号,载波频率由电容CT和电阻RT决定。一般载波频率小于600kHz,4脚和6脚两端产生高频调制波,经高频小磁环变压器隔离后送到UC3725芯片7、8两脚经UC3725进行调制后得到驱动信号,UC3725内部有一肖特基整流桥同时将7、8脚的高频调制波整流成一直流电压供驱动所需功率。一般来说载波频率越高驱动延时越小,但太高抗干扰变差;隔离变压器磁化电感越大磁化电流越小,UC3724发热越少,但太大使匝数增多导致寄生参数影响变大,同样会使抗干扰能力降低。 根据实验数据得出: 对于开关频率小于100kHz的信号一般取(400~500)kHz载波频率较好,变压器选用较高磁导如5K、7K等高频环形磁芯,其原边磁化电感小于约1毫亨左右为好。这种驱动电路仅适合于信号频率小于100kHz的场合,因信号频率相对载波频率太高的话,相对延时太多,且所需驱动功率增大,UC3724和UC3725芯片发热温升较高,故100kHz以上开关频率仅对较小极电容的MOSFET才可以。对于1kVA左右开关频率小于100kHz的场合,它是一种良好的驱动电路。该电路具有以下特点:单电源工作,控制信号与驱动实现隔离,结构简单尺寸较小,尤其适用于占空比变化不确定或信号频率也变化的场合。

第九种:mos管开关电路图

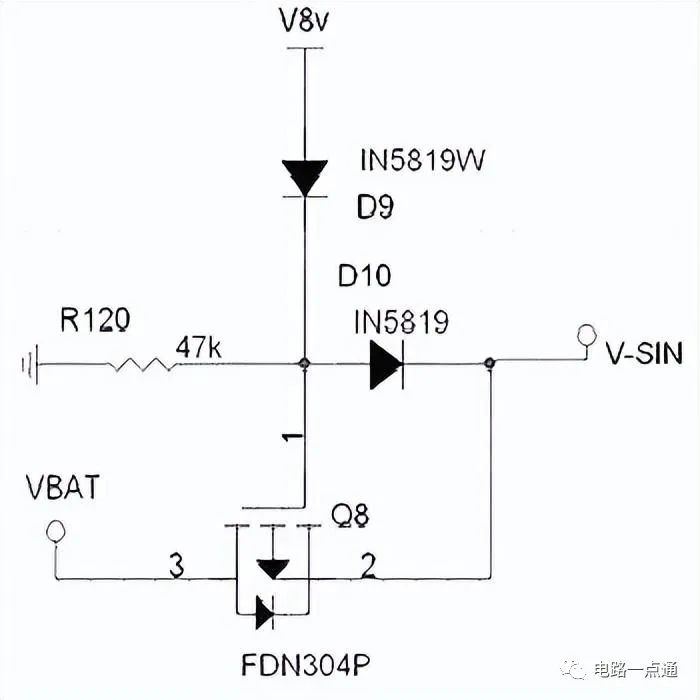

第一种应用,由PMOS来进行电压的选择,当V8V存在时,此时电压全部由V8V提供,将PMOS关闭,VBAT不提供电压给VSIN,而当V8V为低时,VSIN由8V供电。注意R120的接地,该电阻能将栅极电压稳定地拉低,确保PMOS的正常开启,这也是前文所描述的栅极高阻抗所带来的状态隐患。D9和D10的作用在于防止电压的倒灌。D9可以省略。这里要注意到实际上该电路的DS接反,这样由附生二极管导通导致了开关管的功能不能达到,实际应用要注意。

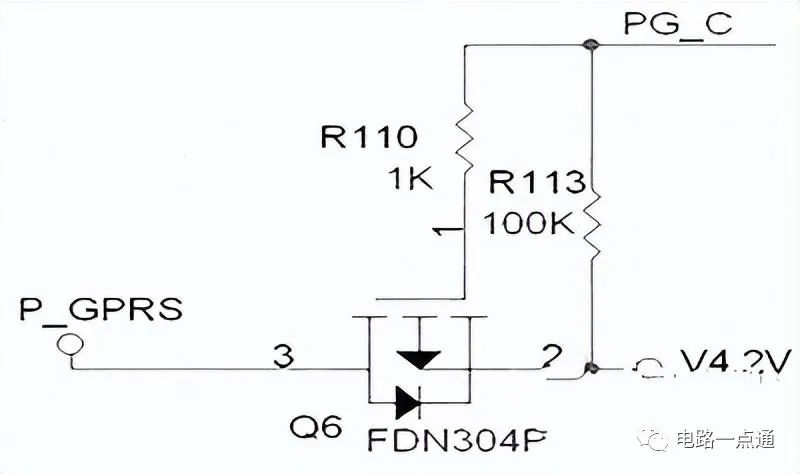

来看这个电路,控制信号PGC控制V4.2是否给P_GPRS供电。此电路中,源漏两端没有接反,R110与R113存在的意义在于R110控制栅极电流不至于过大,R113控制栅极的常态,将R113上拉为高,截至PMOS,同时也可以看作是对控制信号的上拉,当MCU内部管脚并没有上拉时,即输出为开漏时,并不能驱动PMOS关闭,此时,就需要外部电压给予的上拉,所以电阻R113起到了两个作用。R110可以更小,到100欧姆也可。

审核编辑:汤梓红

-

MOS管开关电路图 MOS管开关电路设计2023-07-20 4973

-

MOS管开关电路图分享2023-07-03 3735

-

MOS管开关电路原理图2023-06-20 5139

-

MOS场效应管电源开关电路2023-05-16 2727

-

MOS管开关电路的定义2021-10-29 2703

-

P型MOS管开关电路图资料推荐2021-10-28 3553

-

MOS管开关电路2021-10-22 2252

-

mos管开关电路图大全2021-06-16 3634

-

mos管开关电路图资料下载2021-04-28 1804

-

九种简易mos管开关电路图2019-06-19 155872

-

mos管开关电路_pwm驱动mos管开关电路图分享2018-01-04 63176

-

MOS管开关电路是什么?详解MOS管开关电路2017-05-17 132534

-

简易光控开关电路图2009-04-17 2932

全部0条评论

快来发表一下你的评论吧 !